### TECHNICAL MANUAL

# DIRECT SUPPORT AND GENERAL SUPPORT MAINTENANCE MANUAL

RADIO TEST SET GROUP 0Q-60/USQ-46

No. 11-6625 2578-34

# HEADQUARTERS DEPARTMENT OF THE ARMY WASHINGTON, D.C., 30 April 1923

# Direct Support and General Support Maintenance Manual RADIO TEST SET GROUP OQ-60/USQ-46

| LIST OF   | ILLUSTRATIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Page<br>iii                                                                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER   | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                              |

| Section ] | GENERAL 1-1 Scope 1-2 Mainter and Pornis and Records 1-3 Later and records of Agric Material to Pourage Enemit Use 1-4 Adit and start as the Start agric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-1<br>1-1<br>1-1<br>1-1<br>1-1                                                                                                                              |

| I         | I-O Brown in a of Eco grant in Main wal Improvements<br>· TOF CANCELPTON AND TOATA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                              |

|           | 1-7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 1 - 1<br>1-1                                                                                                                                                 |

| CHAPTER   | and the second and th |                                                                                                                                                              |

| Section 1 | 2-1 ( ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( ) ( )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2-1<br>2-1                                                                                                                                                   |

| -         | [ ANN A COST REAL TERRING, AND NONRECTRRING INTEGRATED CIRCUITS  2-3 Generals  2-4 Symbology and Terminology of Recurring Elements of Integrated Circuits  2-5 Symbology and Terminology of Complete Integrated Circuits                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 2-3<br>2-3<br>2-4                                                                                                                                            |

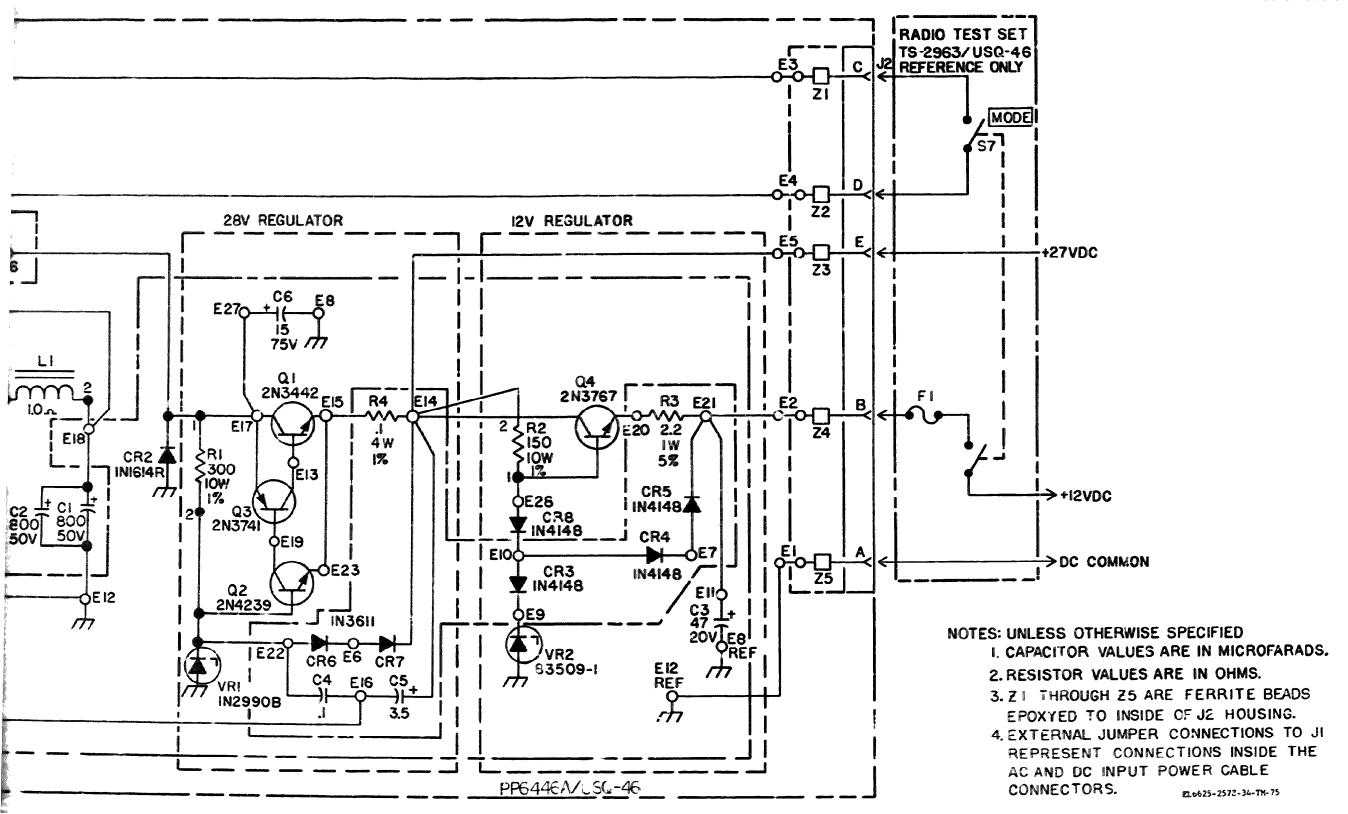

| 1         | I. GFRERA! ECRETIONS  2-6 Cherrer all  2-7 Programm Cerreration  2-8 Mondulation Sie course and Control Section  2-9 Frequencing Suntherizor Section  2-10 RF Amplifier Betweener Campus Section  2-11 Power Supply Regulator Section 1 AIAIT  2-12 Freque Pages Assembly 1 AIAIT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-6<br>2-6<br>2-11<br>2-12<br>2-14<br>2-15<br>2-16                                                                                                           |

| ľ         | 7. IDET AUGUD FUNCTIONING OF TEST SIT MODULES 2-13 Cemeral 2-14 Radio Test Set Data Word Structure 3-15 Mossi per Types 2-16 Addines Codes 2-17 WCNO DADAD 2-18 Detector Output DADAD 2-19 Deop Filter WCO DADAD 2-20 Spribesize                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2-18<br>2-19<br>2-19<br>2-20<br>2-22<br>2-23<br>2-25<br>2-26<br>2-27<br>2-29<br>2-31<br>2-33<br>2-34<br>2-35<br>2-36<br>2-37<br>2-38<br>2-38<br>2-39<br>2-39 |

|           | · •••                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | i                                                                                                                                                            |

| CHADTED | 2     | DIFECT SUPPORT MAINTENANCE                                                                                                                                | Page         |

|---------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|

| CHAPTER |       |                                                                                                                                                           |              |

| Section | Ι.    | GENERAL                                                                                                                                                   | 3 - 1        |

|         |       |                                                                                                                                                           | 3-1          |

|         |       | 3-3. Trouble shooting Data                                                                                                                                | 3-1          |

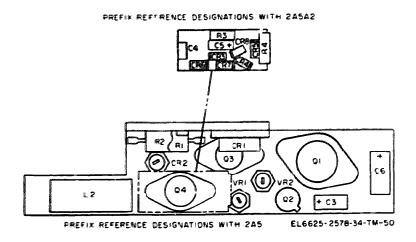

|         |       | 3-4. Component Location Illustrations                                                                                                                     | 3-2          |

|         |       | 3-5. Voltage and Resustance Measurements                                                                                                                  | 3-2          |

|         |       | 3-6. Waveform Analysis                                                                                                                                    | 3-6          |

|         | 11.   | TOOLS AND EQUIPMENT                                                                                                                                       |              |

|         |       | 3-7. Tools, Waterials, and Equipment 3-8. Fibrication of Extender Cubbs                                                                                   | 3-16<br>3-16 |

|         | III.  | DIRECT SUPPORT TROUBLESHOOTING OF THE TEST SET                                                                                                            |              |

|         |       |                                                                                                                                                           | 3-17         |

|         |       | 3-10. Troubleshooting Chart                                                                                                                               | 3-17         |

|         | IV.   | DIRECT SUPPORT REMOVAL AND REPLACEMENT OF TEST SET COMPONENTS                                                                                             |              |

|         |       | 3-11. General                                                                                                                                             | 3-18         |

|         |       | 3-12. Removal or Replacement of Power Supply PP-6116A USQ-16                                                                                              | 3-18         |

|         |       | 3-13. Removal or Peplacement of Center Housing 1.4.2                                                                                                      | 3-18         |

|         |       | 3-14. Removal or the placement of Front Panel Assembly 1A1 118                                                                                            | 3-19         |

|         |       | 3-15. Removal or Replacement of Front Panel Assembly 1A1A18 Environmental Casket                                                                          | 3-19         |

|         |       | 3-16. Removal or Replacement of Kniobs for CHANNEL, MODE, MESSAGE, FSK, PROGRAM and METER Switches and Controls LEVEL SET and LEVEL DEV                   | 3-21         |

|         |       | 3-17. Removal of Replacement of CHANNEL, PROGRAM, MODE, FSK, METER and MESSAGE                                                                            |              |

|         |       | Switches IAI 119-51 through S-10                                                                                                                          | 3-21         |

|         |       | 3-18. Removal or Replacement of Fuse Holder 1 VIA18 XF1                                                                                                   | 3-21<br>3-21 |

|         |       | 3-19. Removal or Replacement of Cabb. Assembly IAIAI8W1 3-20. Removal or Replacement of Connector Dust Cap.                                               | 3-21         |

|         |       | 3-21. Removal or Replacement of Front Panel Assembly Connectors 1A1A18-Jf,                                                                                | 3-22         |

|         |       | 12 I s and - I t                                                                                                                                          | 3-22         |

|         |       | 3-22. Removal or Replacement of Front Panel Assembly START Switch 1A1A18-S11 and uts Wa-                                                                  | 2 22         |

|         |       | terseal Boot                                                                                                                                              | 3-22<br>3-22 |

|         |       | 3-23. Removal or Replacement of Vittenuator IAIAIS ATI Boot 3-24. Removal or Replacement of Plug-F: Modules IAINI through INIAIS on Front Panel Module    | 3-22         |

|         |       | Module Assembly 1.41                                                                                                                                      | 3-22         |

|         |       |                                                                                                                                                           | 3-24         |

|         |       | 3-20. Removal or Realizement of Power Summly Regulator Assembly 131417                                                                                    | 3-24<br>3-24 |

|         |       | 3-27. Removal or Replacement of Connector 1A1P1 on Front Panel Module Assembly                                                                            | 3-24         |

|         |       | 3-28. Removal or Replacement of Center Housing Assembly 1A2 Environmental Gasket 3-29. Removal or Replacement of Connector Assembly 1A2A2 on Center " ong |              |

|         |       | Assembly 1A2                                                                                                                                              | 3-24         |

|         | V.    | TEST SFT DIRECT SUPPORT TEST PROCEDURES                                                                                                                   |              |

|         |       | 3-30. (leneral                                                                                                                                            | 3-25         |

|         |       | 3-31. References                                                                                                                                          | 3-26<br>3-26 |

|         |       | 3-32. Grand Band and Sync Pulse Triming Test Procedure 3-33. RF Output Cilibration Accuracy Test Procedure                                                | 3-20         |

|         |       | 3-34. Programmy Coverige and Vectories Test Procedure                                                                                                     | 3-32         |

|         |       | 3-35. Wessage Program Generation Test                                                                                                                     | 3-34         |

|         | VI.   | DIRECT SUPPORT TROUBLESHOOTING AND REPAIR OF THE POWER                                                                                                    |              |

|         |       | SUPPLY PP-6446A USO-46                                                                                                                                    | 2 27         |

|         |       | 3-36. Trouble-hooting and Repair 3-37. Resistance Data                                                                                                    | 3-37<br>3-37 |

|         |       | 3-38. V I tre Checks                                                                                                                                      | 3-37         |

|         |       | 3-39. Continuity Checks on Laput Power Cable                                                                                                              | 3-37         |

|         | VII.  | DIRECT SUPPORT REPAIR PROCEDURES FOR THE POWER SUPPLY                                                                                                     |              |

|         |       | PP 6116A TSQ-46                                                                                                                                           |              |

| •       | 7777  | 3-40. Repair Procedures                                                                                                                                   | 3-40         |

| \       | /III. | DIRECT SUPPORT REMOVAL OR REPLACEMENT OF POWER SUPPLY PARTS                                                                                               |              |

|         |       | 3-41. Removal or Replacement of Connector 12                                                                                                              | 3-40         |

|         |       | 3-42. Represal or Penth opent of Power Supply Corket                                                                                                      | 3-40         |

| СПУДТЕР               | 4. GENERAL SUFPORT MAINTENANCE                                                                                     | Page         |

|-----------------------|--------------------------------------------------------------------------------------------------------------------|--------------|

| Section               | I. NTRODUCTION                                                                                                     |              |

| Section               | 4-1. General                                                                                                       | 4 - 1        |

|                       | 4-2. Reference Data                                                                                                | 4-1          |

|                       | II. TOOLS, MATERIALS, AND TEST EQUIPMENT                                                                           |              |

| ,                     | 4-3. wis, Materials and Test Equipment                                                                             | 4-1          |

| J                     | II. JENERAL SUPPORT TROUBLESHOOTING OF TEST SET 4-4. Troubleshooting Chart                                         | 4 1          |

| ]                     | IV. GENERAL SUPPORT SYSTEM TESTS FOR TEST SET                                                                      | 4-1          |

|                       | 4-5. General                                                                                                       | 4-2          |

|                       | 4-6. RF Output System: Accuracy Measurement Test Procedure                                                         | 4-4          |

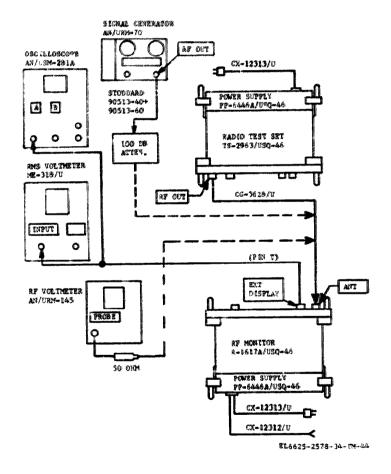

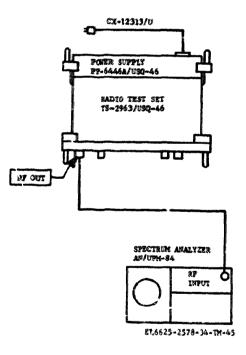

|                       | 4-7. Spurious Output Test Procedure 4-8. Deviation Measurement Test                                                | 4-7          |

|                       | 4-9. Current Brain Test                                                                                            | 4-9<br>4-13  |

|                       | 4-10. Keying Rate Measurement Test Procedure                                                                       | 4-15         |

|                       | V. GENFRAL SUPPORT REMOVAL AND REPLACEMENT OF TEST SET                                                             |              |

|                       | COMPONENTS 4-11. General                                                                                           | 4 17         |

|                       | 4-11. General 4-12. Removal or Replacement of Autonumber 1A1A18 AT1                                                | 4-17<br>4-17 |

|                       | 4-13. Removal or Rept. cement of Meter 1.41418-M1                                                                  | 4-17         |

|                       | 4-14. Relieval or Replacement of Variable Resistors 1A1A18 R1 or 1A1A18 R2                                         | 4-17         |

| ,                     | VI. GENERAL SUPPORT TROUBLESHOOTING OF POWER SUPPLY                                                                | 4.40         |

|                       | 4-15. General<br>4-16. Bef. rence Data                                                                             | 4-18<br>4-18 |

|                       | 4-17. Voltage and Resistance Chart                                                                                 | 4-18<br>4-18 |

| V                     | II. GENERAL SUPPORT POWER SUPPLY TEST PROCEDURES                                                                   | . 10         |

|                       | 4-18. De Mode Voltage Regulation Test Procedure                                                                    | 4-21         |

|                       | 4-19. Dr. Mode Carrent Drain Test Procedure                                                                        | 4-23<br>4-25 |

|                       | 4-20. Ac Mode Voltage Regulation Test Procedure 4-21. Ac Mode Current Drain Test Procedure                         | 4-23         |

| V                     | III. GENERAL SUPPORT REMOVAL OR REPLACEMENT OF POWER SUPPLY COMPONENTS                                             | 7-21         |

|                       | 4-22. <b>Ga mera</b> l                                                                                             | 4-29         |

|                       | 4-23. Removal or Replacement of Transformer 2T1                                                                    | 4-29<br>4-29 |

|                       | 4-24. Removal or Replacement of Choke 21.1<br>4-25. Removal or Replacement of Capacitors 2C1 and 2C2               | 4-29         |

|                       | 4-26. Removal or Replacement of Connector Assembly Ji                                                              | 4-29         |

|                       | 4-27. Removal or Replacement of Fusc Holders for F1, F2 and F3                                                     | 4-30         |

|                       | 4-28. Remarks or Replacement of Component Plate Assembly 245 4-29. Removed or Replacement of Component Board 2A542 | 4-30<br>4-30 |

|                       |                                                                                                                    | 4-30         |

| CHAPTER               | 5. DEPOT REPAIR AND OVERHAUL                                                                                       | 5-1          |

|                       | 5-1. General                                                                                                       | 3-1          |

|                       | 6. FINAL ILLUSTRATIONS                                                                                             | - 4          |

|                       | 6-1. General                                                                                                       | 6-1<br>6-1   |

| ALPHABET              | 6-2. Wurung Diagram Color Codes<br>ICAL INDEX                                                                      | I-1          |

|                       | 1021                                                                                                               |              |

|                       | LIST OF ILLUSTRATIONS                                                                                              |              |

| Figure<br>No.<br>2-1. | Title                                                                                                              | Page 2-2     |

| 2-1.                  | Radio Test Set Basic Block Diagram                                                                                 | 2-2<br>2-3   |

| 2-2.<br>2-3.          | Integrated Circuit Pin Arrangements                                                                                | 2-3<br>2-4   |

| 2-3.<br>2-4.          | Integrated Circuit Logic Symbols Integrated Circuits Logic Diagram                                                 | 2-5          |

| 2-5.                  | Mode Control I. Simplified Block Diagram                                                                           | 2-6          |

| 2-6.                  | Mode Control II. Simplified Block Diagram                                                                          | 2-7<br>2-8   |

| 2-7.<br>2-8.          | Word Length Generator, Simplified Block Diagram                                                                    | 2-8<br>2-9   |

| 2-6.<br>2-9.          | Mode Control III. Simplified Block Diagram  Encoder I. Simplified Block Diagram                                    | 2-9          |

| 2-10.                 | Encoder Matrix, Simplified Block Diagram                                                                           | 2-10         |

| 2-11.                 | Encoder II. Simplified Block Plagram                                                                               | 2-10<br>2-11 |

| 2-12.                 | Shift Register, Simplified Block Diagram                                                                           | 4-11         |

| Figure         | Title                                                                                                             | Page                 |

|----------------|-------------------------------------------------------------------------------------------------------------------|----------------------|

| No.<br>2-13.   |                                                                                                                   | 2-11                 |

| 2-13.<br>2-14. | NCXO Simplified Block Diagram  Refer to Constator Simplified Block Diagram                                        | 2-12                 |

| 2-15.          | Synthesizer Mrx r, Simplified Block Diagran.                                                                      | 2-13                 |

| 2-16.          | Programmable Develer, Simplified Block Diagram                                                                    | 2-14                 |

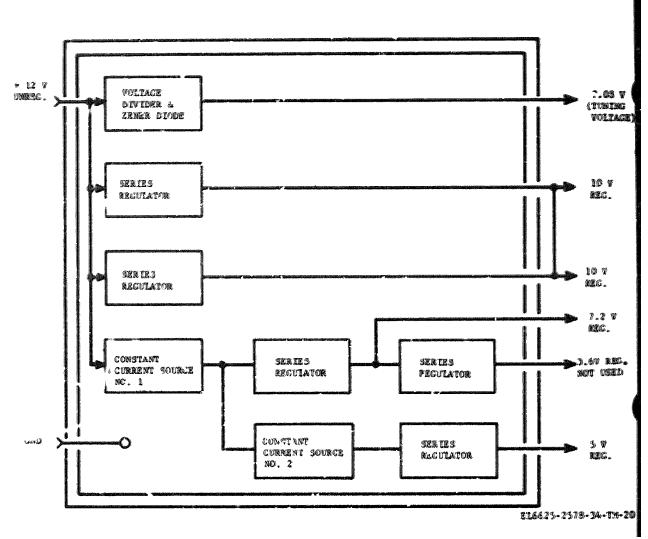

| 2-17.          | Loop Filter VCO, Simplified Block Diagram                                                                         | 2-15<br>2-16         |

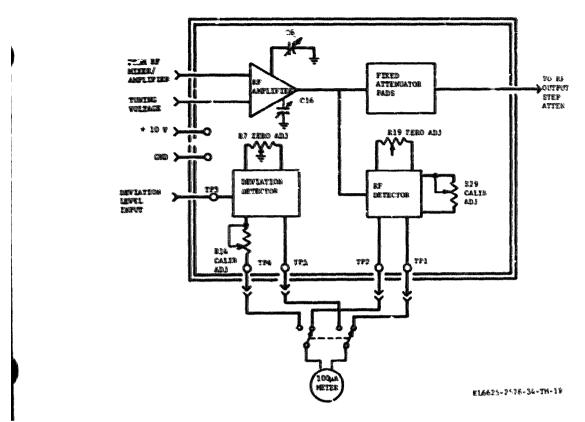

| 2-18.<br>2-19. | RE Wiver Amplifier, Simplified Block Diagram                                                                      | 2-16<br>2-17         |

| 2-17.          | Detector Output, Simplified Block Diagram                                                                         | 2-17                 |

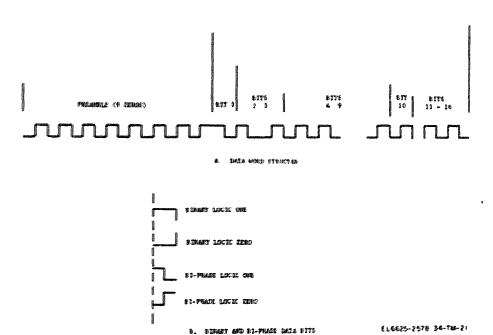

| 2-21.          | Power Supply Regulator, Simplified Block Diagram Typical Radio Set Pata Word                                      | 2-19                 |

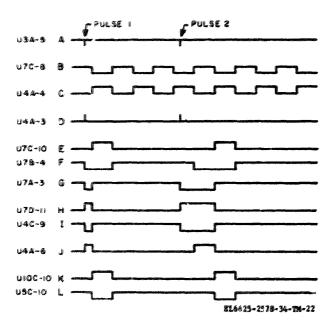

| 2-22.          | Reset Synchronizer Timing Diagram                                                                                 | 2-28                 |

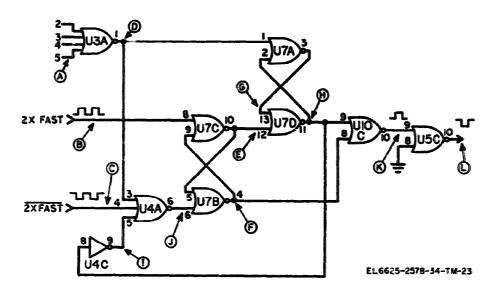

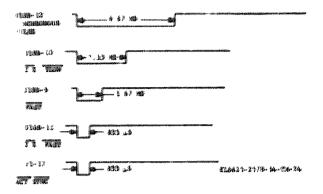

| 2-23.          | Reset Synchronizer Schematic                                                                                      | 2-28                 |

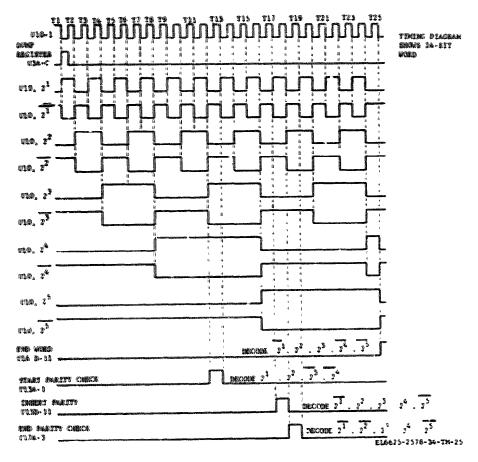

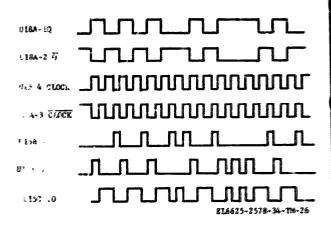

| 2-24.<br>2-25. | Clock Timing Diagram                                                                                              | 2-32<br>2-33         |

| 2-25.<br>2-26. | 21 Bit Word Timing Piagrani Manchester Encoder Data (Example)                                                     | 2-38                 |

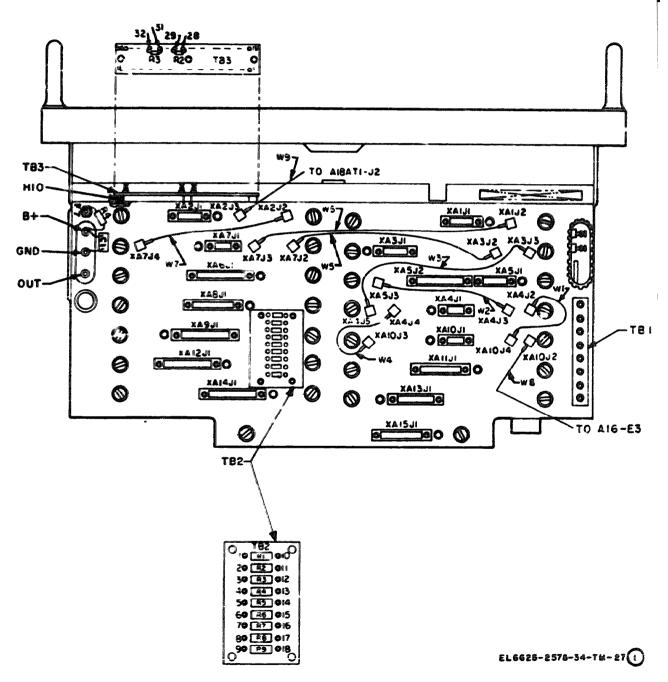

| 3-1.           | Test Set Front Penel Module Assembly Component Location Diagram                                                   | 3-2                  |

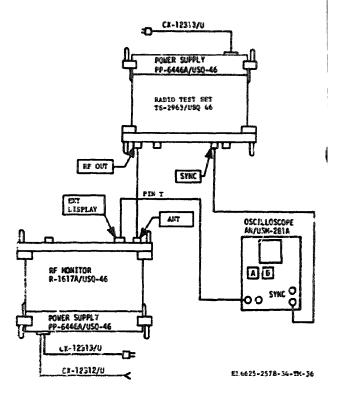

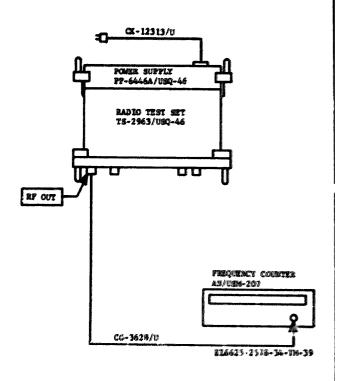

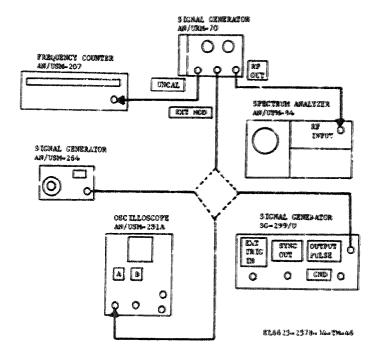

| 3-2.           | General Equipment Test Setup                                                                                      | 3-4                  |

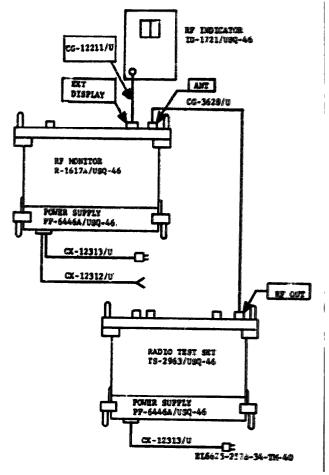

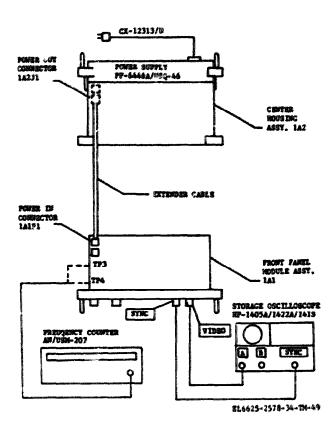

| 3-3.           | Voltage, Resistance and Waveform Troubleshooting Test Setup                                                       | 3-5                  |

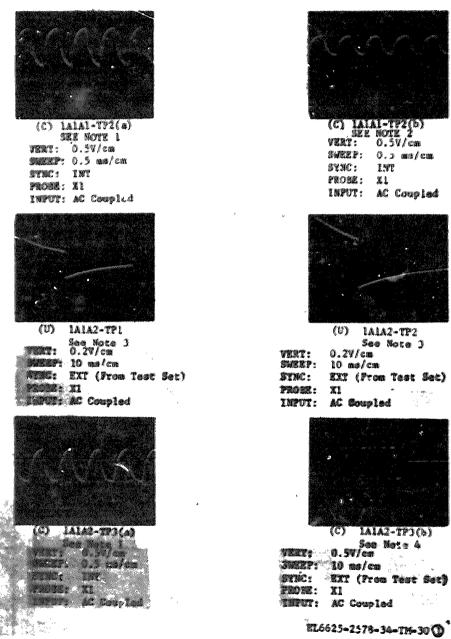

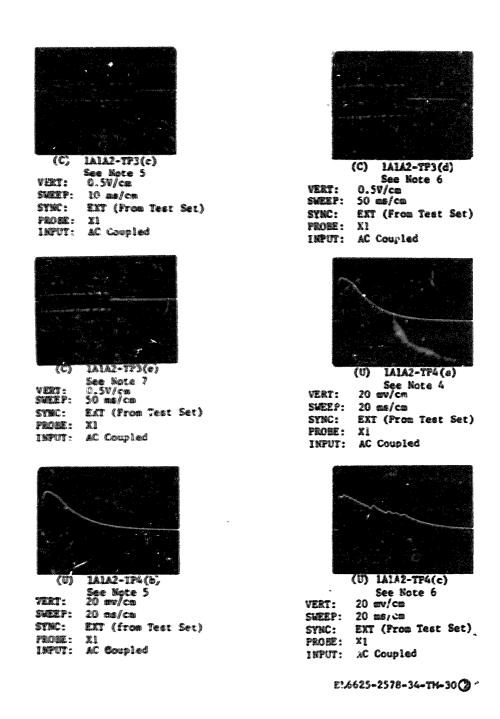

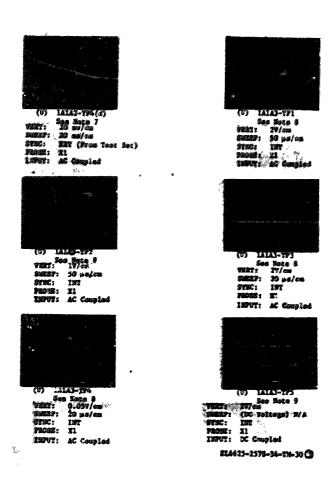

| 3-4.<br>3-5.   | To the Syrom Wave irema                                                                                           | 3-7<br>3-17          |

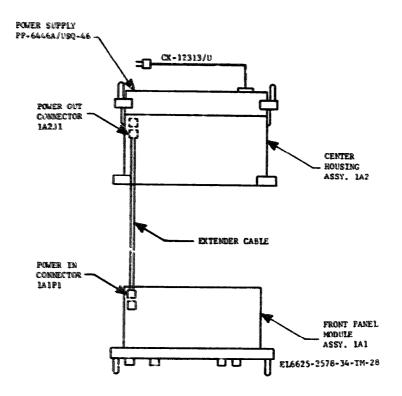

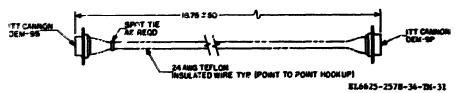

| 3-5.<br>3-6.   | Extender Cable Fabrica' on Diagram                                                                                | 3-19                 |

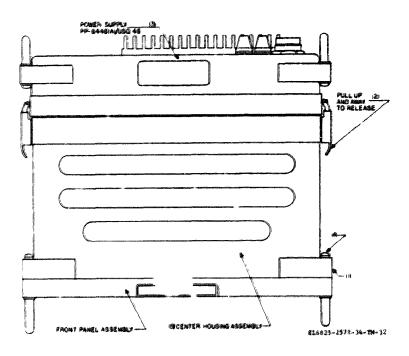

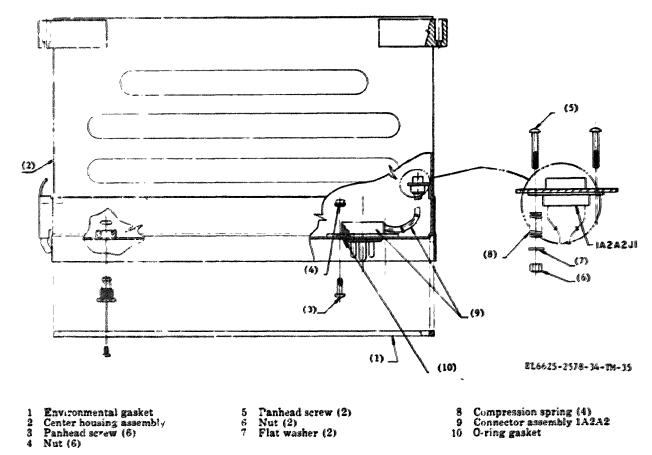

| 3-0.<br>3-7.   | Powert Supply and Center Housing Assembly 1A2, Removal or Replacement Front Panel Assembly 1 VIA18, Exploded View | 3-19                 |

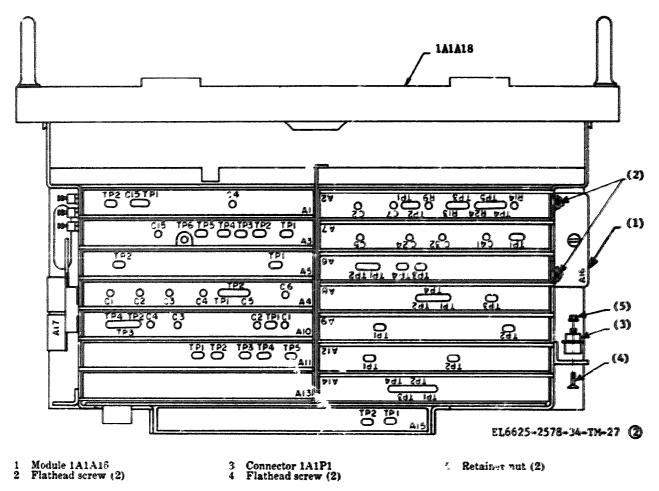

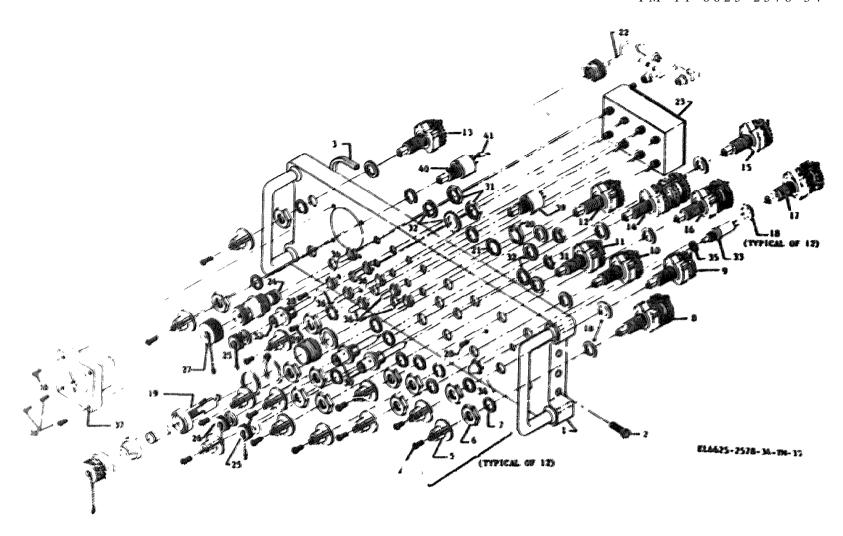

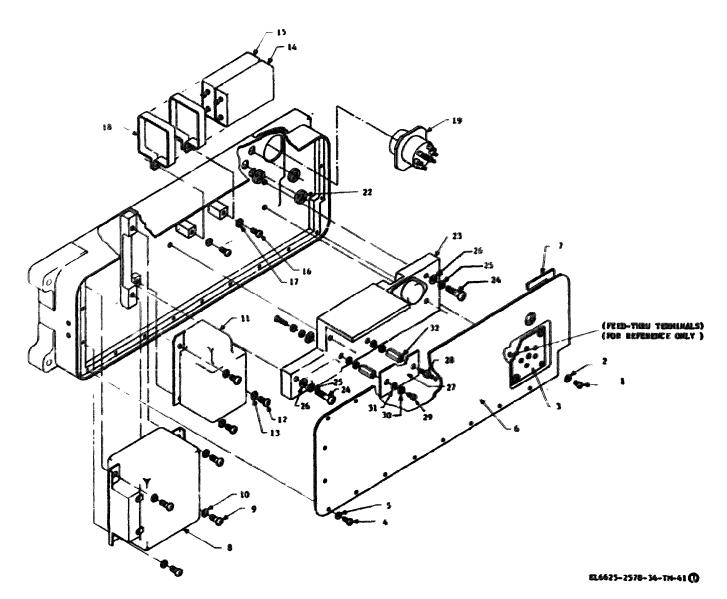

| 3-8.           | From Panel Module Assembly 1A1, Exploded View                                                                     | 3-23                 |

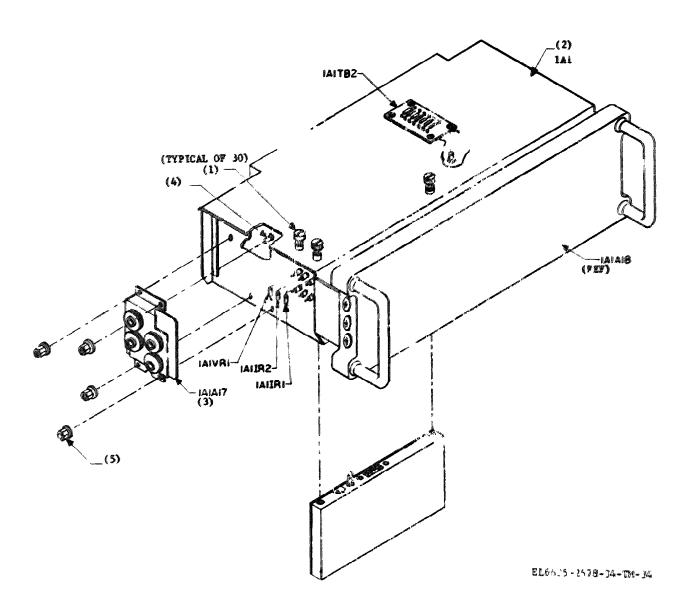

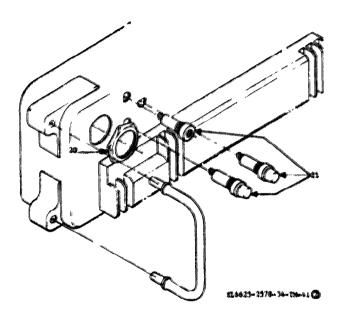

| 3-9.           | Center Hi sang Neembly 1A2, Exploded View                                                                         | 3-25                 |

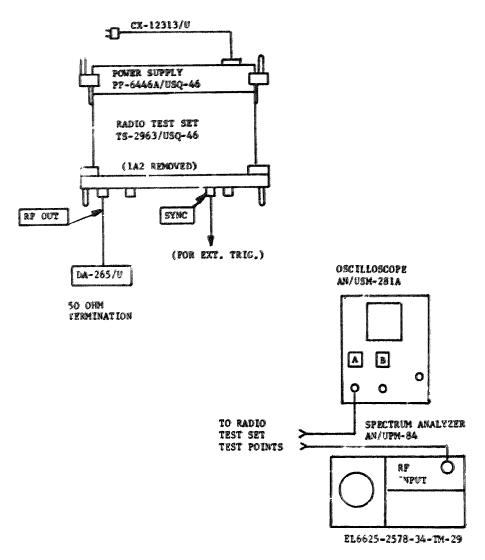

| 3-10.          | Guard Band and Sync Timing Test Setup                                                                             | 3-26<br>3-27         |

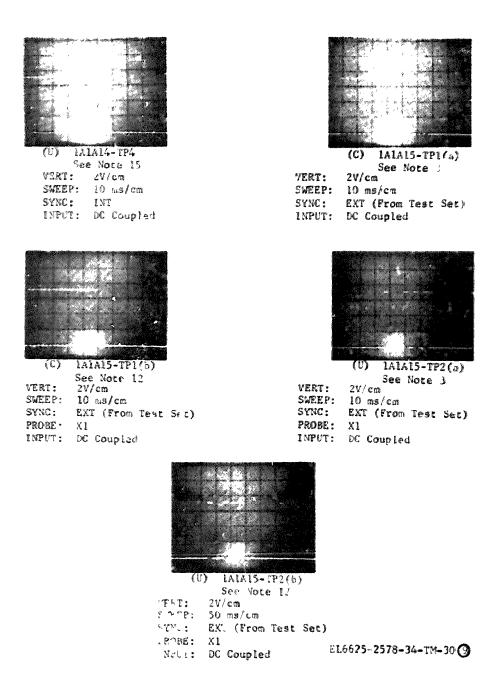

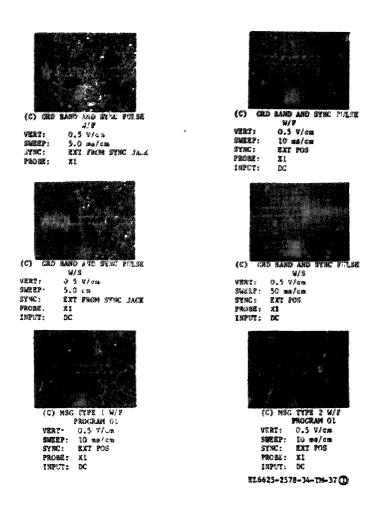

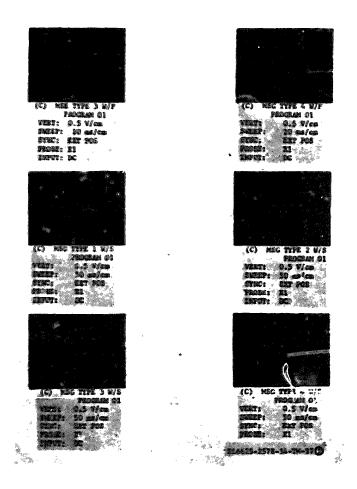

| 3-11.<br>3-12. | Percet Support Test Set System Waveforms                                                                          | 3-27<br>3-30         |

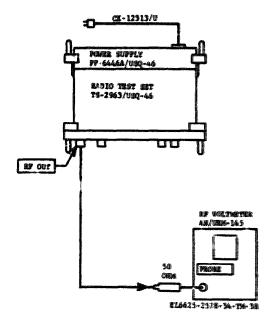

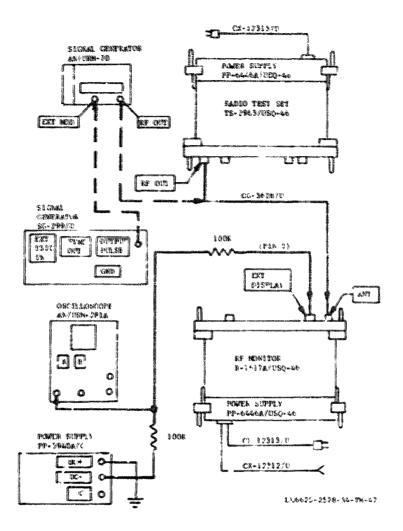

| 3-12.<br>3-13. | RF Output Calibration Accuracy Test Setup  Frequency Coverage and Accuracy Test Setup                             | 3-32                 |

| 3-14.          | Message Generation Test Setup                                                                                     | 3-34                 |

| 3-15.          | Power Supply PP-6116A USQ-46, Components Location                                                                 | 3-38                 |

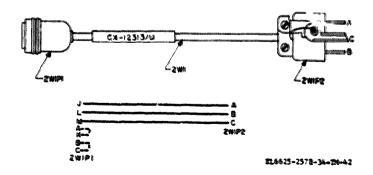

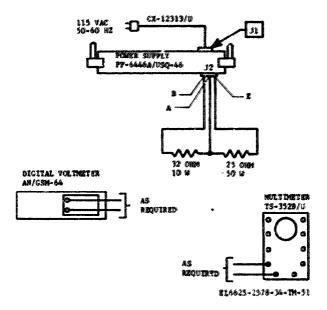

| 3-16.          | Power Supply AC Cable Assembly, CX-12313/U                                                                        | 3-39                 |

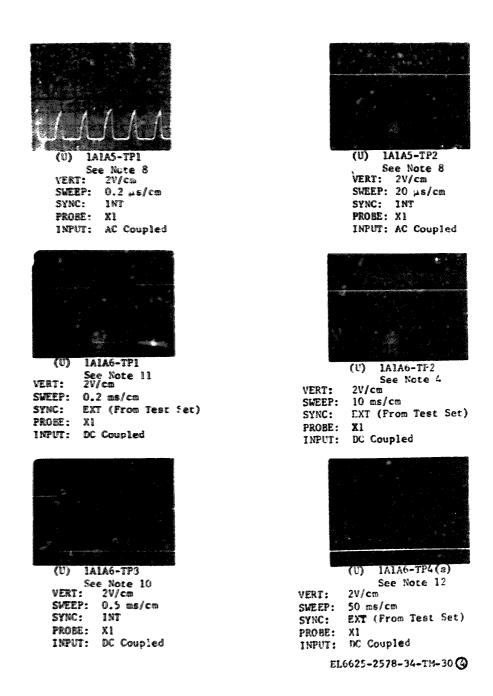

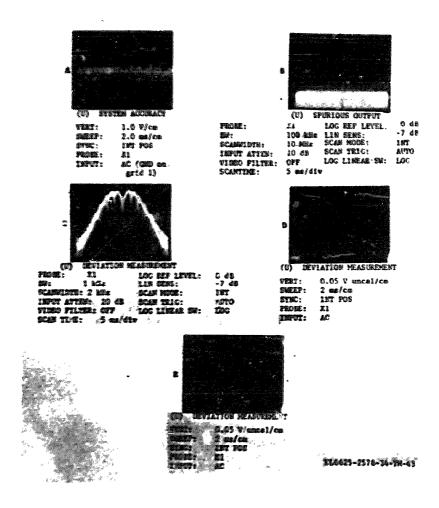

| 4-1.<br>4-2.   | General Support Test Set System Waveforms                                                                         | 4-3<br>4-4           |

| 4-3.           | RF Output System Accuracy Measurement Test Setup Spurious Output Test Setup                                       | 4-7                  |

| 4-4.           | Deviat on Test Equipment Calibration Test Setup                                                                   | 4-9                  |

| 4-5.           | Deviation Measurement Test Setup                                                                                  | 4-10<br>4-13         |

| 4-6.<br>4-7.   | Current Drain Test Setup                                                                                          | 4-13<br>4-15         |

| 4-7.<br>4-8.   | Keying Rate Measurement Test Setup                                                                                | 4-13                 |

| 4-9.           | Component Plate and Component Board Assembly Components Location Power Supply Troubleshooting Test Setup          | 4-19                 |

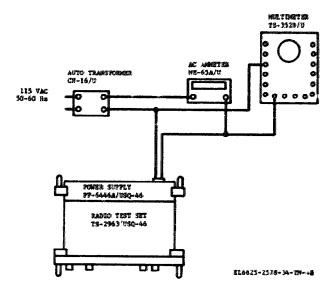

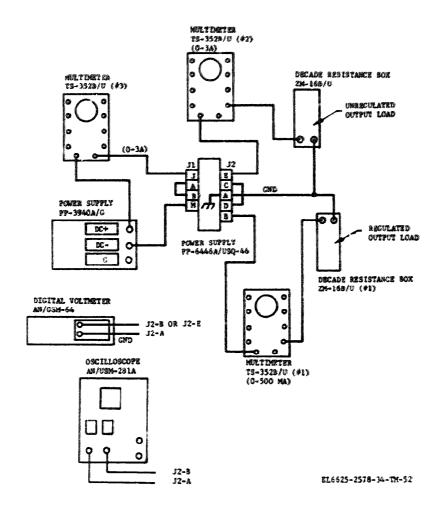

| 4-10.          | De Mode Voltage Regulation Test Setup                                                                             | 4-21                 |

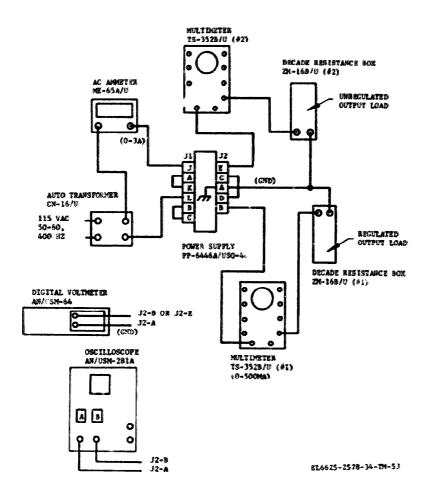

| 4-11.          | Ac Mode Voltage Regulation Test Setup                                                                             | 4-25                 |

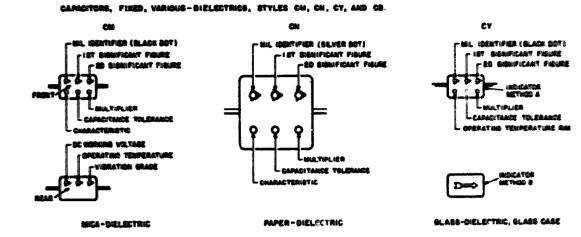

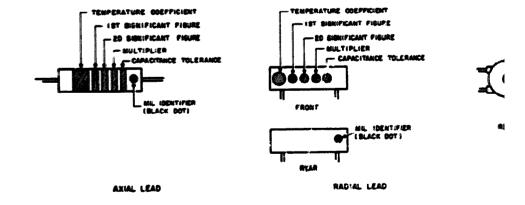

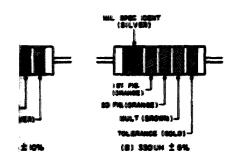

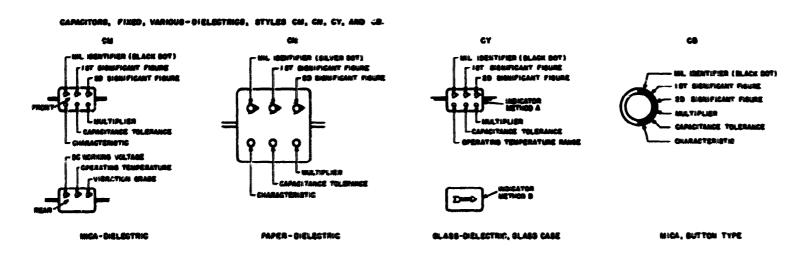

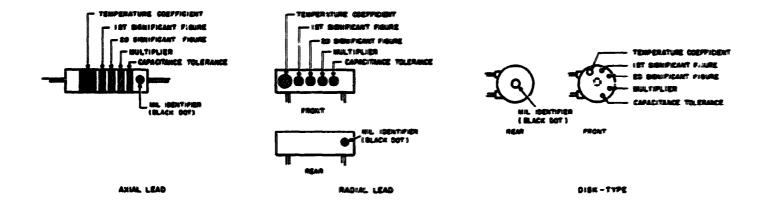

| 6-1.<br>6-2.   | Color Code Marking for MIL-STI Capacitors, Inductors, and Resistors                                               | Fold-out<br>Fold-out |

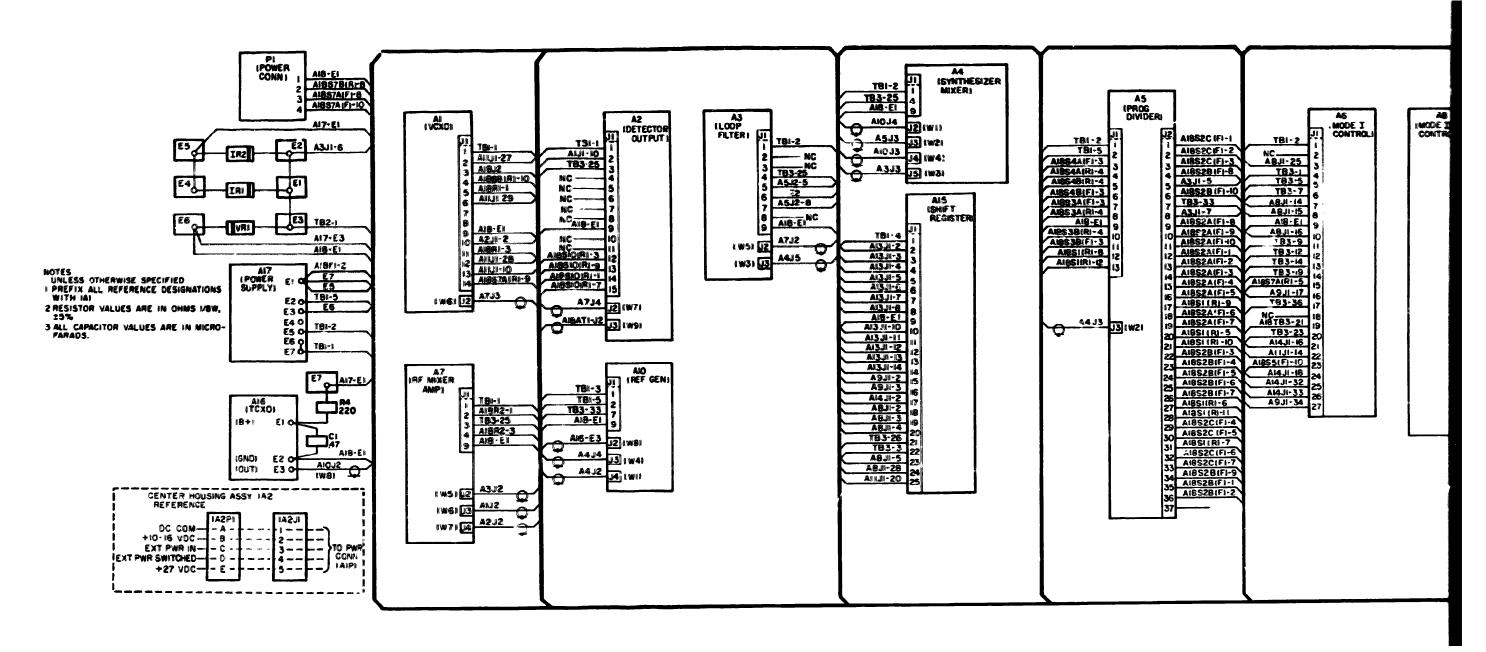

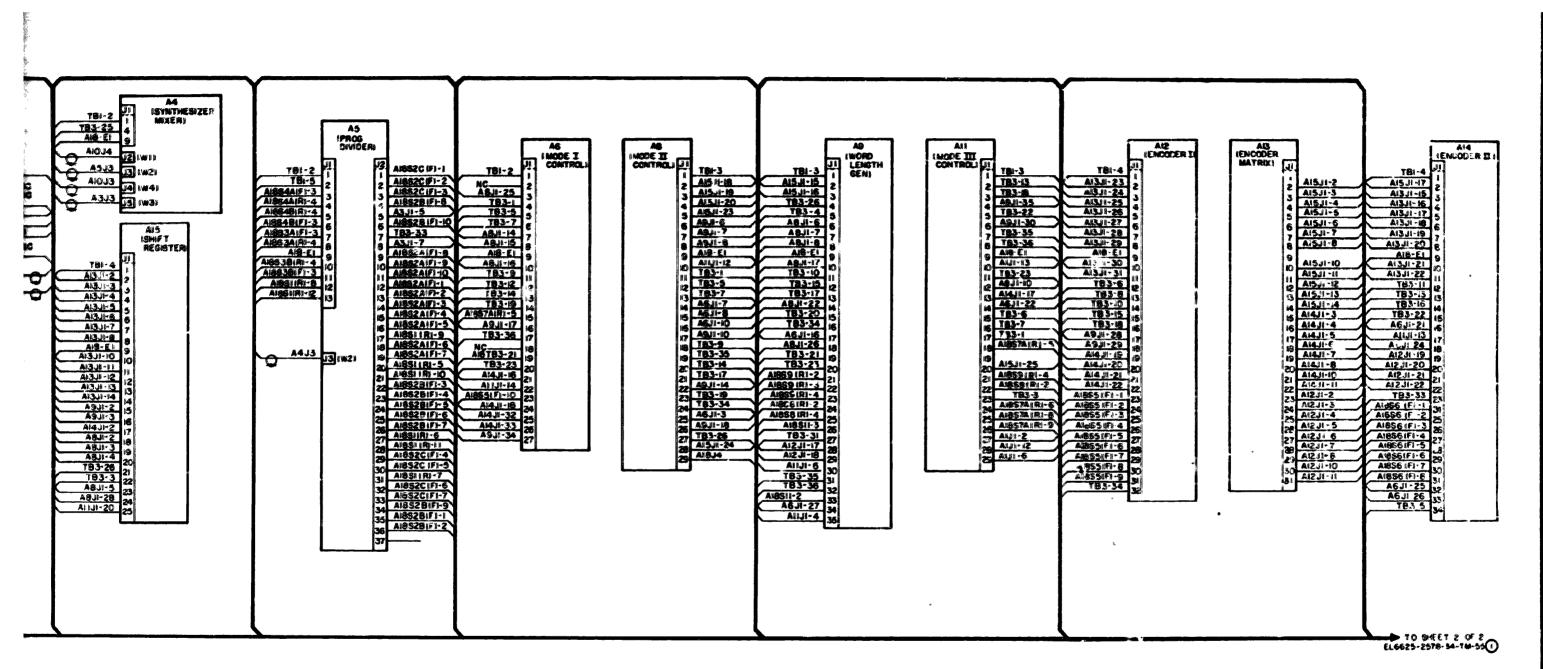

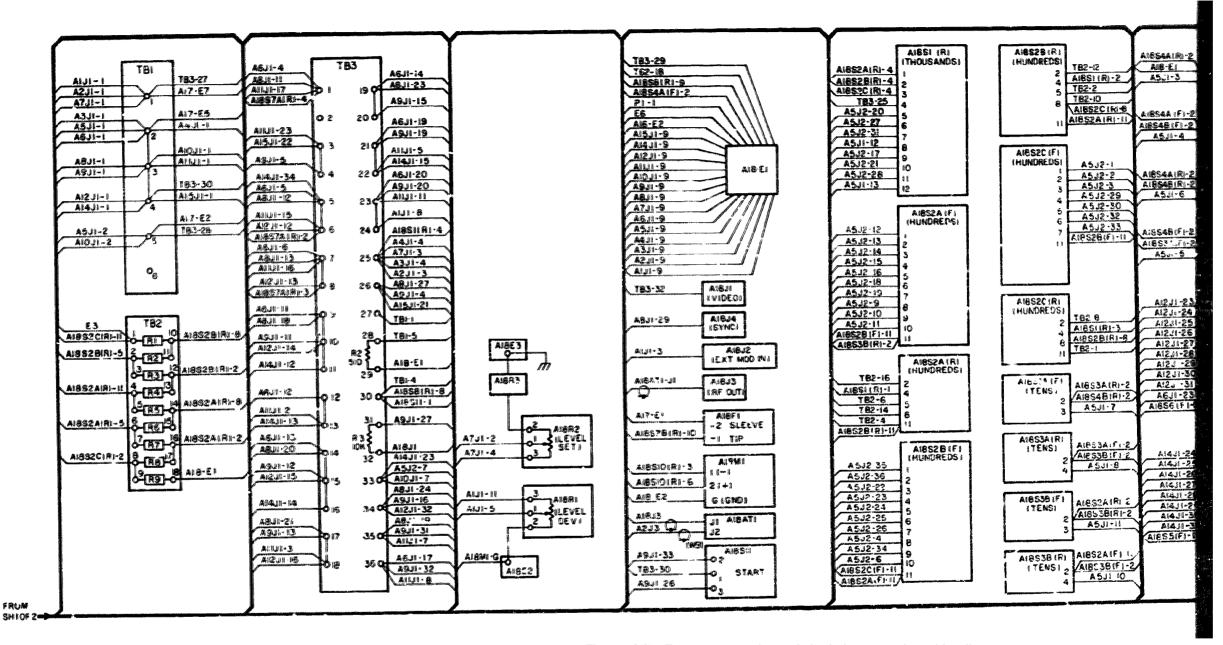

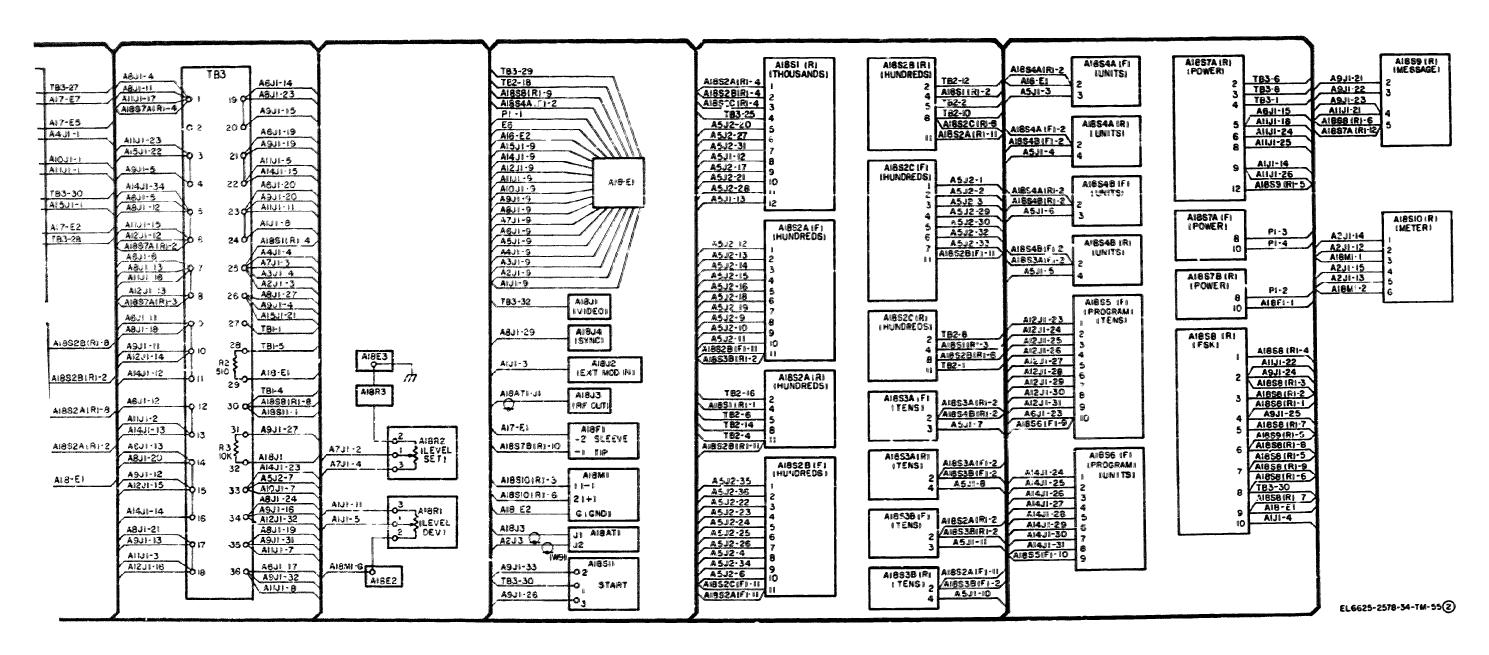

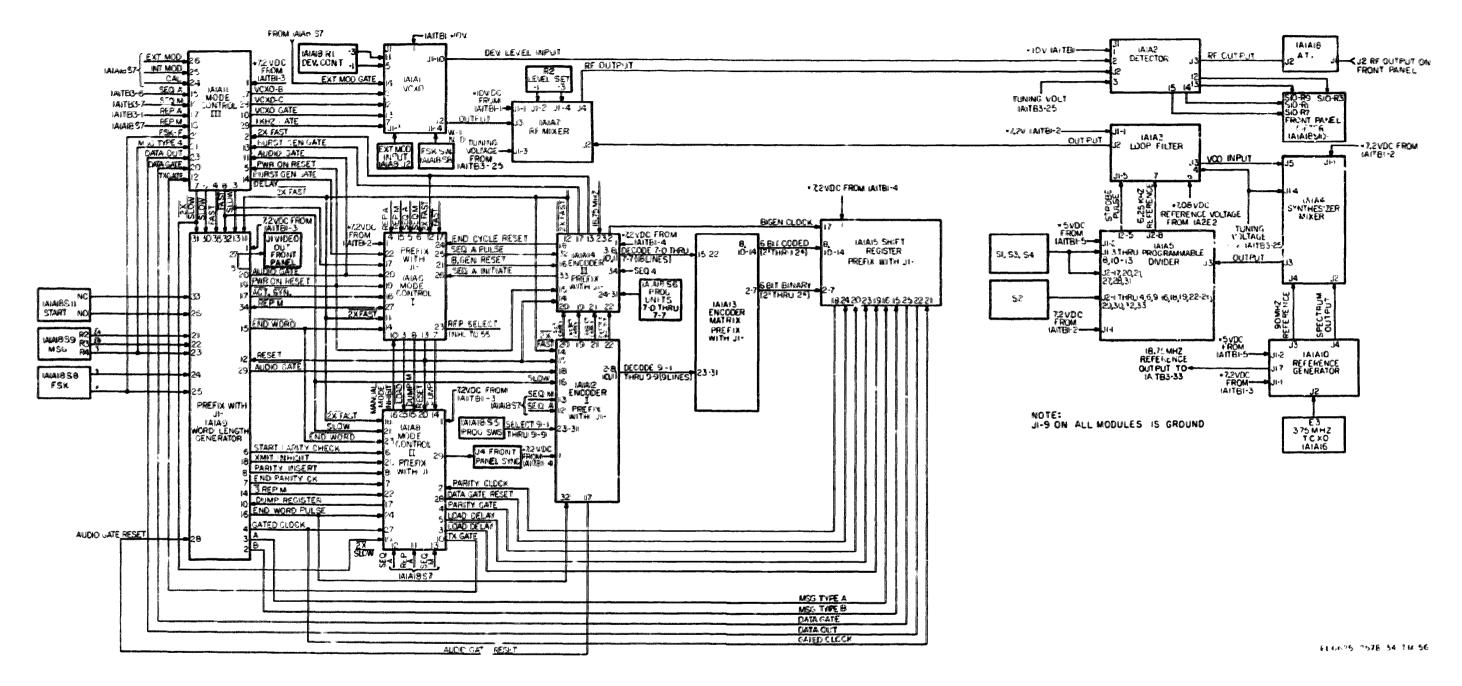

| 6-3.           | Test Set Power and Control Circuit, Interconnection Wiring Diagram Test Set Block Diagram                         | Fold-out             |

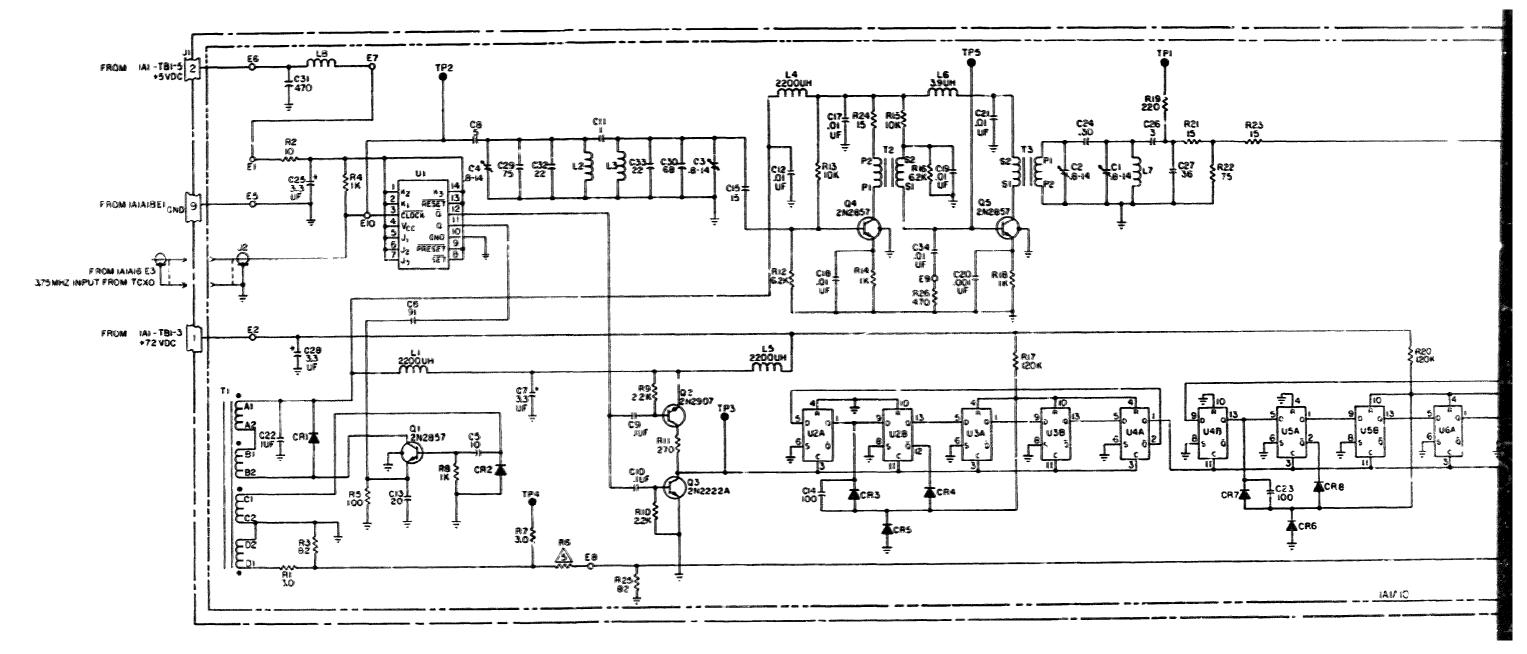

| 6-4.           | VCXO (1 MAI) Schematic Diagram                                                                                    | Fold-out             |

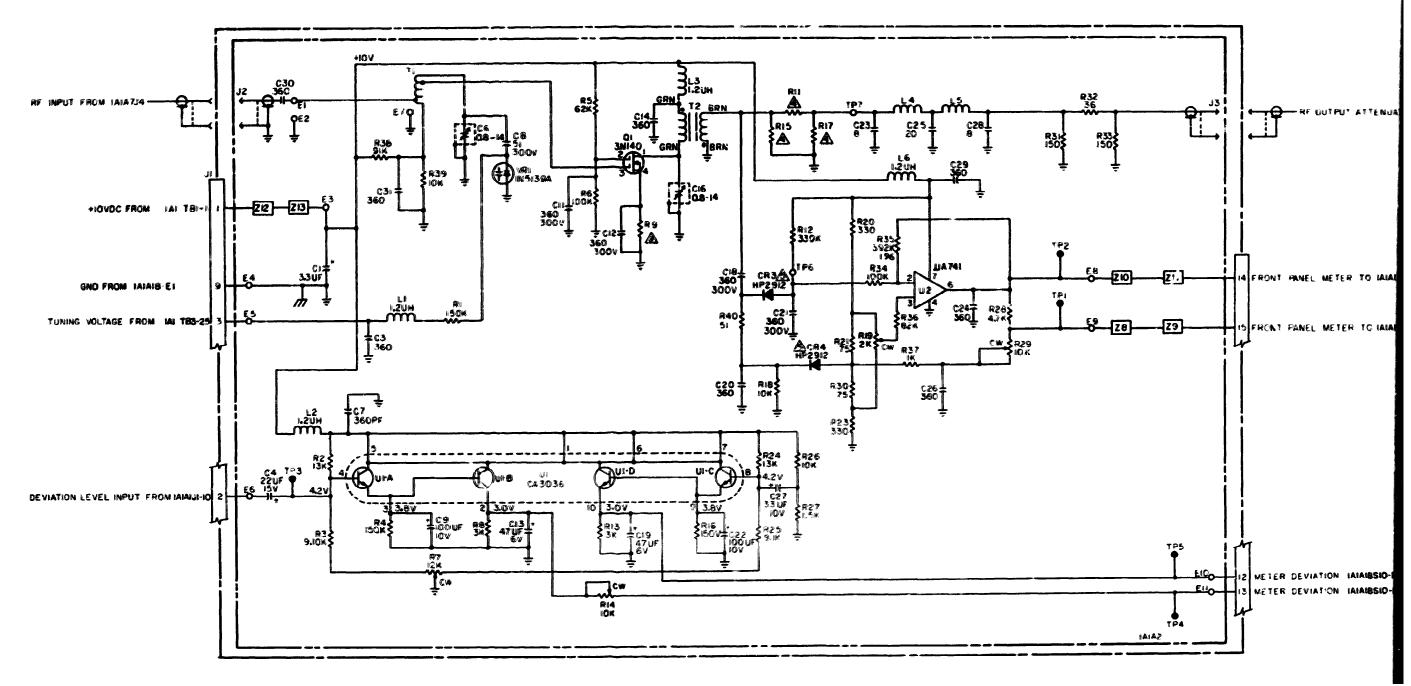

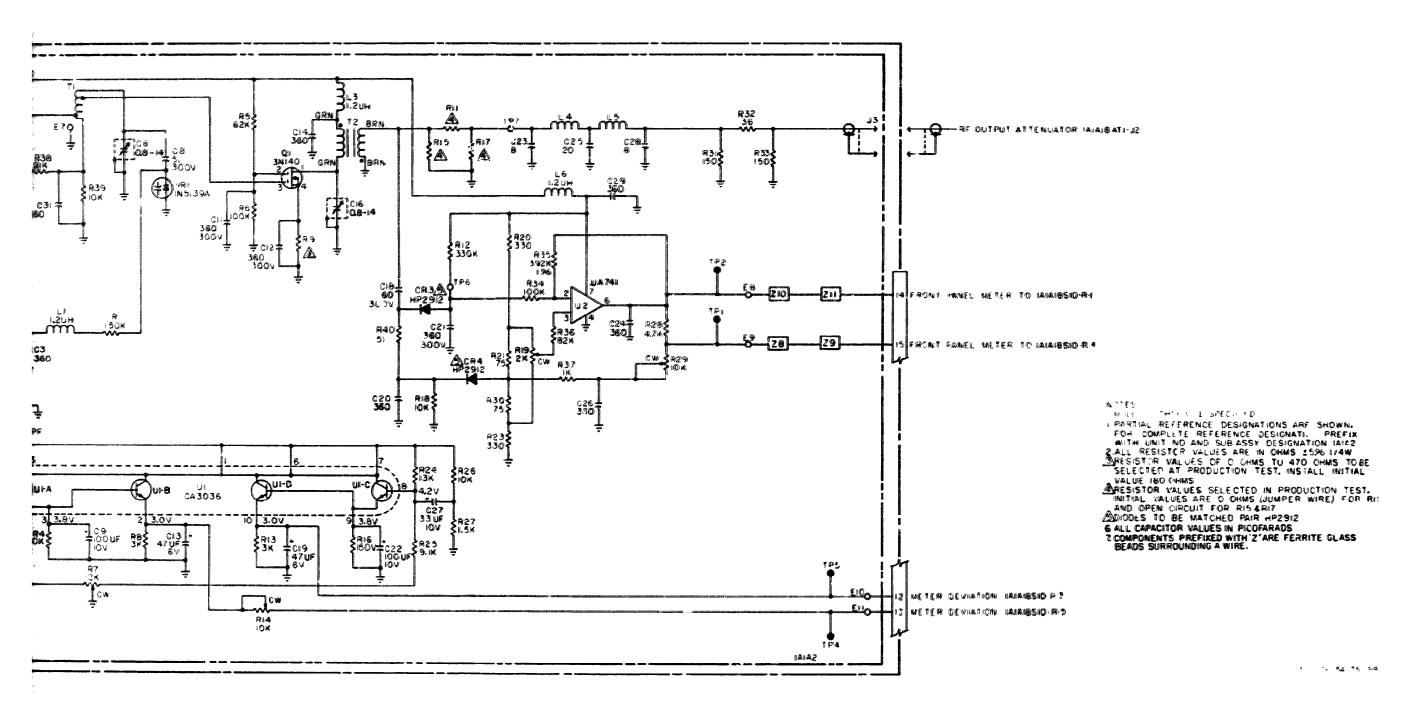

| 6-5.           | Detector Output (IAI 12) Schematic Diagram                                                                        | Fold-out             |

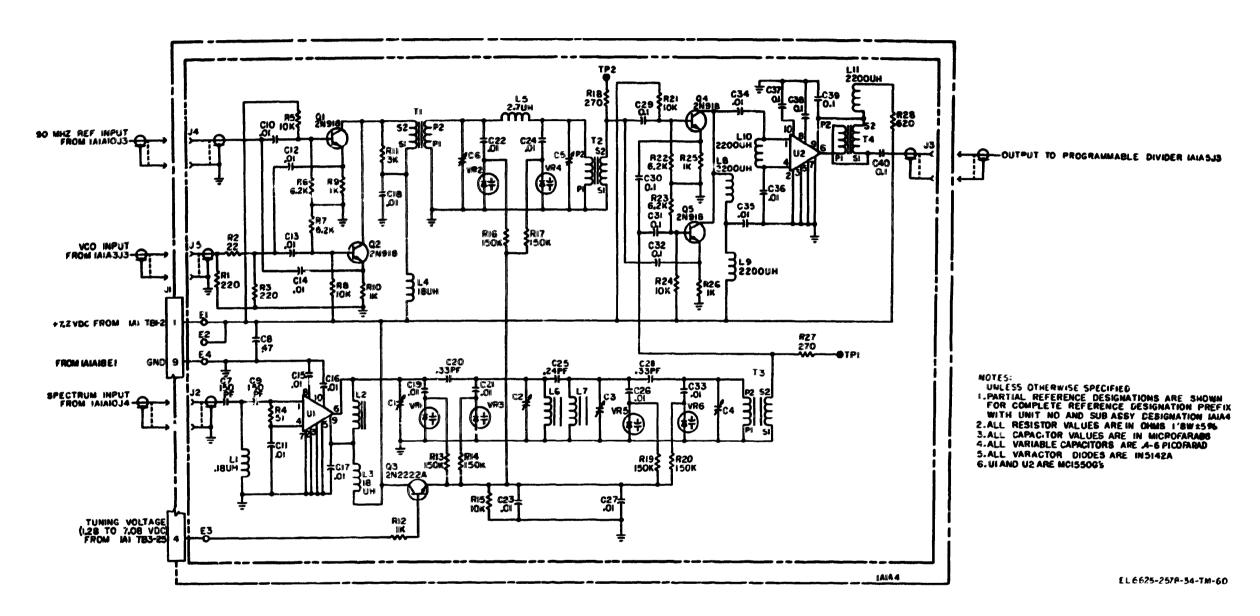

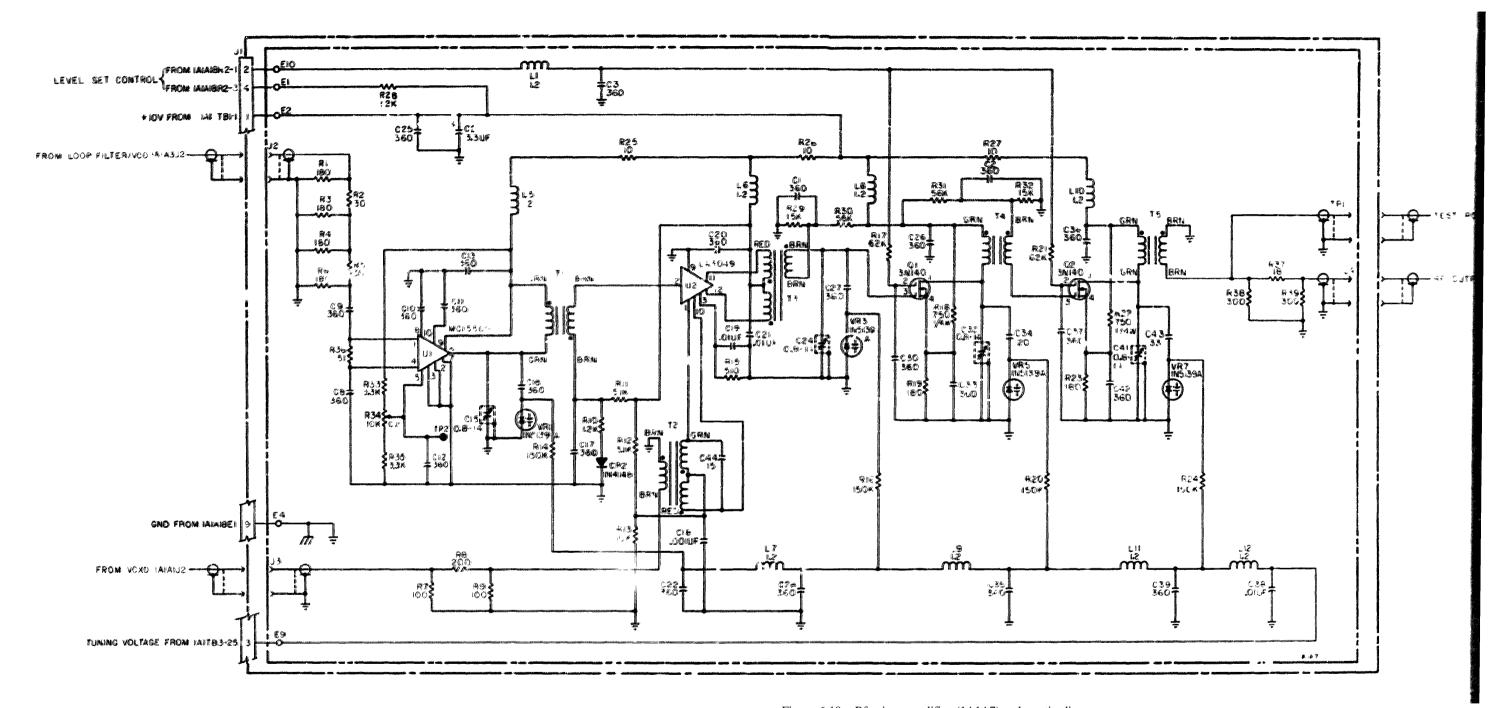

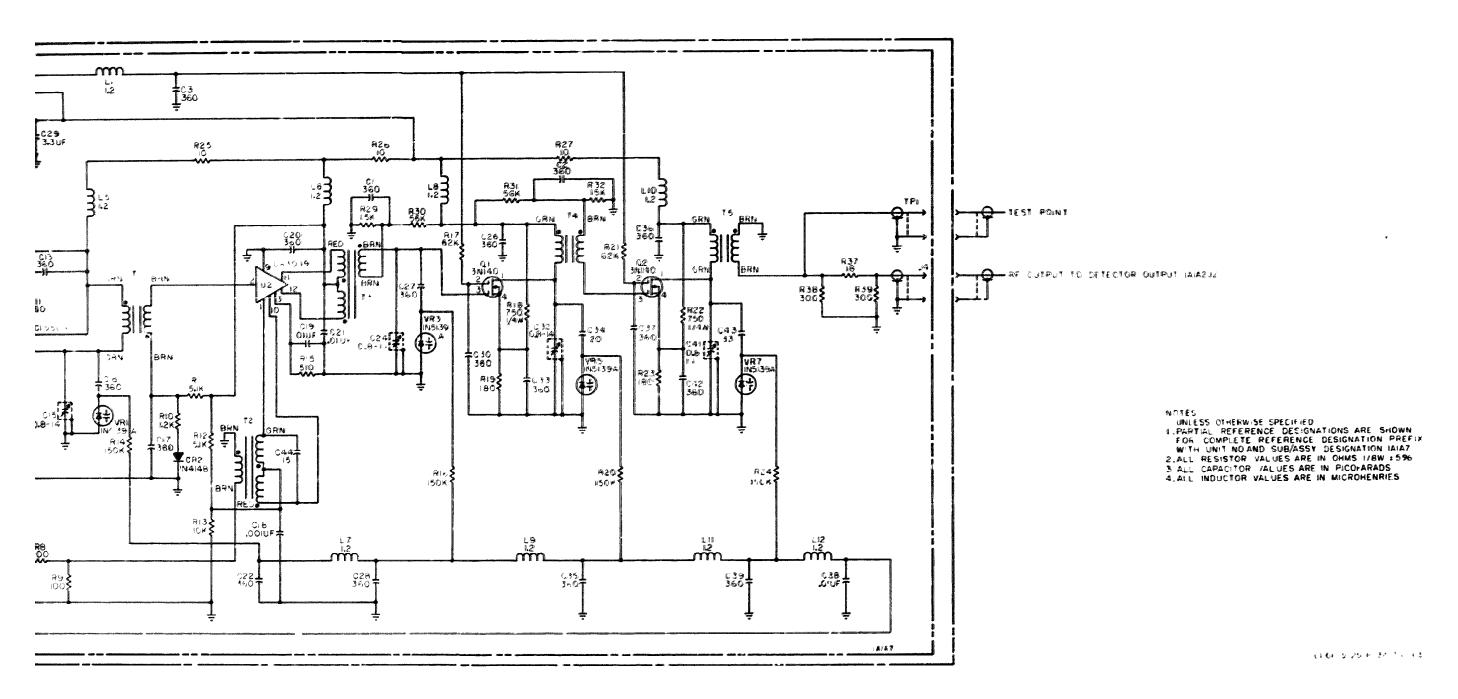

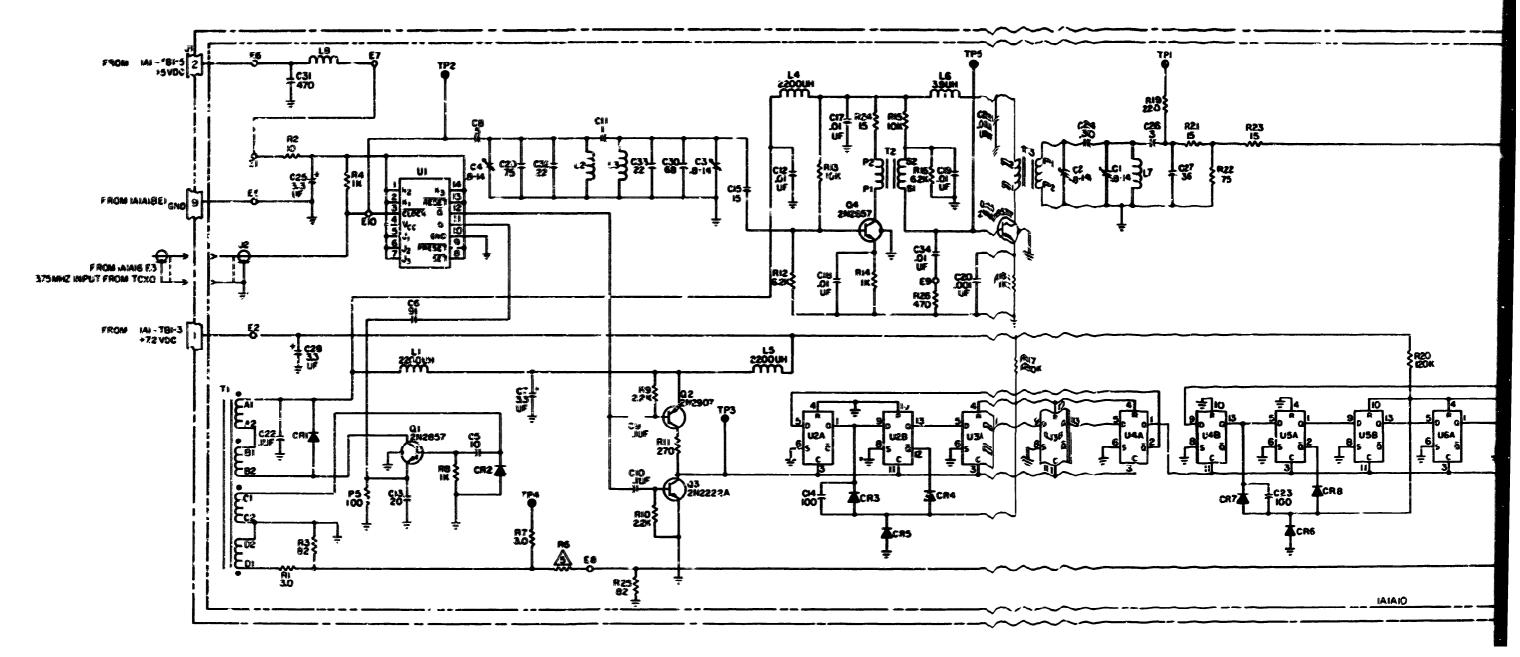

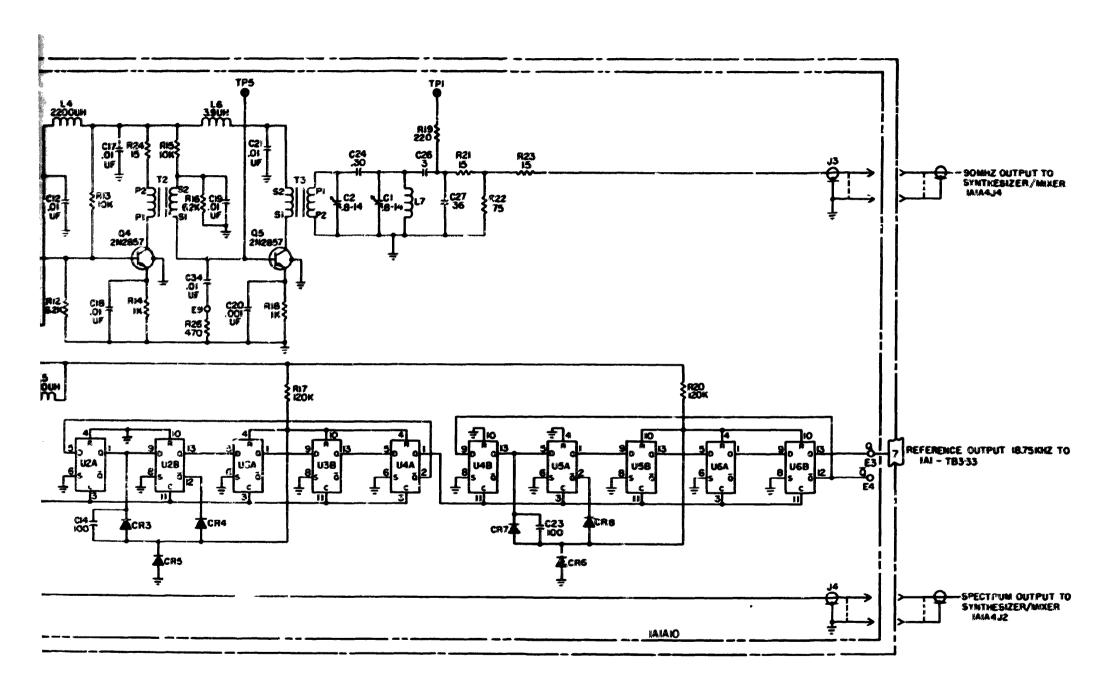

| 6-6.<br>6-7.   | Loop Filter VCO (1A1A3) Schematic Diagram                                                                         | Fold-out<br>Fold-out |

| 6-8.           | Synthesizer Mixer (1A1A1) Schematic Diagram                                                                       | Fold-out             |

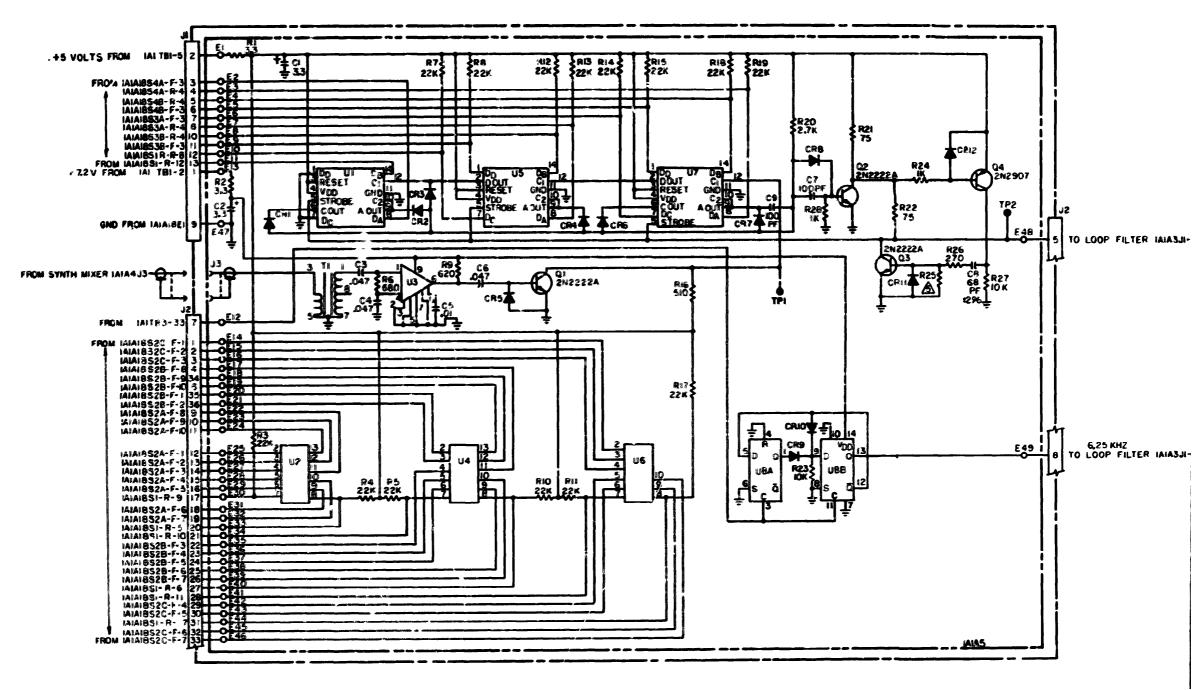

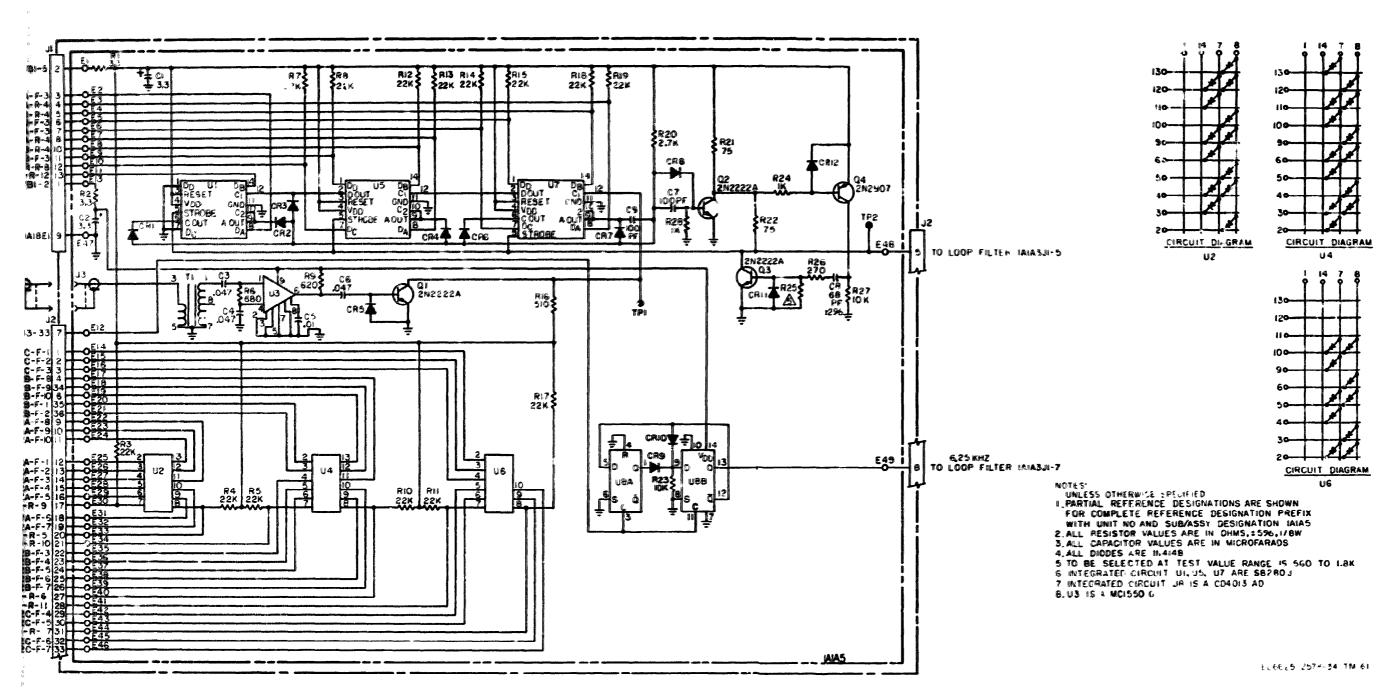

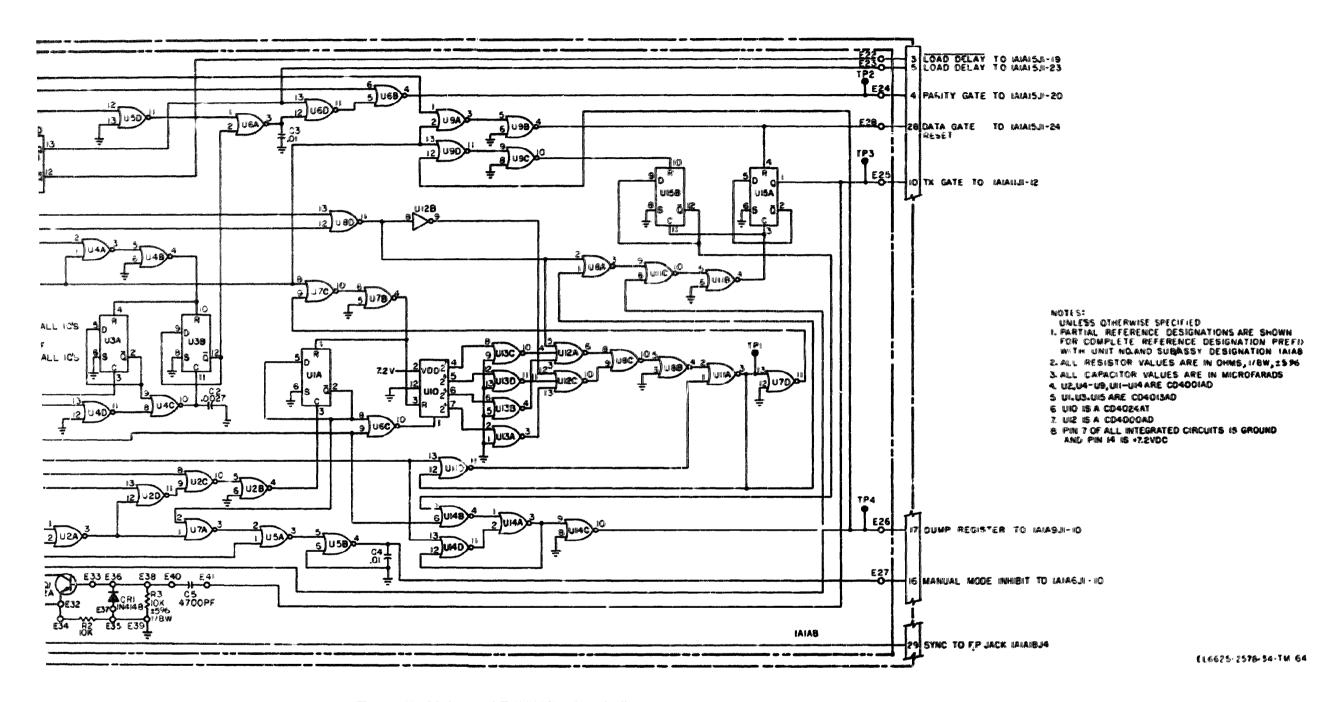

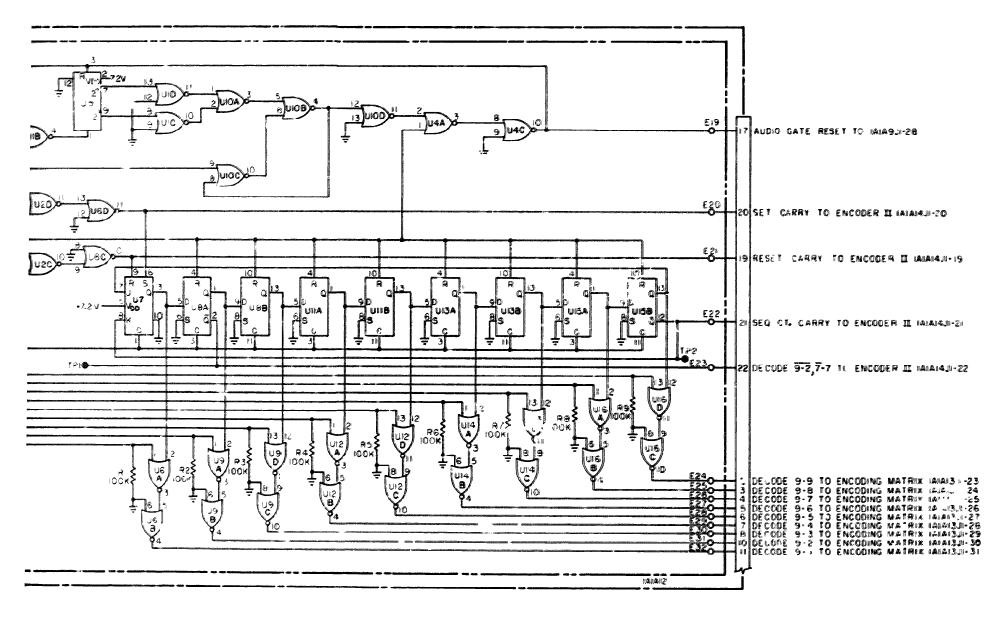

| 6-9.           | Programmable Duider (14145) Schematic Diagram  Mode Control I (14146) Schematic Diagram                           | Fold-out             |

| 6-10.          | RF Mixer Amplifier (1A1A7) Schematic Diagram                                                                      | Fold-out             |

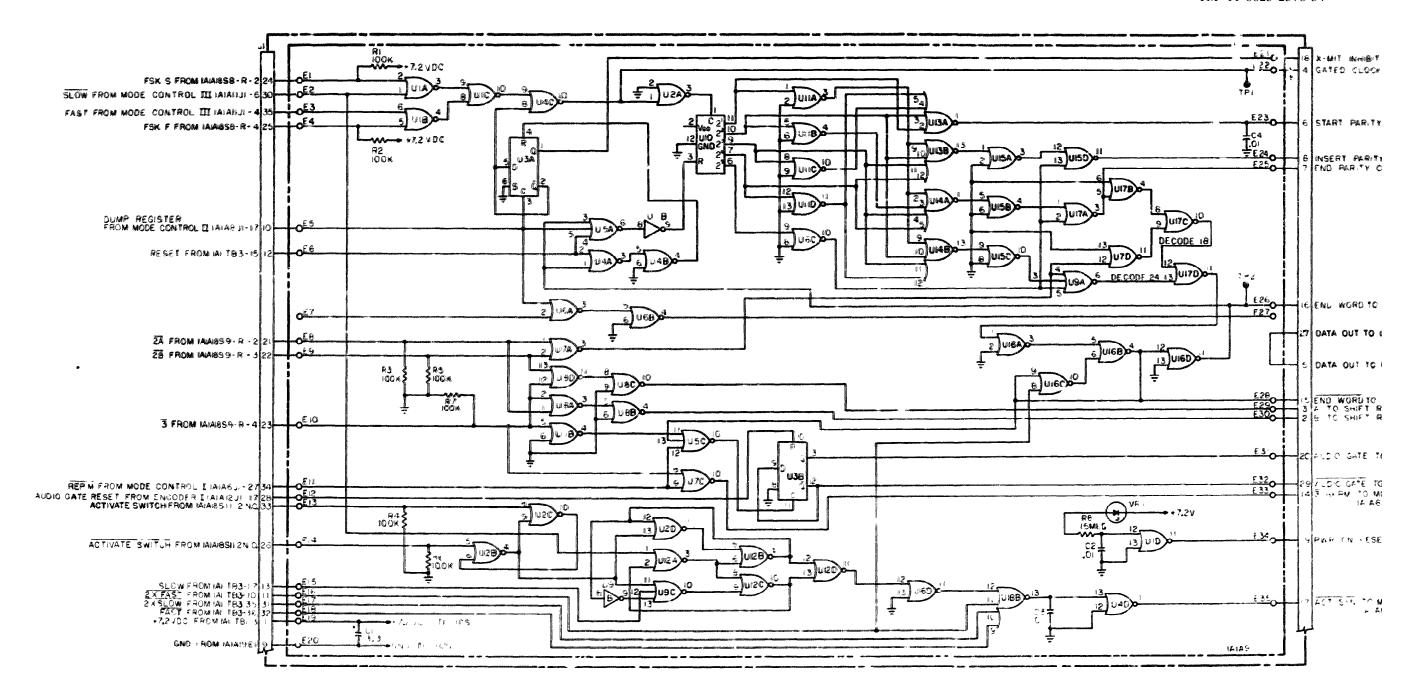

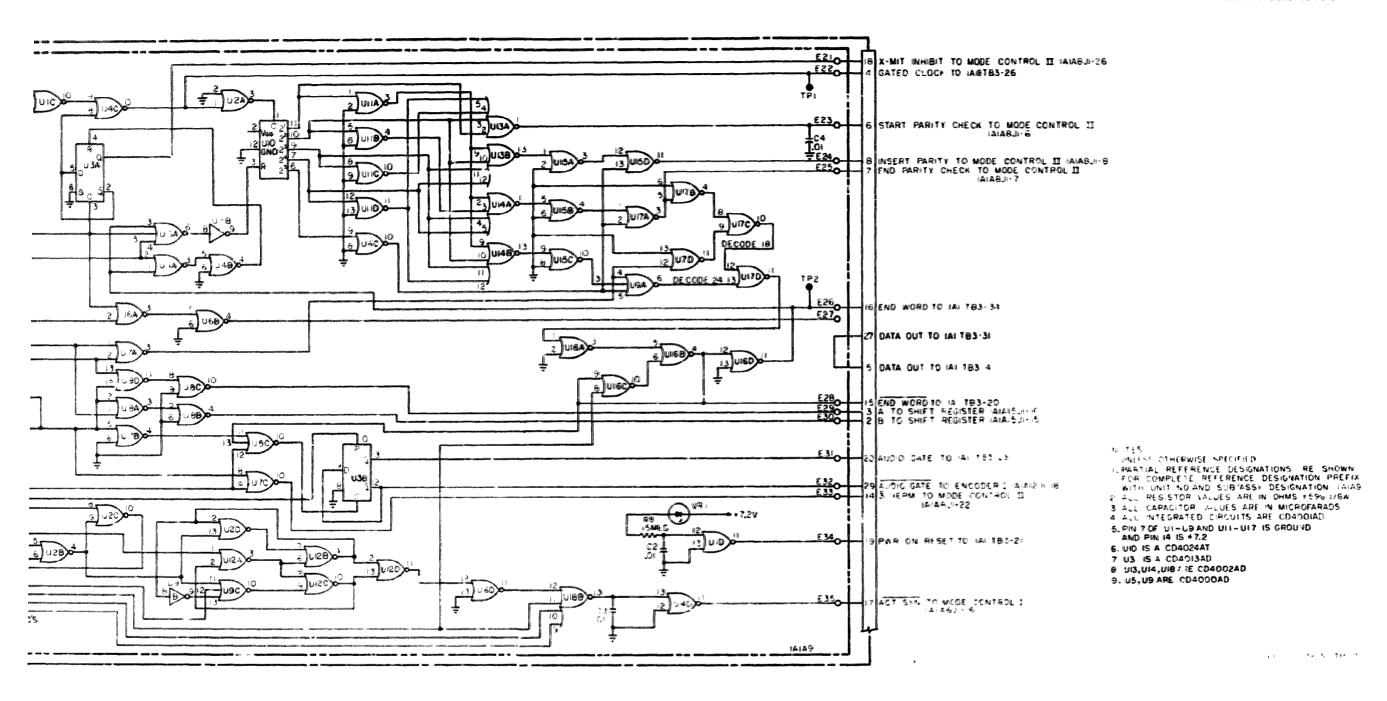

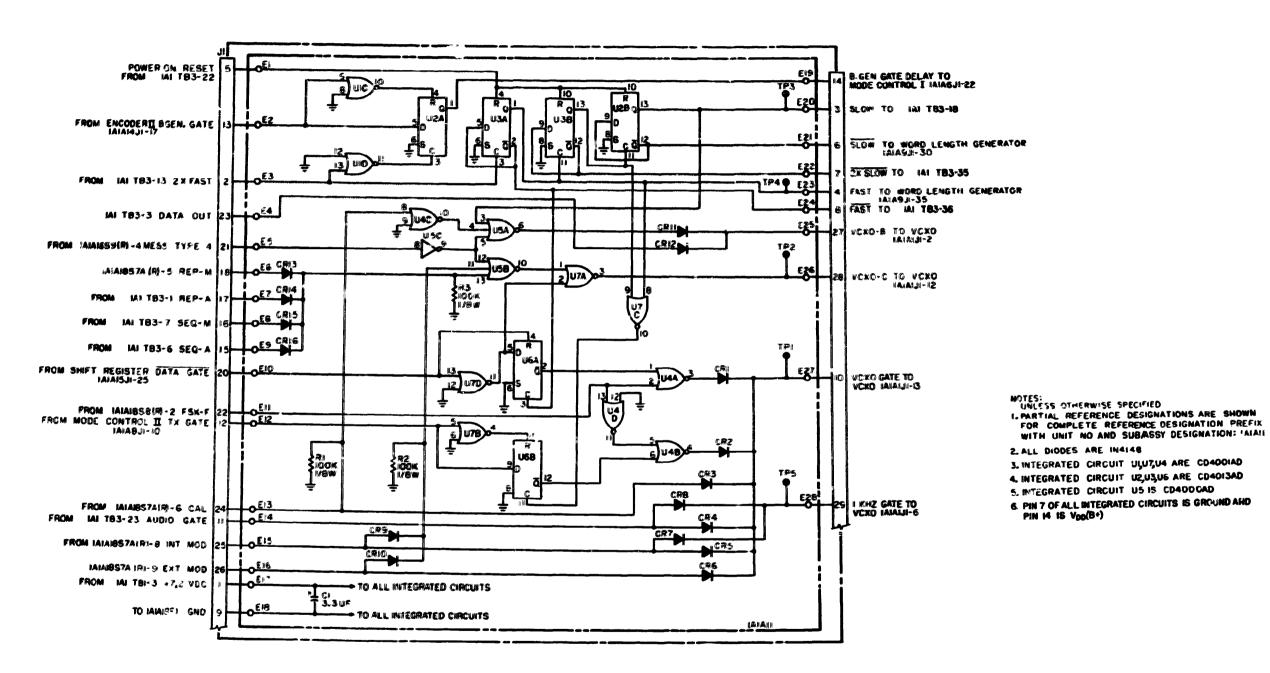

| 6-11.          | Mode Control I' (1 11 18) Schematic Diagram                                                                       | Fold-out             |

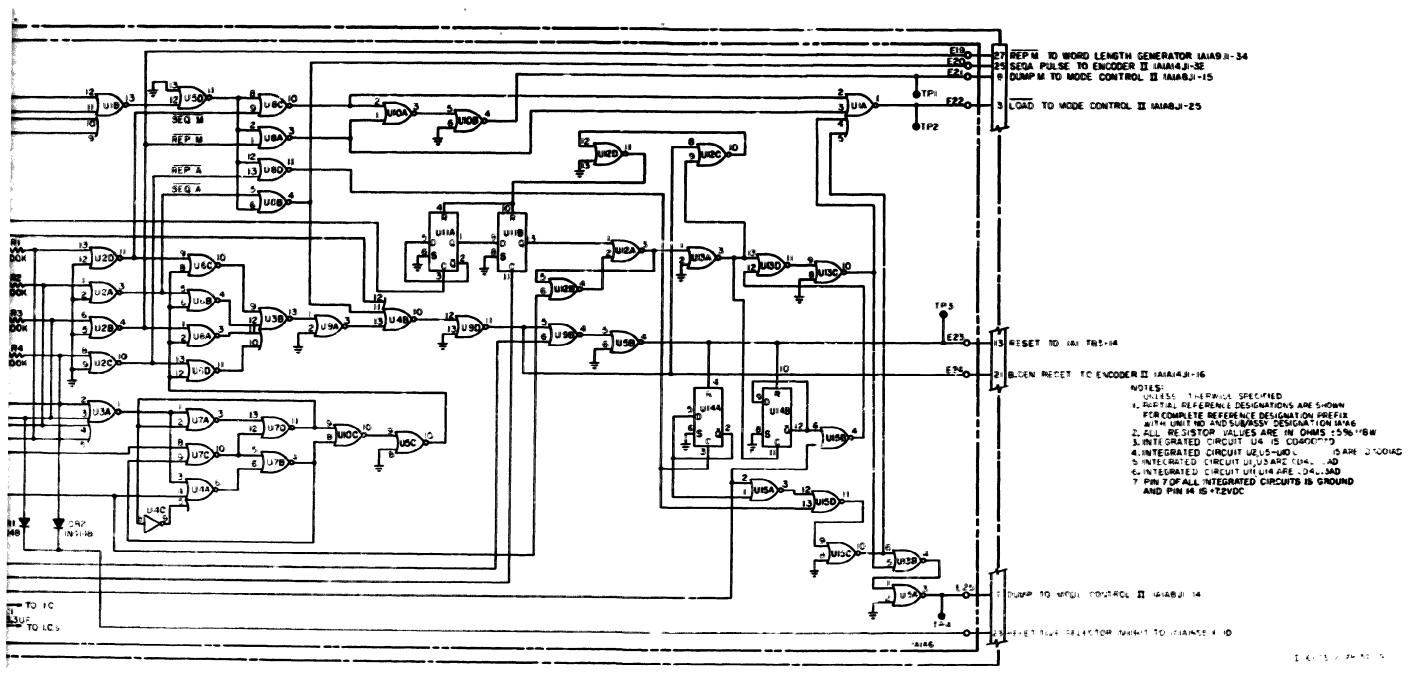

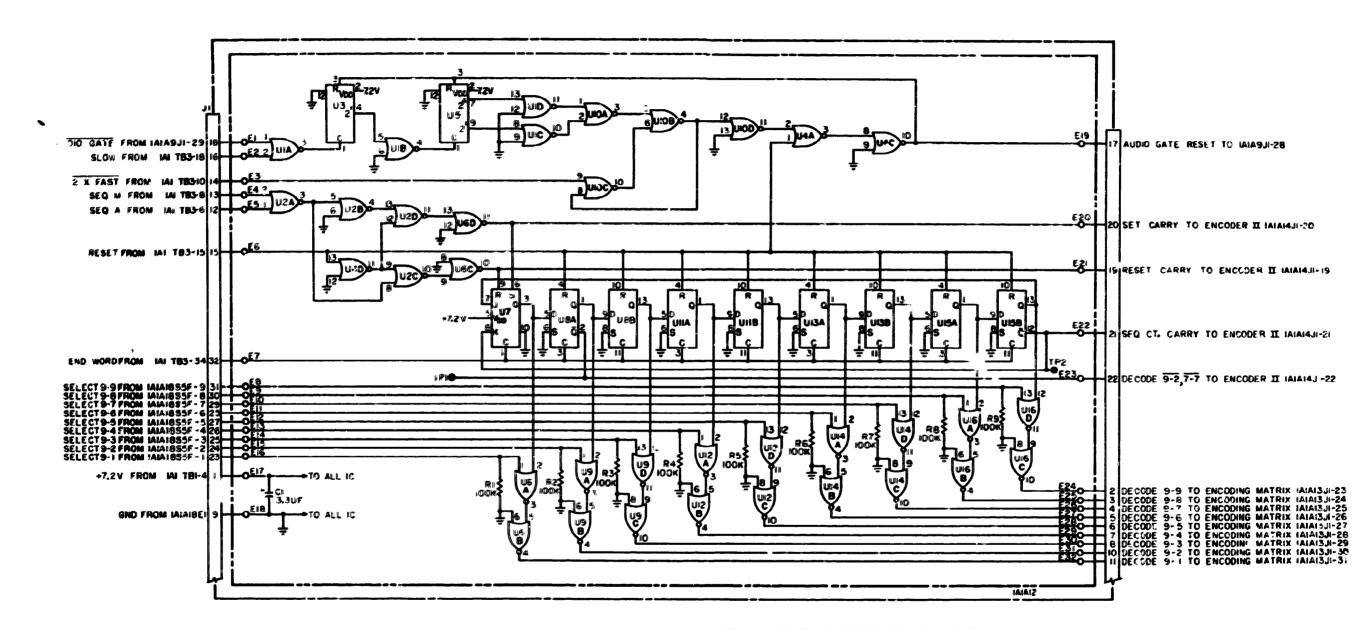

| 6-12.<br>6-13. | Word Length Generator (1A149) Schematic Diagram                                                                   | Fold-out<br>Fold-out |

| 6-13.<br>6-14. | Reference Generator (IAIAIO) Schematic Diagram                                                                    | Fold-out<br>Fold-out |

| 6-15.          | Mode Control III (1 X1 X11) Schematic Diagram  Liconer L (1 X1 X12) Schematic Diagram                             | Fold-out             |

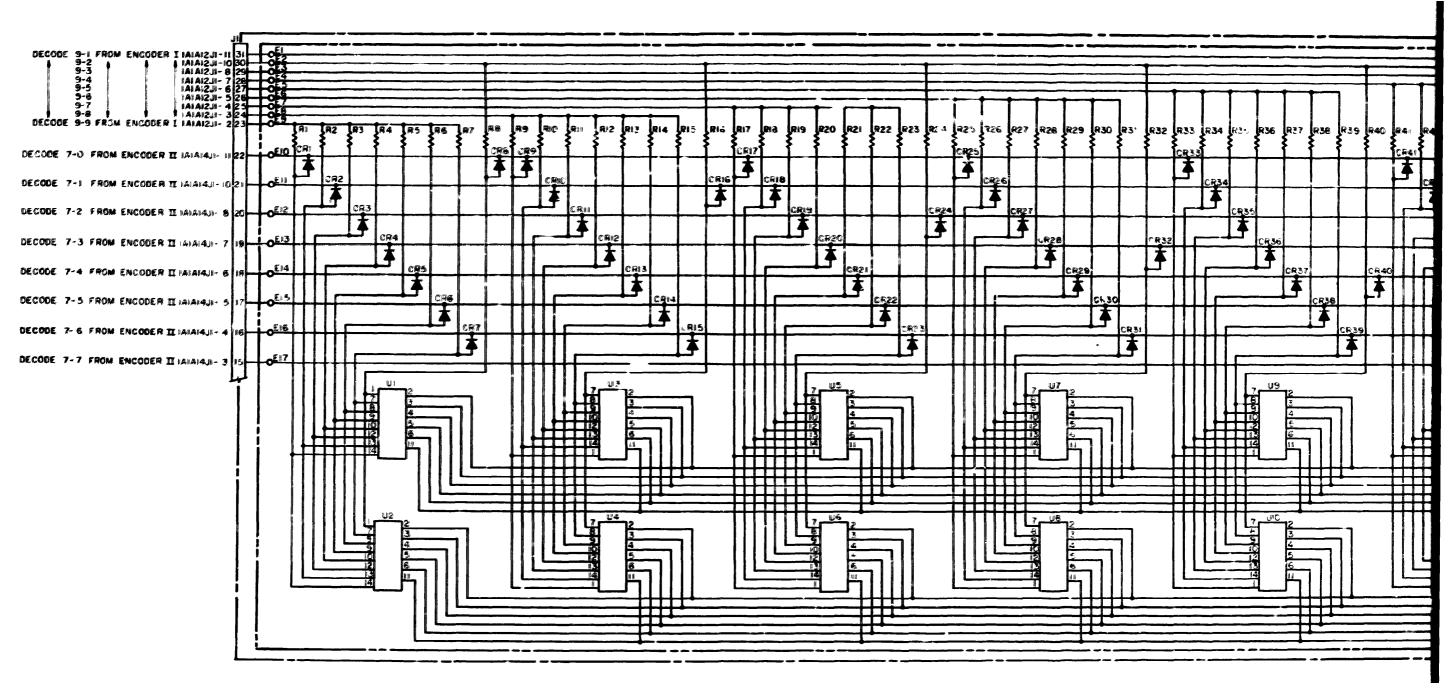

| 6-16.          | Freeder Matrix (INIAI3) Schematic Diagram                                                                         | Fold-out             |

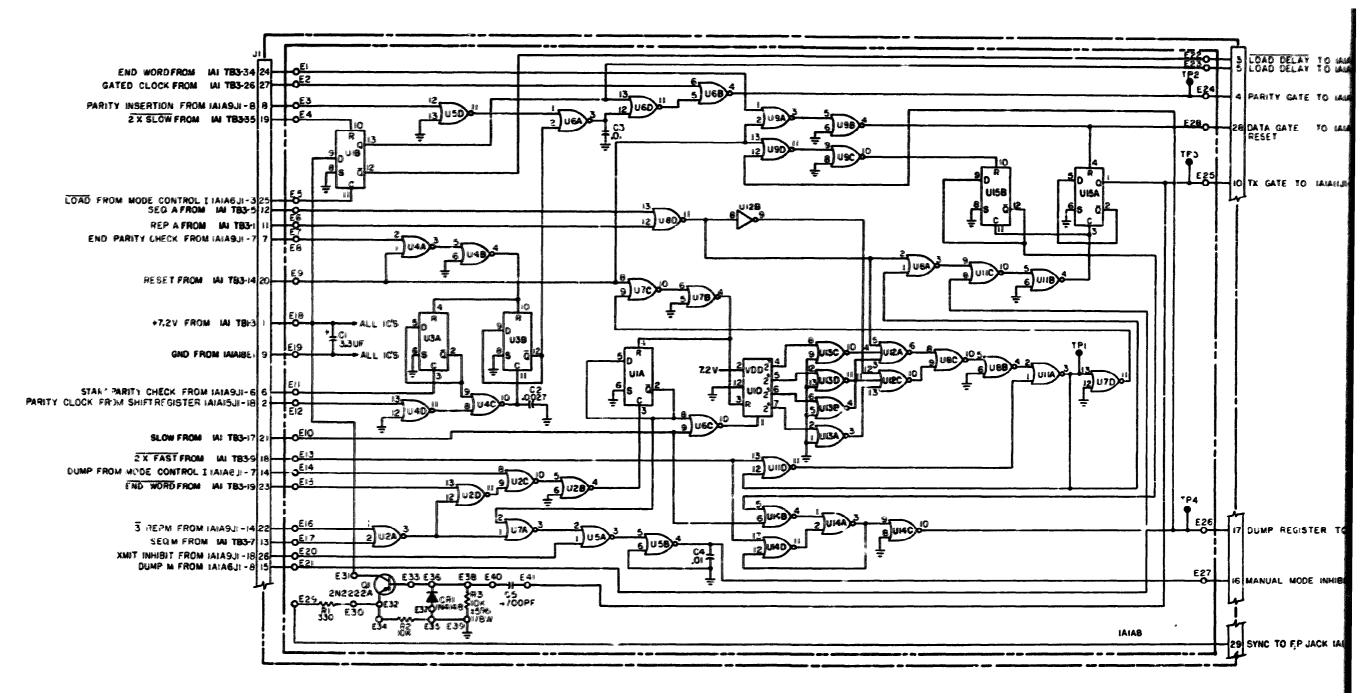

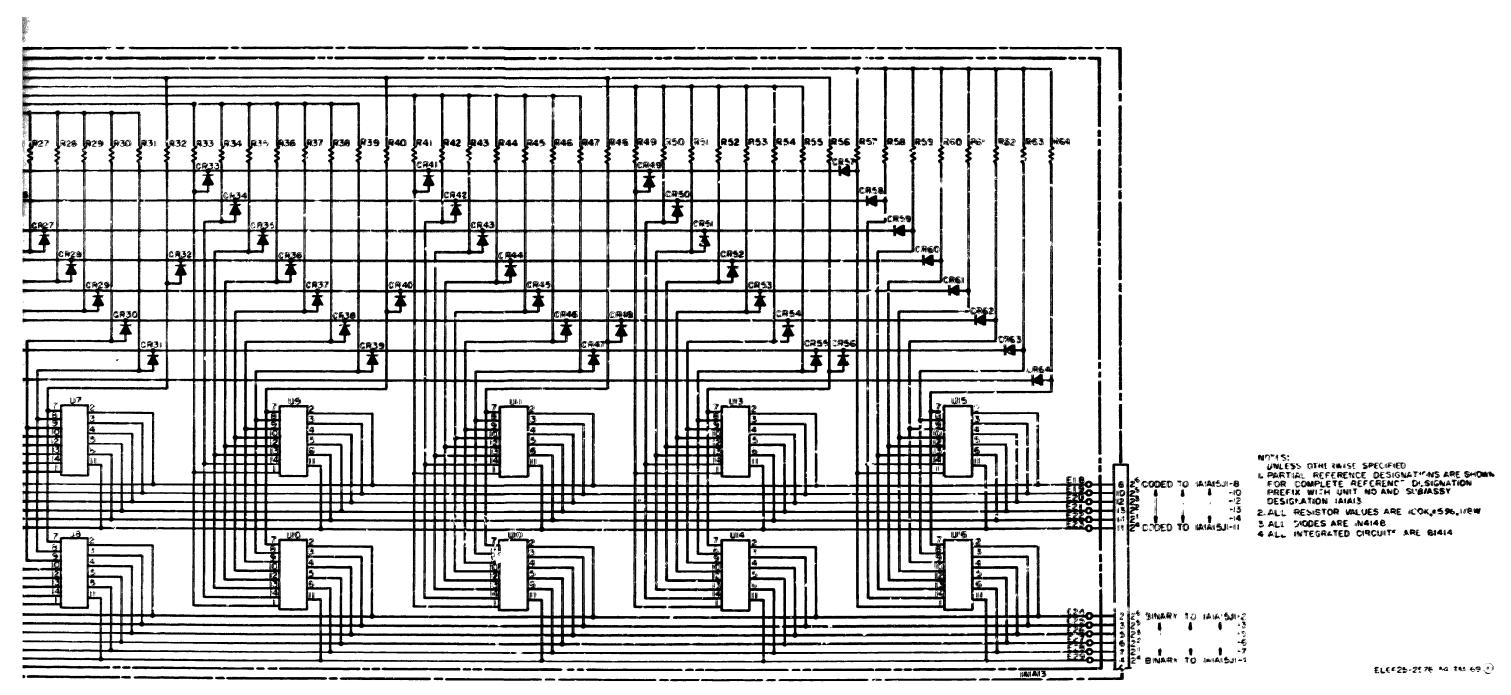

| 6-17.          | Encoder II (1 MAt) Schematic Diagram                                                                              | Fold-out             |

| 6-18.          | Shift Register #1 11 1174 Schematic Diagram                                                                       | Fold-out             |

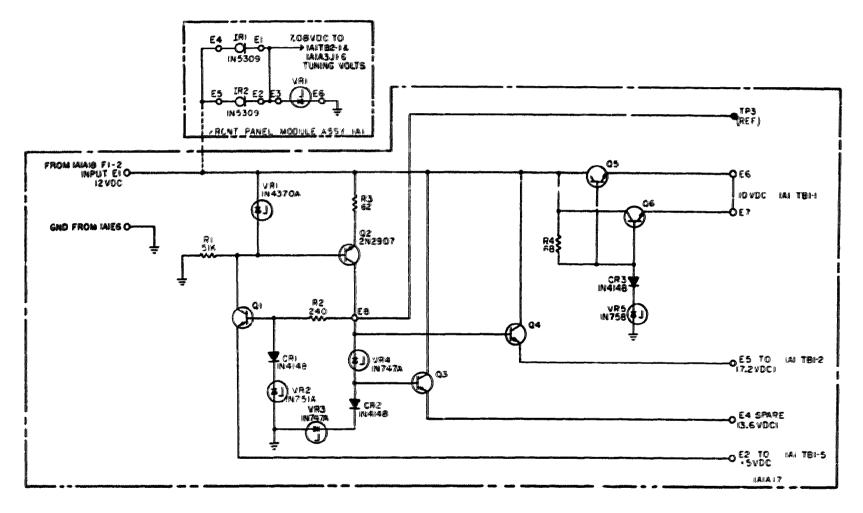

| 6-19.<br>6-20. | Power Supply Regulator (IAIAI7) Schematic Diagram                                                                 | Fold-out<br>Fold-out |

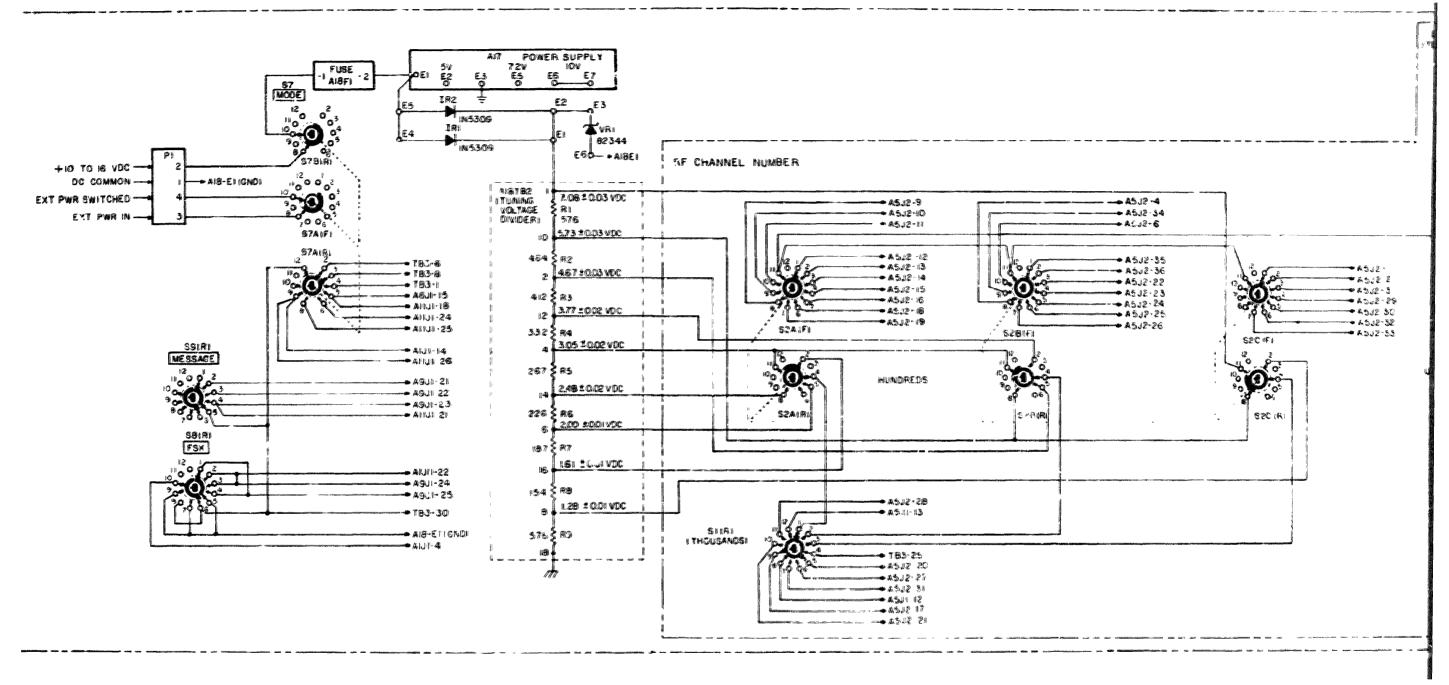

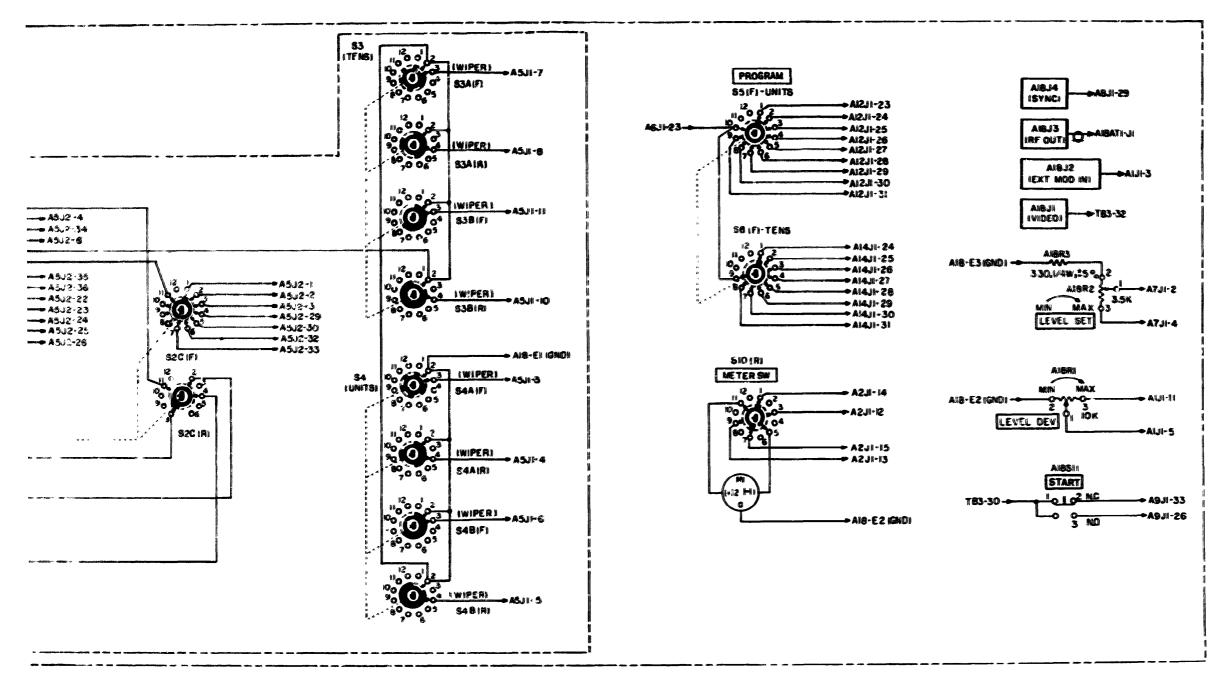

| 6-21.          | From Panel Centrol Interface (1A1A18) Schematic Diagram                                                           | Fold-out             |

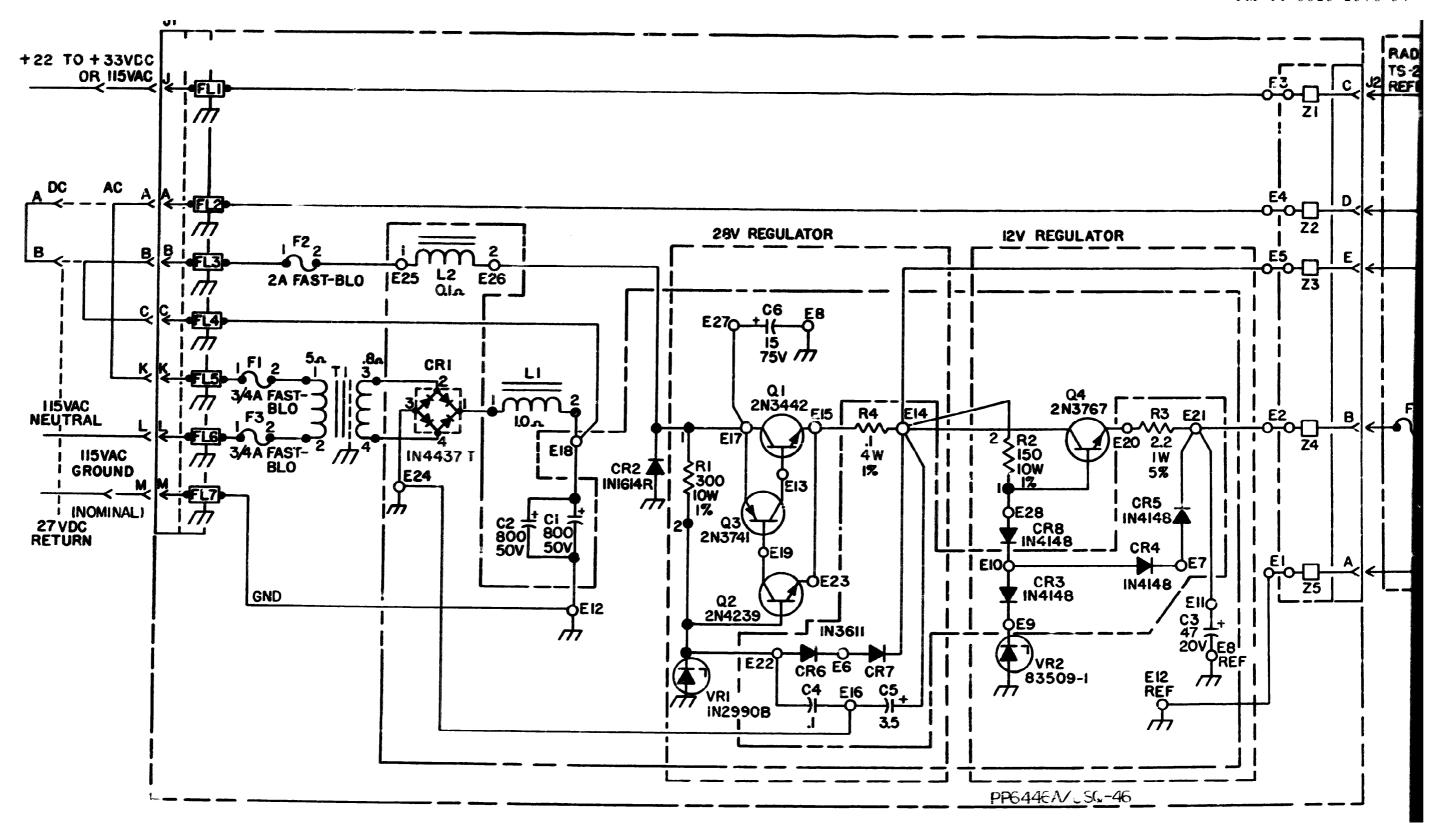

| -              | Prove supply PP6416A & SQ 46 (1A2) Schematic Diagram                                                              | 1 old out            |

#### LIST OF TABLES

| Table |                                            | Title | Page  |

|-------|--------------------------------------------|-------|-------|

| 2-1.  | Marsaga Type lalarestatication.            |       | 2-19  |

| 2-2.  | Message Type 2 Codi. r                     |       | 2-19  |

| 2-3.  | Message Type 3 Coding                      |       | 2-19  |

| 2-4.  | Ladio Tesi Sei Address Codes               |       | 2-20  |

| 6-1.  | Module Connector Wirms Color Code Sequence |       | 6-1   |

| 6-2.  | Chassis Wiring Color Code and Size         |       | 6 - 2 |

#### CHAPTER 1

#### INTRODUCTION

#### Section I.

#### 1-1. Scope

a This manual covers direct support and general support maintenance for the Radio Test Set Group OQ-60 USQ-16. Included is a functional description of the radio test set group, with croubleshooting, repair, replacement, adjustment alinement, and testing instructions for all required maintenance procedures. Also listed are tools, materials, and test equipment required for direct support, and general support maintenance

b. Operation, installation, and organizational maintenance instructions are in TM 11-6625-2578-12 which also contains the basic issue items listed and the maintenance allocation chart.

#### 1-2. Maintenance Forms and Records

Department of the Army forms and procedures used for equipment maintenance will be those prescribed by TM 38-750.

1-3. Destruction of Army Material to Prevent Enemy Use

Destruction of this equipment will be accompashed in accordance with TM 750-244-2. Au-

thorization to destroy this equipment must be given by divisional (or higher) commanders or a subordinate commander who has been delegated this authority. Destruction of 'he equipment will be reported through command channel

#### 1-4. Administrative Storage

Administrative storage of this equipment shall be accomplished in accordance with instructions contained in TM 740-90-1.

#### 1-5. Calibration

Pertinent publications on calibration of this equipment shall be referenced.

# 1-6. Reporting of Equipment Manual Improvements

The reporting of errors, omissions, and recommendations for improving this publication by the individual user is encouraged Reports should be submitted on DA Form 2028 (Recommended Changes to Publications) and forwarded direct to Commander, US Army Electronics Command, ATTN: AMSEL-MA-SR, Fort Monmouth, NJ 07703.

#### Section II. DESCRIPTION AND DATA

#### 1-7. Description

Refer to TM 11-6625-2578-12 for the general description of the Radio Test Set Group OQ-60 USQ-46

#### 1-8. General Characteristics

a Refer to TM 11-6625-2578-12 for technical characteristic data for the Radio Test Set Group OQ-60 USQ-46.

b In addition to the data listed in TM 11-

6625–2578-12, reference designators, momenclature, and common names of major assembles and subassembles of the radio test set group are provided in chart 1-1. The reference designators were assigned to the OQ-60/USQ-16 in accordance with the unit numbering method of American Standard, Electrical Reference Designator-ASA Y32.16.

c The major assemblies or subassemblies are referred to by their common name throughout this magnal

Chart 1-1. Radio Test Set Group OQ-60 USQ-46 Reference Designator, Nomenclature, and Common Name

| Reference<br>designator | Nomenciature                                          | A water of the statement |

|-------------------------|-------------------------------------------------------|--------------------------|

| 1                       | Radio Test Set TS-2963 USQ-46                         | Test set                 |

| 1A1                     | Front panel module assembly                           | Front panel module ass.  |

| 1A1A1                   | Voltage controlled crystal oscillator module assembly | vcxo                     |

| 1A1A2                   | RF detector—output module assembly                    | RF de ector              |

| 1A1A3                   | Loop filter—module assembly                           | Loop filter              |

| 1A1A4                   | Synthesizer mixer module assembly                     | Synthesizer mixer        |

| IA1A5                   | Programable divider module assembly                   | Programable divider      |

| 1A1A6                   | Mode control I module assembly                        | Mode control !           |

| 1A1A7                   | RF mixer amplifier module assembly                    | RF mixer amplifier       |

| 1A1A8                   | Mode control II module assembly                       | Mode control II          |

| 1A1A9                   | Word length generator module assembly                 | Word length generator    |

| 1A1A10                  | reference generator module assembly                   | Reference generator      |

| 1A1A11                  | Mode control III module assembly                      | Mode control III         |

| 1A1A12                  | Encoder I module assembly                             | Encoder I                |

| IA1A13                  | Encoder matrix module assembly                        | Encoder matrix           |

| 1A1A14                  | Encoder 1 module assembly                             | Encoder II               |

| 1A1A15                  | Shift register module assombly                        | Shift register           |

| 1A1A16                  | Temperature compensated crystal oscillator            | TCXO                     |

| 1A1A17                  | Power supply regulator power assembly                 | Power regulator          |

| 1A1A18                  | Front panel assembly                                  | Front panel assembly     |

| 1W1                     | RF Cable Assembly CG-3628 U                           | RF cable                 |

| 2                       | Power Supply PP-6446A USQ-46                          | Power supply             |

| 2W1                     | Ac Power Cable Assembly CN-12313 U                    | Ac cable                 |

#### CHAPTER 2

#### FUNCTIONING OF EQUIPMENT

#### Section I. INTRODUCTION

#### 2-1. General

The Radio Test Set TS-2963/USQ-46 with associated Power Supply PP-6446A/USQ-46 form a portable signal generating device designed to simulate all signals that RF Monitor Sets AN/USQ-46 or AN/USQ-46A can receive and act upon. The Radio Test Set generates fm signals from 160 to 176 MHz, providing 2520 output channels with 6.25 kHz channel spacing.

#### 2-2. Functional Divisions

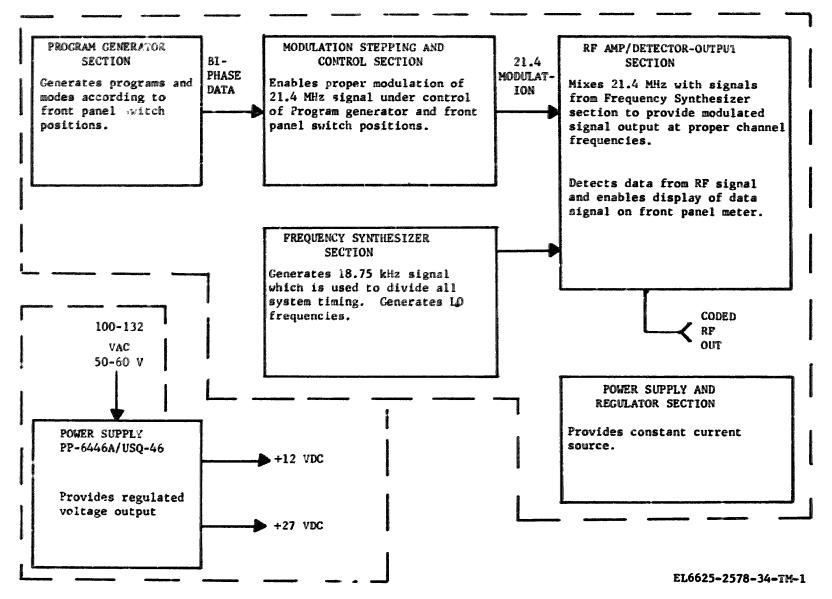

The radio test set consists of six functional sections as shown in figure 2-1. Paragraphs 2-6 through 2-12 describe the general functioning of each module within these sections. Detailed description of each module function is provided in paragraphs 2-13 through 2-16.

Figure 2-1. Radio test set basic block diagram.

# Section II. ANALYSIS OF RECURRING AND NONRECURRING INTEGRATED CIRCUITS

#### 2-3. General

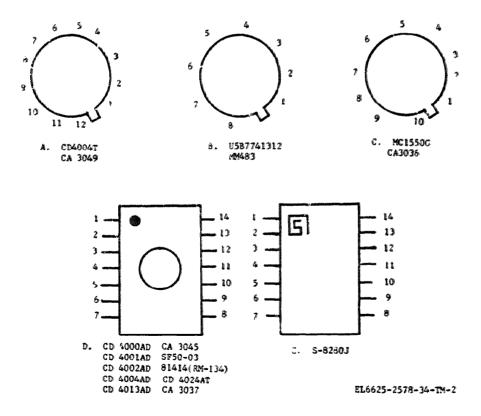

- a. Integrated circuits (IC's) are used throughout the radio test set functional sections and almost entirely in the logic section. Each IC contains one or more logic elements such as NOR gates, inverters, fip-flops, shift registers, counters, or amplifiers contained in a protective package. Five package configurations are used throughout the Radio Test Set. These configurations are shown in figure 2-2 as an aid to pin number identification of various IC's.

- b. The 14-pin flat packages (D and E, fig. 2-2) have a lead identification or manufacturers trademark dot in the upper left-hand corner which represents the pin number starting point. The remaining IC's are contained in TO-5 type housings and have a case tip which represents the starting or ending point for pin numbers (A through C, fig. 2-2).

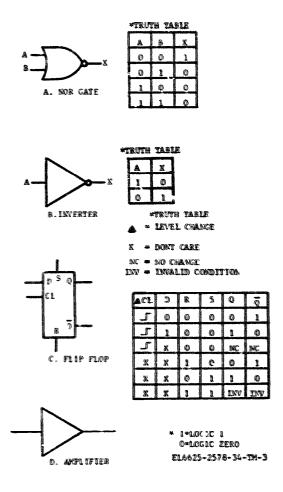

- 2-4. Symbology and Terminology of Recurring Elements of Integrated Circuits

- a. NOR Gate. The logic symbol for a NOR gate is shown in A, figure 2-3. A NOR gate is said to be enabled when one or both of the inputs (A or B) is a logic one (approximately +7.2 vdc). Enabling the NOR gate results in a logic zero (approximately 0 vdc) output (X). If all inputs are low, the gate is said to be inhibited and the output is high.

- b. Inverter. The logic symbol for the inverter is shown in B, figure 2-3. A logic one input to an inverter results in a logic zero output. Conversely, a logic zero input results in a logic one output.

- c. Flip-Flop. The logic symbol for a flip-flop is shown in C, figure 2-3. The flip-flop has two possible output states; Q and  $\overline{Q}$  (the latter is proncunced NOT Q). Output states are controlled

Figure 2-2. Integrated circuit pin arrangements.

Figure 2-3. Integrated circuit logic symbols.

by the input level at the data input (in conjunction with a clock pulse) and the level at either the DC SET (if used) or DC RESET inputs. The logic level present at the data input is transferred to the Q output during the positive going transition of a clock pulse. The  $\overline{\mathbf{Q}}$  output will always be in the opposite state from the Q output. The DC SET (if used) and DC RESET inputs are independent of, and override, clock and data inputs. A logic one at the DC SET (if used) input causes the Q to become a logic one and  $\overline{\mathbf{Q}}$  a logic zero. A logic one at the DC RESET input causes Q to become a logic zero and  $\overline{\mathbf{Q}}$  a logic one. The flip-flop will remain in either state indefinitely until reversed by appropriate input signals.

d. Amplifiers. Amplifiers, as they are shown on schematic diagrams, are represented in D, figure 2-4. These amplifiers are operational amplifiers, athough they may connect for a specific function.

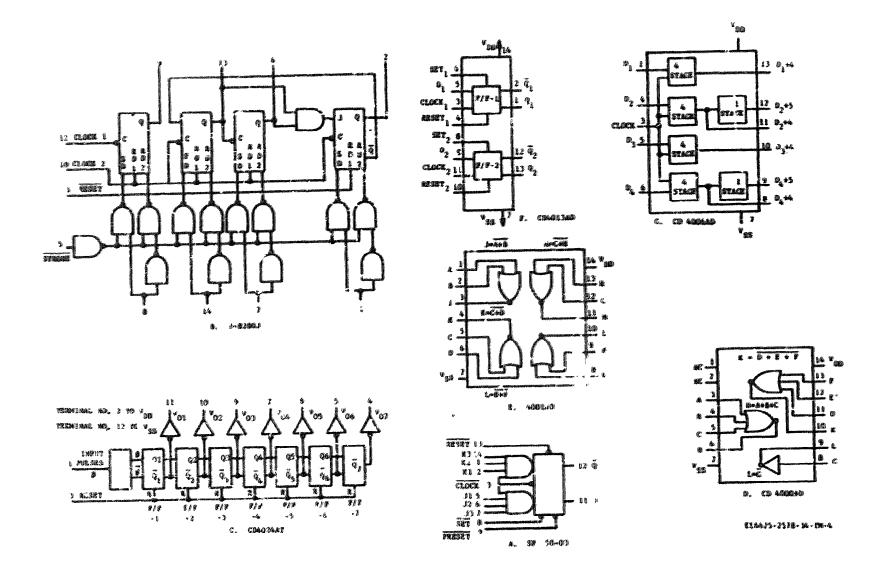

2-5. Symbology and Terminolgy of Complete Integrated Circuits

Internal packaging and pin connection of integrated circuits is shown in figure 2-4.

- a. SF50-03. The SF50-03 (A, fig. 2-4) is an AND input, J-K flip-flop used to divide by two. Unused inputs to the AND gates and DC SET, DC RESET, or DC PRESET are connected to +7.2 vdc. The SF50-03 is used in the 1A1A8 and 1A1A10 modules.

- b. S-8280J. The S-2820J (B, fig. 2-4) is a decade counter connected in the BCD counting mode and is used in the 1A1A8 module. The counter has a strobed parallel-entry capability so that the counter may be preset to any desired output state. A logic one or logic zero will be transferred to the associated output when the strobe input is a logic zero. A logic zero at the reset input produces a logic zero at each output. The counting operation is performed on the falling (negative going) edge of the input clock pulse.

- c. CD-4024AT. The CD-4024AT (C, fig. 2-4) is a seven-stage binary counter with a pulse shaper input stage. A high level at reset causes Q output of all stages to go low. The counter advances one binary count on each negative going transition at the input, pin 1.

- d. CD4000AD The CD-4000AD (D, fig. 2-4) is a dual 3 input NOR gate, single inverter IC.

- e. CD-4001AD. The CD-4001AD (E, fig. 2-4) is a quad 2 input NOR gate IC which is used in several modules.

- f. CD-4013AD. The CD-4013AD (F, fig. 2-4) is a dual D flip-flop with SET/RESET IC used in several modules. The CD-4003AD is identical to the CD-4013AD except that there is no SET(s) input on a CD-4903AD. Therefore, the CD-4003AD may be used in place of the CD-4013AD if a SET input is not required.

- g. CD-4006D. The CD-4006D (G, fig. 2-4) is an 18-stage shift register. Data is shifted through each register stage on the negative going edge of a clock pulse.

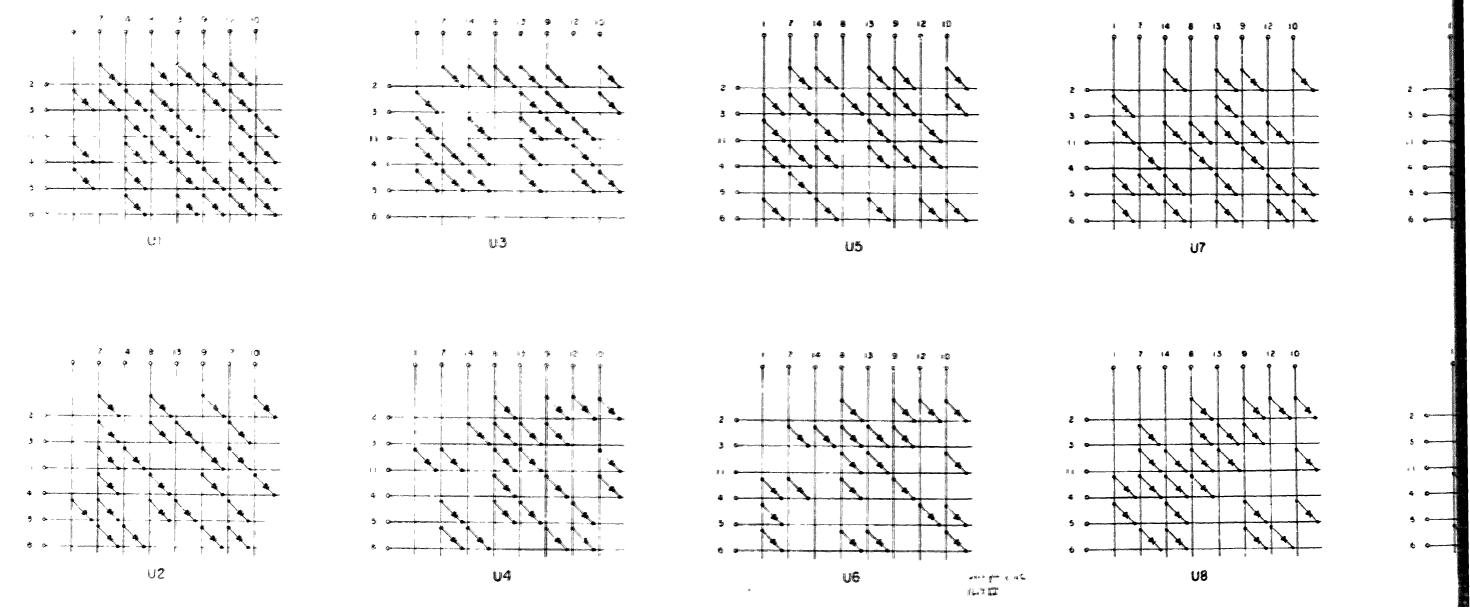

- h. Diode Matrices. Diode matrices, part numper 8141, have some of their internal fusiblelink diodes intentionally blown out. These matrices are shown on individual schematic diagrams as they actually are.

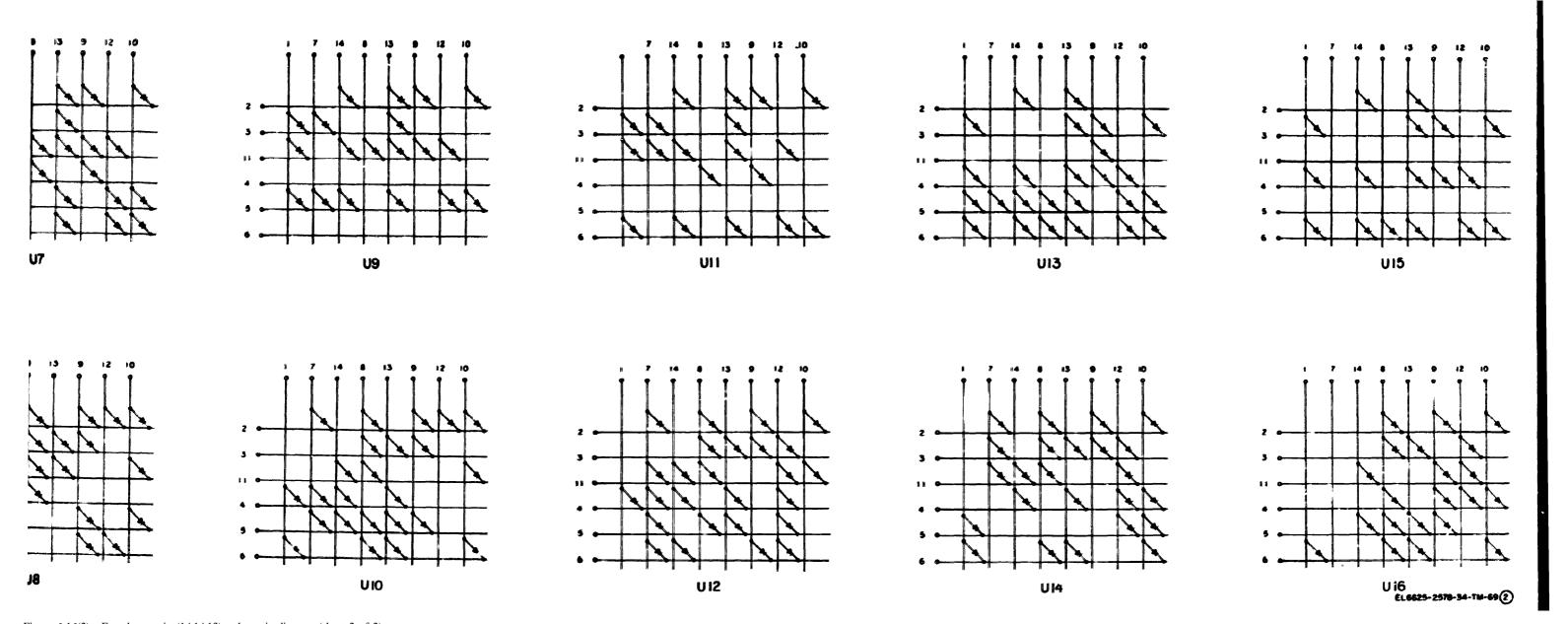

Figure 2-4. Integrated circuits logic diagram.

2-5

#### Section III. GENERAL FUNCTIONING OF SECTIONS

#### 2-6. General

Refer to the partial schematic or block diagrams referenced in the text and the overall block diagram (fig. 6-2), to aid in understanding the general functional description of sections and modules.

#### 2-7. Program Generator

- a. The program generator section is comprised of the following modules which are described below:

- (1) Mode Control I 1A1A6

- (2) Mode Control II 1A1A8

- (3) Word Length Generator 1A1A9

- (4) Mode Control III 1A1A11

- (5) Encoder I 1A1A12

- (6) Encoder Matrix 1A1A13

- (7) Encoder II 1A1A14

- (8) Shift Register 1A1A15

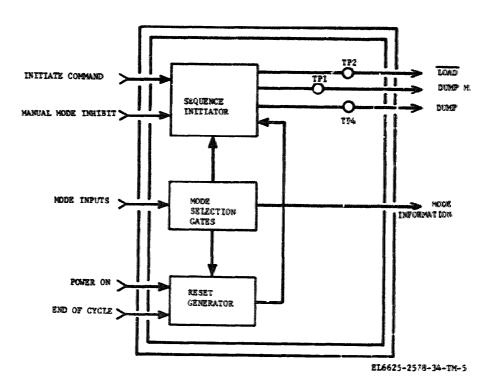

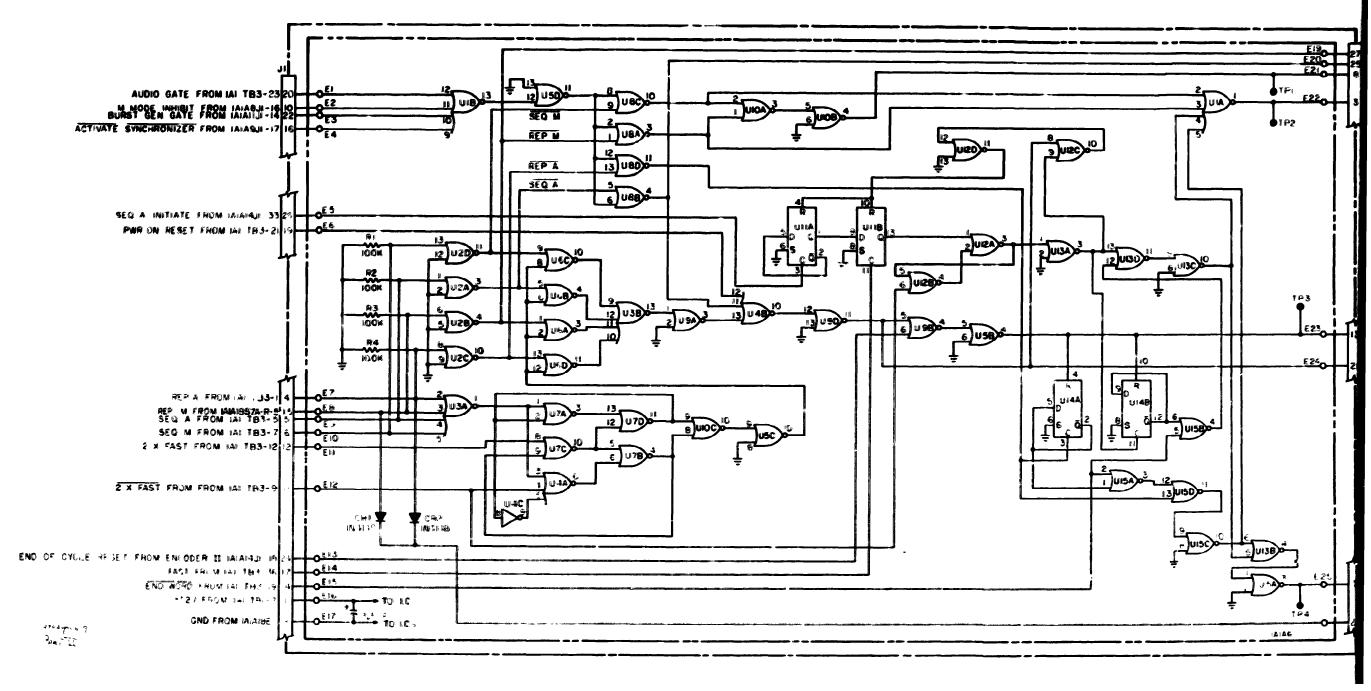

- b. Mode Control I (fig. 2-5).

- (1) Mode control I receives information

- from the front panel MODE switch (S7) which determines if the type of operation is  $\omega$  be sequential or repetitive, manual, or automatic. If the manual mode is selected, this information is decoded by the mode selection gates and applied to the sequence initiator, requiring that the START button be pressed once for every word generated. Had the automatic mode been selected, the sequence initiator would have continued to generate the necessary word start signals until the complete 64-word sequence had been achieved.

- (2) The automatic mode may be interrupted or inhibited by several conditions. Power turn-on or interruption will inhibit the sequence initiator until the proper reset functions have been accomplished; pressing the START button inhibits the sequence initiator and causes the reset generator to put out a pulse (TP3) which, in turn, restarts the sequential cycle. Mode change also causes a restart resulting in initiation of the first sequential word.

- (3) Mode selection information from the mode selection gates is also passed on to Mode Control III (1A1A11).

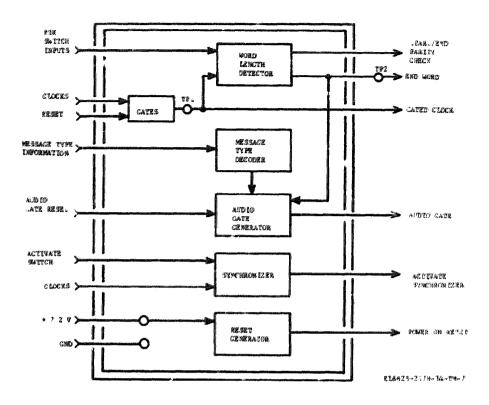

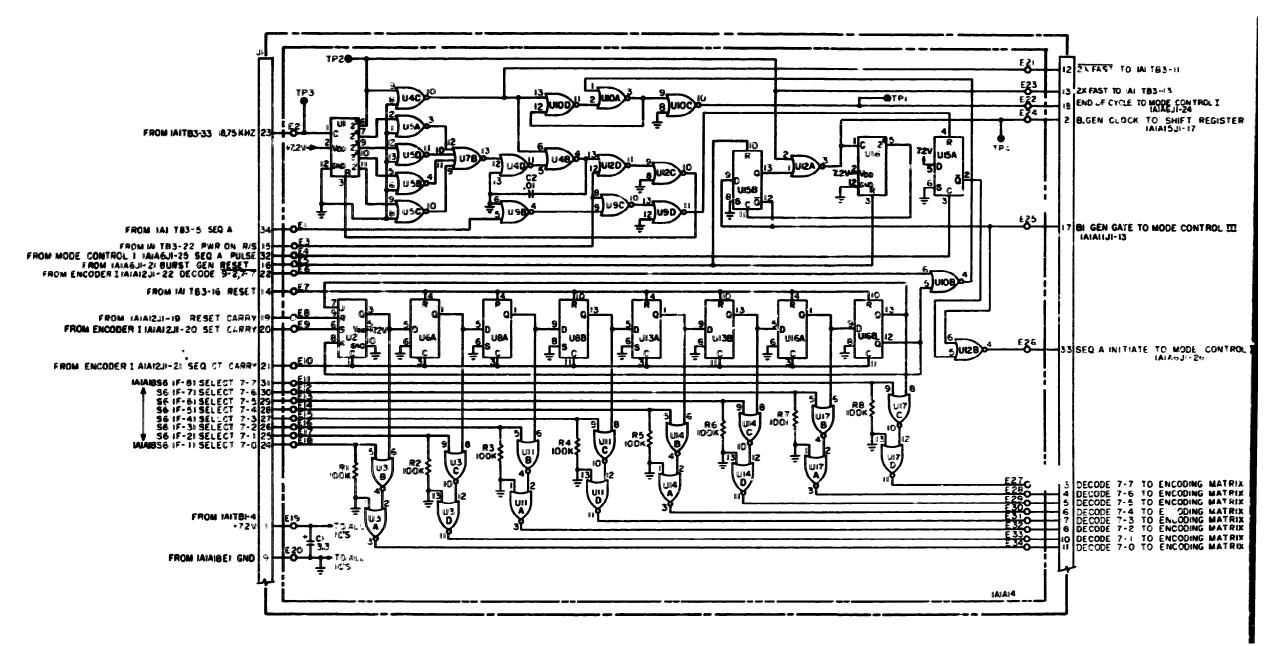

Figure 2-5. Mode control I, simplified block diagram.

Figure 2-6. Mode control II, simplified block diagram.

#### c. Mode Control II (fig. 2-6).

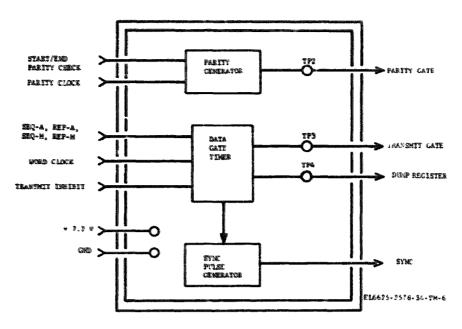

- (1) The Mode Control II module performs two basic functions, parity bit control and recycle time regulation. The parity generator receives start and end parity check commands from the Word Length Generator (1A1A9). The commands and a parity clock from the Shift Register (1A1A15) produce a parity gate (TP2). This parity gate will insert the proper bit in the message to assure correct parity.

- (2) The delay between successive messages must be controlled in order to prevent command overlap, eliminate the effects of any possible switch bounce, and to provide enough time for proper message reception by the AN/USQ-46 or AN/USQ-46A. The data gate timer determines this delay by conspining mode information from the front panel with a word clock pulse. If a transmit inhibit signal is not present, a dump register (TP4) and a transmit gate (TP3) signal, in the correct time sequence to begin a message, is provided as outputs. In the manual mode, the word is transmitted as soon as the START button is pressed and a 0.5-second delay time follows the end of the message. A new message cannot begin until this delay has elapsed. In the automatic mode, a 1-second delay time commences when the START button is pressed, and after this delay, the word is transmitted. At the end of the word, another 1-second delay is instituted before the transmission of the next word. The delayed reset pulse may be seen at TP1.

- (3) A: auxiliary function of the Mode Control II module is the development of the sync pulse to the front panel SYNC Connector, 1A1-A18J4.

- d. Word Length Generator (fig. 2-7).

- (1) The Word Length Generator has four basic functions, one of which is to generate a pulse when power is turned on. The reset generator provides a POWER ON RESET pulse of approximately 50 msec in duration and outputs this signal to the Encoder II module (1A1A14), the Mode Control I module (1A1A6) and Mode Control III module (1A1A11).

- (2) When the 5rART button on the front panel is pressed, the synchronizer gates this information along with the clock input in order to produce an activate synchronizer pulse which is synchronous with all internally generated clocks.

- (3) Should a type 3 message be desired, the message type decoder will determine this from the front panel switch positions and send this information to the audio gate generator. The 0.5-second delay which would normally follow the end of a manual word is inhibited to permit a 20.5-second audio gate to be delivered to the VCXO (1A1A1).

- (4) The word length detector will detect the start parity check and end parity check points by performing a count of its gated clock inputs (TP1) and will also output an end word signal (TP2) when the 18 or 24 message bits

Figure 2-7. Word length generator, simplified block diagram.

have been completed (determined by message type).

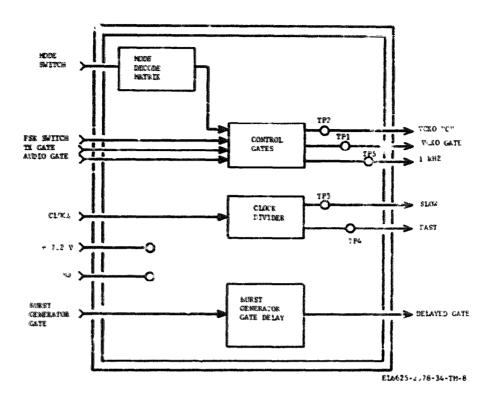

- e. Mode Control III (fg. 2-8).

- (1) An input clock from the Encoder II module (1A1A14) is received by the clock divider circuit which ther divides the clocks into two frequencies; slow (75 Hz), and fast (300 Hz). These clocks are utilized by modules 1A1A6, 1A1A8, 1A1A9, and 1A1A12.

- (2) The burst generator gate signal from Encoder II module (1A1A14) is delayed by the burst generator gate delay circuit in order to prevent a premature command initiation. This signal goes to the Mode Control I module (1A1-A6).

- (3) Information from the front panel mode switches is used by the mode decode matrix along with FSK switch information, to dotermine the proper time sequence for the VCXO GATE (TP1) and the 1 kHz GATE (TP5). The control gates also determine the modulation frequency applied to the VCXO (1A1A1) by selecting VCXO B or VCXO C (TP2).

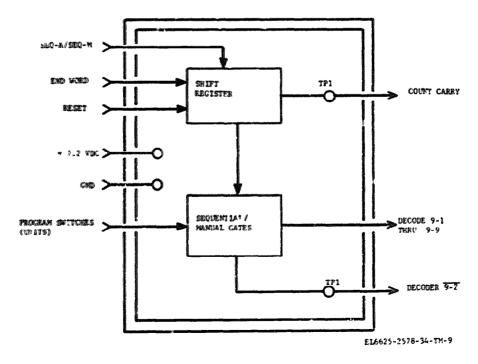

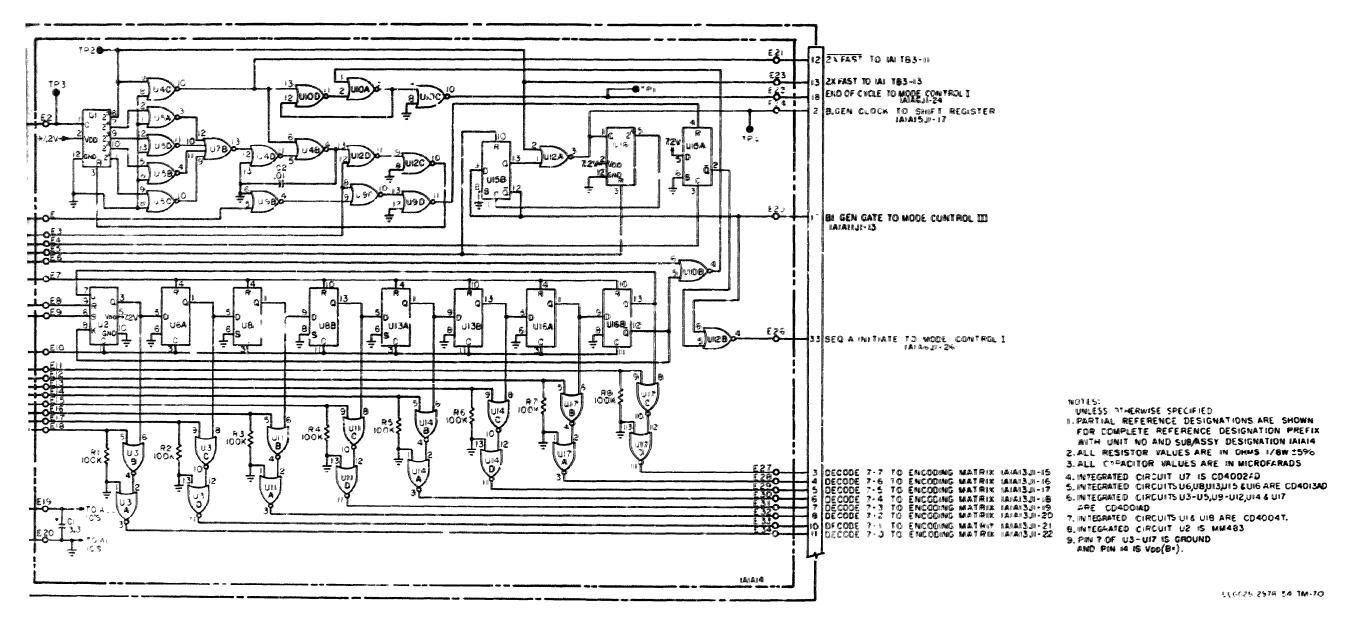

- f. Encoder I (fig. 2-9).

- (1) The function of the Encoder I module

- is to produce an output which is used as the units input to the Encoding Matrix (1A1A13) which in turn will determine what word is \*o be generated.

- (2) Information from the front panes mode switches is utilized by a shift register to determine if a count inhibit signal should be present. If in the repetitive mode, the shift register will be inhibited and the front panel program switch information will be routed through the sequential/manual gates to the Encoding Ma\*rix (1A1A13).

- (3) Should a sequential mode have been selected, the shift register will be advanced with each end word input until a count carry (TPI) is generated to the Encoder II module (1A1A14). This count sequence continues until all 64 words have been transmitted. Then the signal 9-2 and information from the Encoder II module (1A1-A14) will prevent the sequential coding advancement. When in a sequential mode the program switch information of the sequential/manual gates is inhibited and shift register information is sent to the Encoding Matrix (1A1A13).

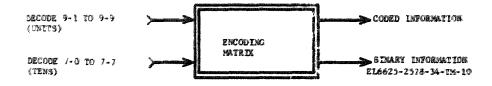

- g. Encoder Matrix (fig. 2-10). The Encoding Matrix, containing two diode matrices, senses and encodes the states of the two encoder regis-

Figure 2-8. Mode control III, simplified block diagram.

Figure 2-9. Encoder I, simplified block diagram.

Figure 2-10. Encoder matrix, simplified block diagram.

Figure 2-11. Encoder II, simplified block diagram.

ters. Encoder 1 (1A1A12) and Encoder II (1A1-A14). One matrix decodes and outputs 6-bit binary information while the other matrix decodes and outputs 6 bit coded information. The code and binary signing are routed to the Shift Register (1A1A15) where they are used to form the transmitted word.

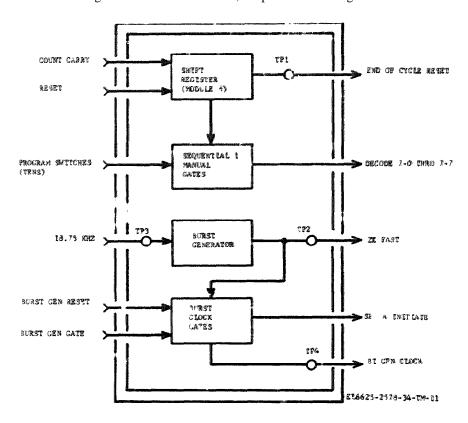

#### h. Encoder II (fig. 2-11).

- (1) Encoder II functions in a manner very similar to that of Facoder I (1A1A12). Encoder I supplies a count carry input to Encoder II while both use the common reset signal. When the complete word sequence has been executed, an end of cycle reset is generated (TP1).

- (2) Information from the shift register is

gated with the program switches inputs (tens) to provide an output to the Encoding Matrix (1A1A13)

- (3) An 18.75 kHz signal (TP3) from the Reference Generator (1A1A10) in the Frequency Synthesizer section, is injected into the burst generator which divides this input down to the 2X Fast frequency (600 Hz, TP2). This signal is then controlled by the burst clock gates to produce a gated clock (TP4) to the Shift Register (1A1A15) and a timed SEQ A INITIATE pulse to Mode Control I module (1A1A6,.

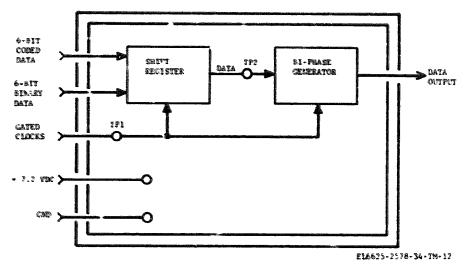

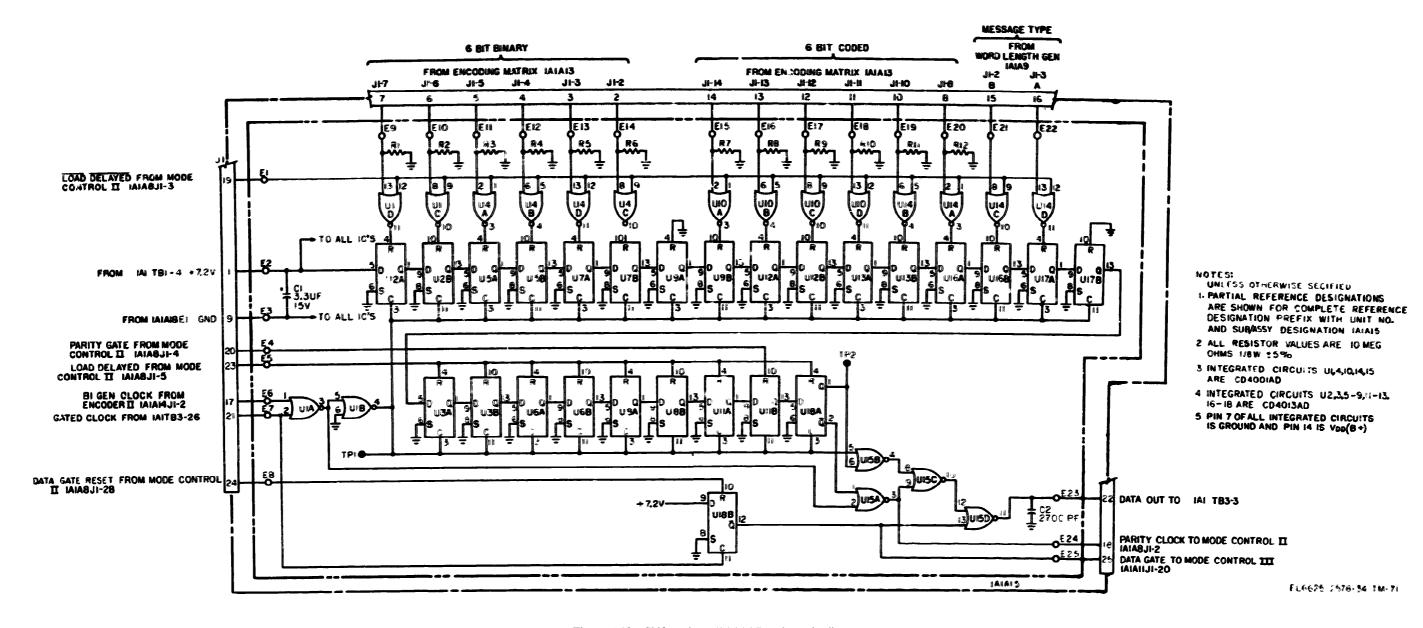

- i. Shift Register (fig. 2-12). The Shift Register receives 6-bit binary data from the Encoding Matrix (1A1A13). When a LOAD DELAYED

Figure 2-12. Shift register, simplified block diagram.

Figure 2-13. VCXO, simplified block diagram.

command is received, this information is loaded into the shift register cells while the first 9 cells are reset by the LOAD DELAY command. When gated clocks are generated (TP1), the information in the shift register is shifted out (TP2) to the biphase generator. The biphase generator converts the input data into Manchester coded data which is applied to the Mode Control III module (1A1A1I).

- 2-8. Modulation Steering and Control Section.

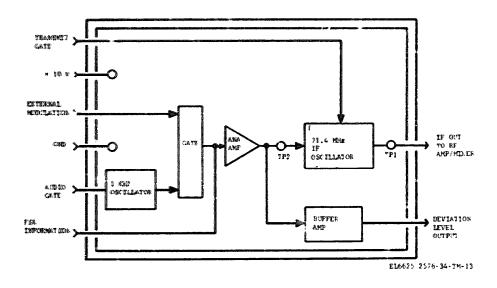

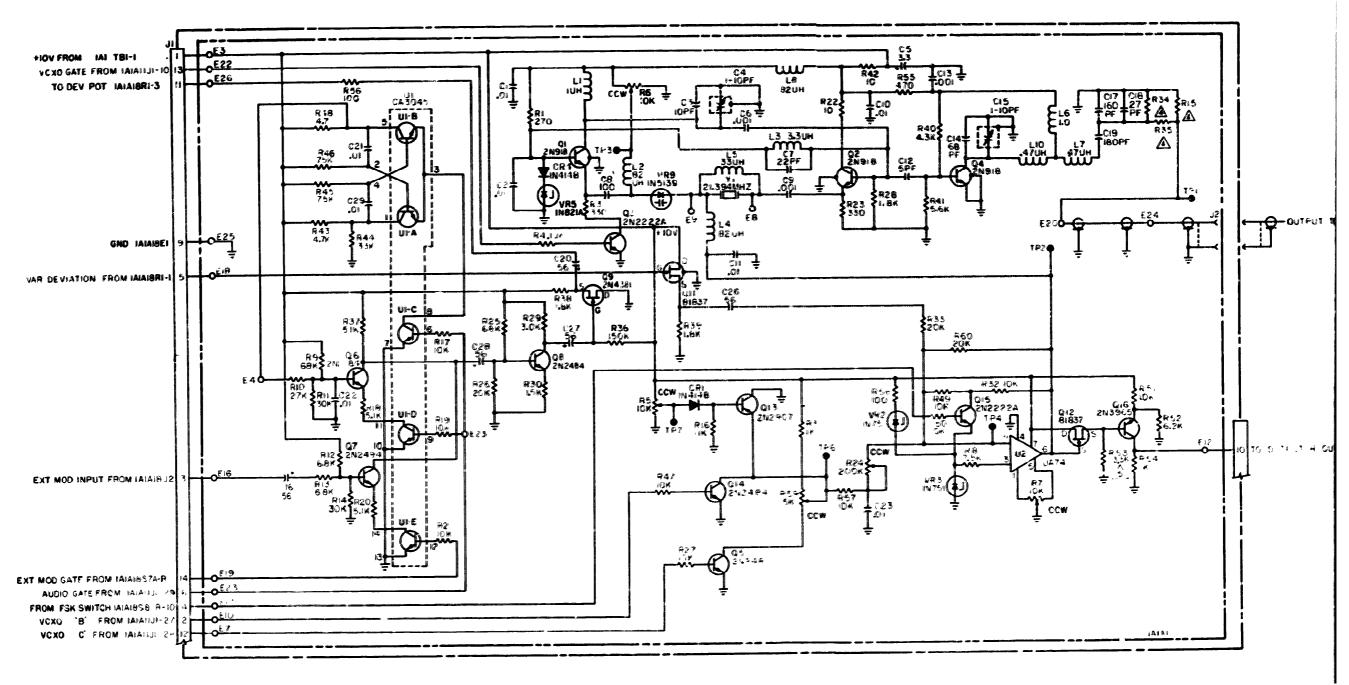

- a. This section is comprised of the Voltage Controlled Crystal Oscillator (VCXO) 1A1A1 (fig. 2-13).

b. The VCXO is the source of the 21.4 MHz carrier frequency (IF). The front panel mode switch has three positions which will affect the modulation of the VCXO and are indicated by the abbreviations CAL (calibrate), INT (internal), and EXT (external). When the MODE switch is in INT a 1 kHz oscillator is enabled which produces the modulation signal during the 1 kHz GATE pulse time. It is possible to provide modulation from an external source by injecting a signal into the front panel EXT MOD IN connector 1A1A18J2 while the MODE switch is in the EXT position. The third switch position (CAL) provides no modulating signal to the IF

oscillator. Therefore, an unmodulated 21.4 MHz signal will be seen at TP1. The internal or external modulations signals are gated with FSK information to the analog amplifier. The output of the analog amplifier at TP2 is the modulation signal to be used by the IF oscillator. Presence of the VCXO GATE is required to turn on the IF oscillator.

#### 2-9. Frequency Synthesizer Section

- a. This section is comprised of the following modules which are described below:

- (1) Temperature Compensated Crystal Oscillator (TCXO) 1A1A16

- (2) Reference Generator 1A1A10

- (3) Synthesizer Mixer 1A1A4

- (4) Programable Divider 1A1A5

- (5) Loop Filter/VCO 1A1A3

- b. The Temperature Compensated Crystal Oscillator generates an output of 3.75 MHz with ±1 ppm stability over its entire input voltage range of 10-16 vdc. The 3.75 MHz signal may be monitored at TP2 of the Reference Generator module (1A1A10).

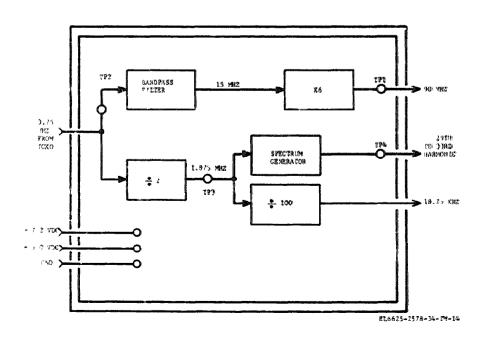

- c. Reference Generator (fig. 2-14).

- (1) The Reference Generator receives a 3.75 MHz input from the TCXO (1A1A6) and

- produces three outputs. The 3.75 MHz input is fed to a bandpass filter which selects the fourth harmonic of 3.75 MHz, or 15 MHz at its output. This 15-MHz signal then goes through a times six multiplier stage to produce 90 MHz at its output (TP1). This 90 MHz is applied to the Synthesizer/Mixer module (1A1A4).

- (2) The 3.75 MHz input (TP2) also goes to a divide-by-two-circuit whose output of 1.875 MHz (TP3) is then used by two circuits. One of these circuits is a divide-by-100 device which will produce a final output of 18.75 kHz to be used by the Programable Divider module (1A1A5).

- (3) The spectrum generator also receives the 1.875-MHz square wave input and transforms this into a spectrum output to the Synthesizer/Mixer module (1A1A4). The filters in the Synthesizer/Mixer will utilize the 25th to 33rd harmonics of the spectrum output (TP4).

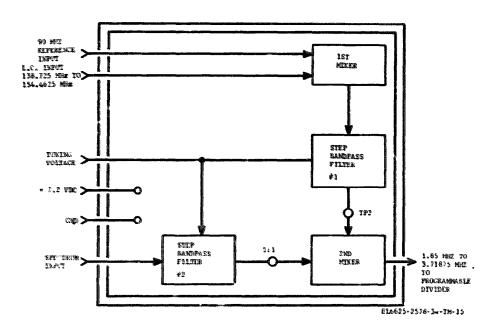

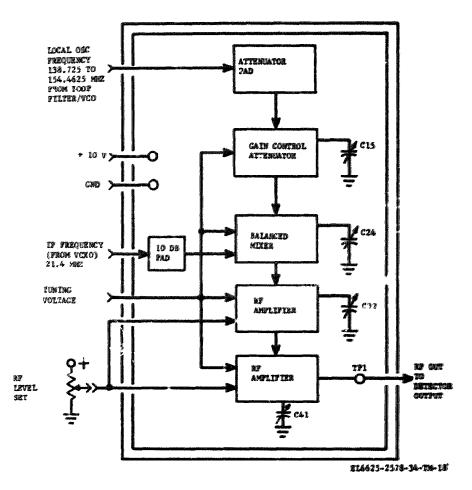

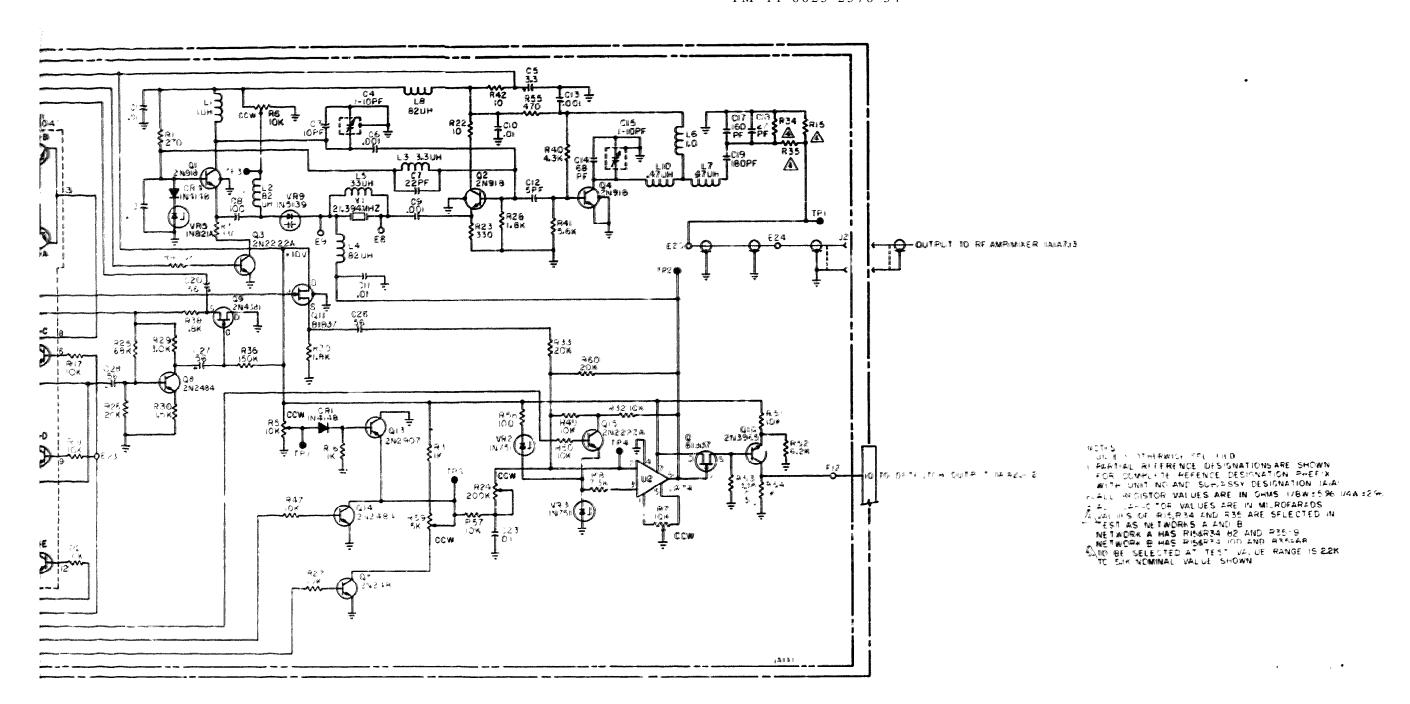

#### d. Synthesizer Mixer (fig. 2-15).

- (1) The Synthesizer/Mixer mixes input frequencies from the Reference Generator (1A1A10) with the LO frequency from the Loop Filter/VCO (1A1A3) and, in conjunction with a tuning voltage from the RF CHANNEL NUMBER switches, produces an output clock frequency for use by the Programable Divider (1A1A5).

- (2) The first mixer mixes 90 MHz from the Reference Generator with the LO frequency

Figure 2-14. Reference generator, simplified block diagram.

Figure 2-15. Synthesizer mixer, simplified block diagram.

(138.725 to 154.4625 MHz) to produce a difference frequency (48.725 to 64.4625 MHz) at its output. This output goes to the step bandpass filter one which uses the tuning voltage input to select the proper output frequency.

- (3) Step bandpass filter two uses the spectrum output (25th to 33rd harmonic) from the Reference Generator, along with tuning voltage to select an output frequency (46.875 to 61.875 MHz).

- (4) The outputs from bandpass filter one and bandpass filter two are mixed by the second mixer to produce an output which may range from 1,85 to 3.71875 MHz according to the RF channel number selected. The outputs of bandpass filters one and two may be monitored at test points TP2 and TP1 respectively.

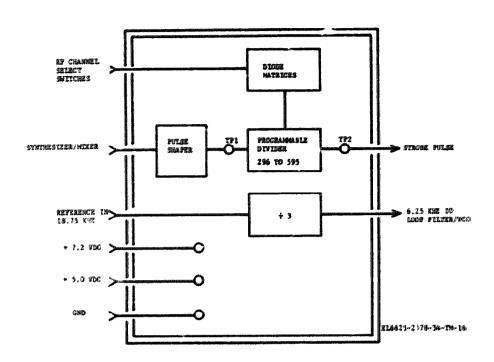

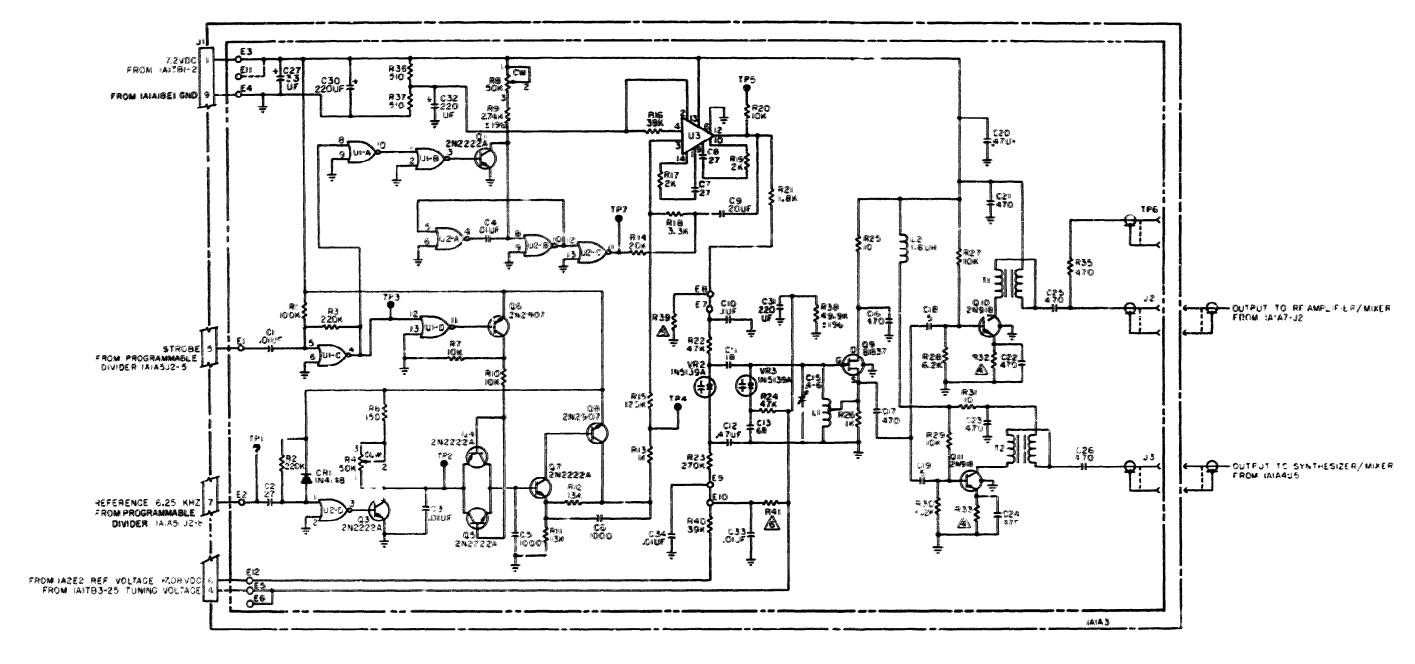

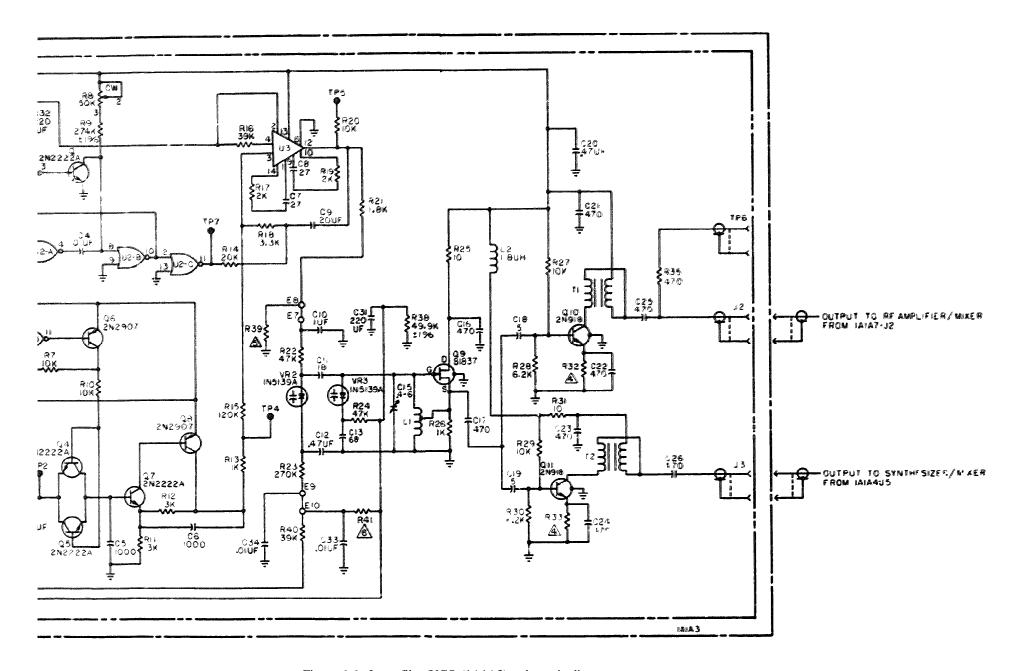

#### e. Programable Divider (fig. 2-16).

(1) The Programable Divider module receives the analog signal output from the Synthesizer/Mixer (1A1A4) second mixer and passes it through a pulse shaper. This enables the signal at TP1 to have a clocking edge transition time adequate to properly clock the programable divider. Information from the front panel RF CHANNEL SELECT switches is decoded by the diode matrices and is then used to preset the programable divider so that any count between

296 and 595 may be obtained. The strobe pulse (TP2) from the programable divider is used by the Loop Filter/VCO module (1A1A3).

(2) The 18.75 kHz from the Reference Generator (1A1A10) is divided by three and the resultant 6.25 kHz signal is routed to the Loop Filter/VCO.

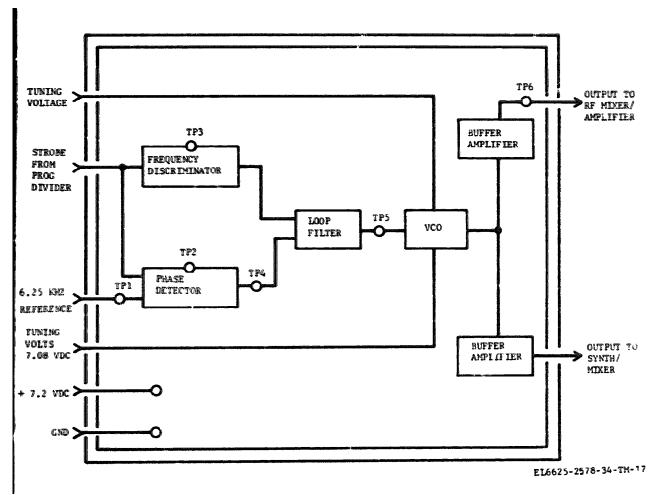

#### f. Loop Filter/VCO (fig. 2-17).

- (1) The strobe pulse and 6.25-kHz reference frequency inputs to the Loop Filter/VCO permit the frequency discriminator, phase detector and loop filter to generate an error voltage to the VCO. The output from the VCO (LO frequency) is then used to modify the frequency synthesizer circuits in such a manner as to become self-correcting for frequency stability.