# TM 11-6625-620-45-2

DEPARTMENT OF THE ARMY TECHNICAL MANUAL

## GENERAL SUPPORT AND DEPOT MAINTENANCE MANUAL

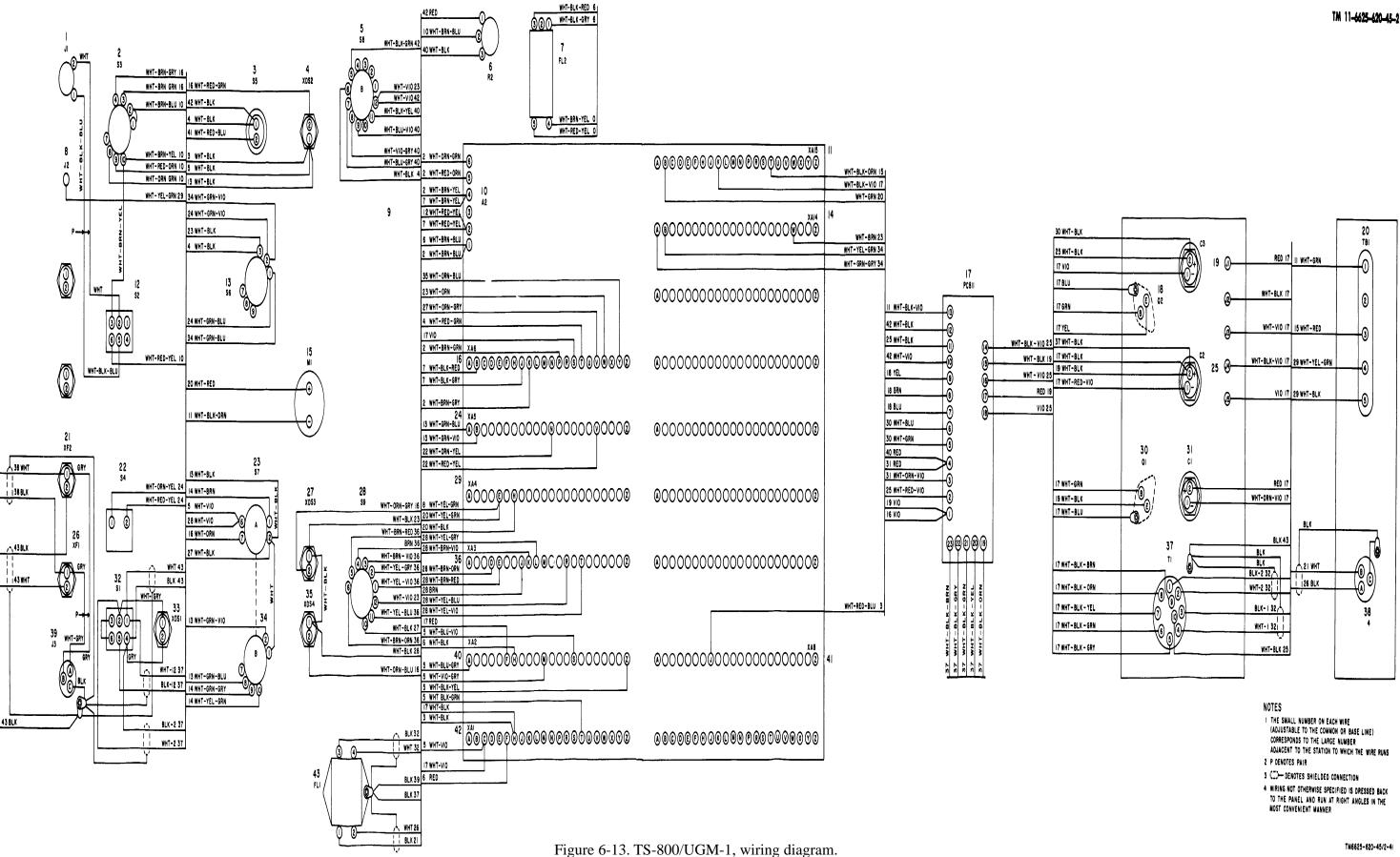

## TEST SET, TELETYPEWRITER TS-800/UGM-1

This copy is a reprint which includes current Pages from Changes 1 and 2

HEADQUARTERS, DEPARTMENT OF THE ARMY 14 MARCH 1968

#### WARNING

#### DANGEROUS VOLTAGES EXIST IN THIS EQUIPMENT

Be caraful when working on or near the 115 or 230—volt ac line connetions. Serious injury or DEATH may result from contact with these ter**minals**.

#### **DON'T TAKE CHANCES!**

Change

No. 2

HEADQUARTERS DEPARTMENT OF THE ARMY Washington, DC, 1 August 1986

#### General Support and Depot Maintenance Manual TEST SET, TELETYPEWRITER TS-800/UGM- 1 (NSN 6625-00-965-0197)

TM 11-6625-620-45-2, 14 March 1968, is changed as follows:

1. Title of manual is changed as shown above.

2. Remove old pages and insert new pages as indicated below. New or changed material is indicated by a vertical bar in the margin of the page. Added or revised illustrations are indicated by a vertical bar adjacent to the identification number.

| Remove pages | Insert pages    |

|--------------|-----------------|

| None         |                 |

| i            | i/(ii blank)    |

| 1-1and 1-2   | 1-1and 1-2      |

| 3-1 and 3-2  |                 |

| 4-1and 4-2   |                 |

| 4-7 and 4-8  |                 |

| 6-11         |                 |

| 6-23         |                 |

| A-1          | A-1/(A-2 blank) |

3. File this change sheet in the front of the publication for reference purposes.

This publication Is required for official use or for administrative or operational purposes only. Distribution is limited to US Government Agencies. Other requests for the document must be referred to Commander, US Army Communication-Electronics Command and Fort Monmouth, ATTN: AMSEL-ME-P, fort Monmouth, NJ 07703-5007. By Order of the Secretary of the Army:

JOHN A. WICKHAM JR. General, United States Army Chief of Staff

Official:

R. L. DILWORTH Brigadier General, United States Army The Adjutant General

DISTRIBUTION:

To be distributed in accordance with DA Form 12-36 literature requirements for TS-8000/UGM-1.

#### WARNING

#### DANGEROUS VOLTAGES EXIST IN THIS EQUIPMENT

Be careful when working on or near the 115- or 230-volt ac line connections. Serious injury or DEATH may result from contact with these terminals.

#### WARNING

When troubleshooting or making repairs on this equipment be extremely careful. Voltages as high as 230V are present in the test set. Use insulated test probes when making voltage measurements. Always disconnect the power cords before touching any internal parts.

#### CAUTION

Use extreme care when performing maintenance of the printed circuit boards.

#### CAUTION

Make sure that the power cable is never connected to a 230 volt ac source with the POWER switch locking guard permitting the POWER switch to be set to the 115 volt position. Setting the POWER switch to the 115 volt position with equipment connected to a 230 volt source can damage the equipment.

#### CAUTION

Do not make resistance measurements on the distortion analyzer unless specifically directed to do so. The battery voltage of an ohmmeter can damage the transistors.

Change 2 A/(B blank)

TECHNICAL MANUAL

No. 11-6625-620-45-2

HEADQUARTERS DEPARTMENT OF THE ARMY WASHINGTON, D. C., 14 March 1968

#### General Support and Depot Maintenance Manual

#### TEST SET, TELETYPEWRITER TS-800/UGM-1

#### (NSN 6625-00-965-0197)

#### REPORTING ERRORS AND RECOMMENDING IMPROVEMENTS

You can help improve this manual. If you find any mistakes or if you know of a way to improve the procedures, please let us know. Mail your letter or DA Form 2028 (Recommended Changes to Publications and Blank Forms) direct to: Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: AMSEL-ME-MP, Fort Monmouth, NJ 07703-5007. In either case, a reply will be furnished direct to you.

| Paragrapl                                                                    | n Page       |

|------------------------------------------------------------------------------|--------------|

| CHAPTER 1. FUNCTIONING OF EQUIPMENT                                          |              |

| Section I. General 1-1, 1-2                                                  | 2 1-1        |

| II. Unit functioning 1-3, 1-4                                                | 1-1          |

| III. Circuit analysis and logic symbols 1-5-1-4                              | 4 1-7-1-16   |

| III. Circuit analysis and logic symbols 1-5-1-<br>IV. Logic analysis 1-15-1- | 24 1-18-1-31 |

| CHAPTER 2. TROUBLESHOOTING                                                   |              |

| Section I. General troubleshooting information 2-1-2-3                       | 3 2-1        |

| II. Troublshooting procedures 2-4-2-                                         | 9 2-2-2-41   |

| CHAPTER 3. ADJUSTMENT PROCEDURES 3-1-3-4                                     | 4 3-1-3-2    |

| 4. GENERAL SUPPORT TESTING PROCEDURES 4-1-4-                                 | 9 4-1-4-8    |

| 5. DEPOT MAINTENANCE 5-1, 5-                                                 | 2 5-1        |

| 6. DEPOT OVERHAUL STANDARDS 6-1-6-                                           | 3 6-1        |

| APPENDIX REFERENCES                                                          | A-1          |

| INDEX                                                                        |              |

Change 2 i/(ii b

i/(ii blank)

<sup>\*</sup>This manual supersedes TM 11-6625-620-45-2, 6 December 1966.

#### **CHAPTER 1 INTRODUCTION**

#### Section I. GENERAL

#### 1-1. Scope

a. This manual contains general support and depot maintenance instructions for Test Set, Teletypewriter TS-800/UGM-1. It includes instructions appropriate to general support and depot maintenance personnel for troubleshooting, testing and repairing the equipment. It also lists tools, materials, and test equipment required for general support and depot maintenance. Functional analysis of the equipment is also covered.

b. The complete technical manual for this equipment includes TM 11-6625-620-12 and TM 11-6625-620-25P-2.

#### **1-2. Consolidated Index of Army Publications** end Blank Forms

Refer to the latest issue of DA Pam 310-1 to determine whether there are new editions, changes or additional publications pertaining to the equipment.

#### 1-2.1. Maintenance Forms, Records and Reports

a. Reports of Maintenance and Unsatisfac-tory Equipment. Department of the Army forms and procedures used for equipment maintenance will be those prescribed by DA Pam 738-750 as contained in Maintenance Management Update.

b. Report of Packaging and Handling Deficiencies. Fill out and forward SF 364 (Report of

#### Section II. UNIT FUNCTIONING

#### 1-3. General

Test Set, Teletypewriter TS-800/UGM-1 (distortion analyzer) provides a direct-reading, panel-meter indication of the amount of distortion present in a start-stop telegraph signal. It compares the position of the input signal transitions to an accurate time-base signal that is generated in the time-base circuits, and indicates whether the signal transitions are occurring at the correct time, early, or late. The EARLY lamp lights to indicate when the transitions are early; the LATE lamp lights to indicate when the transitions are late. The time-base circuits synchronize the timebase signal (reference) with the mark-to-space transition of the stop-mark and start-space. The distortion analyzer also compares the succeeding mark-to-space or space-to-mark transitions of the Discrepancy (ROD)) as prescribed in AR 735-11-2/DLAR 4140.55/NAVMATINST 4355.73A/AFR 400-54/MCO 4430.3H.

c. Discrepancy in Shipment Report (DISREP) (SF 361). Fill out and forward Discrepancy in Shipment Report (DISREP) (SF 361) as prescribed in AR 55-38/NAVSUPINST 4610.33C/AFR 75-18/ MCO P4610.19D DLAR 4500.15.

#### **1-2.2. Destruction of Army Materiel To Prevent Enemy Use**

Refer to TM 750-244-2 for procedures to be used for this equipment.

#### 1-2.3. Administrative Storage

Refer to TM 760-90-1 for procedures to be used when equipment is to be placed in administrative storage.

#### 1-2.4. Reporting Equipment Improvement Recom-

#### mendations (EIR)

If your equipment needs improvement, let us know. Send us an EIR. You, the user, are the only one who can tell us what you don't like about the design. Put it on an SF 368 (Quality Deficiency Report). Mail it to: Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: AMSEL-PA-MA-D, Fort Monmouth, New Jersey 07703-5023. We'll send you a reply.

input signal to this reference. The displacement of the telegraph-signal transitions with respect to the reference is directly indicated as a percent distortion indication on the PERCENT DISTOR-TION meter.

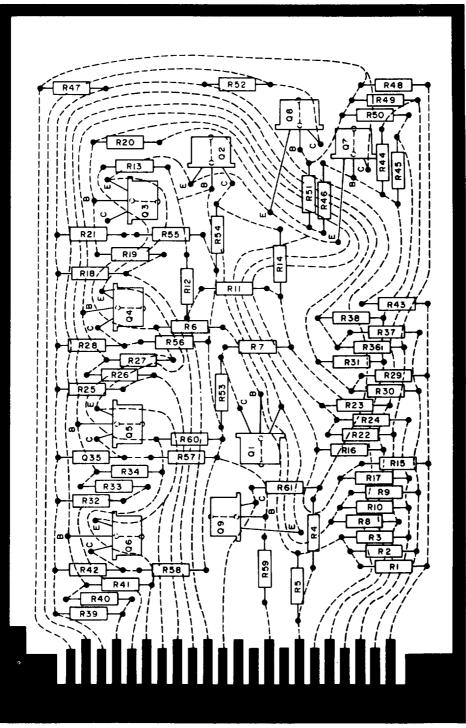

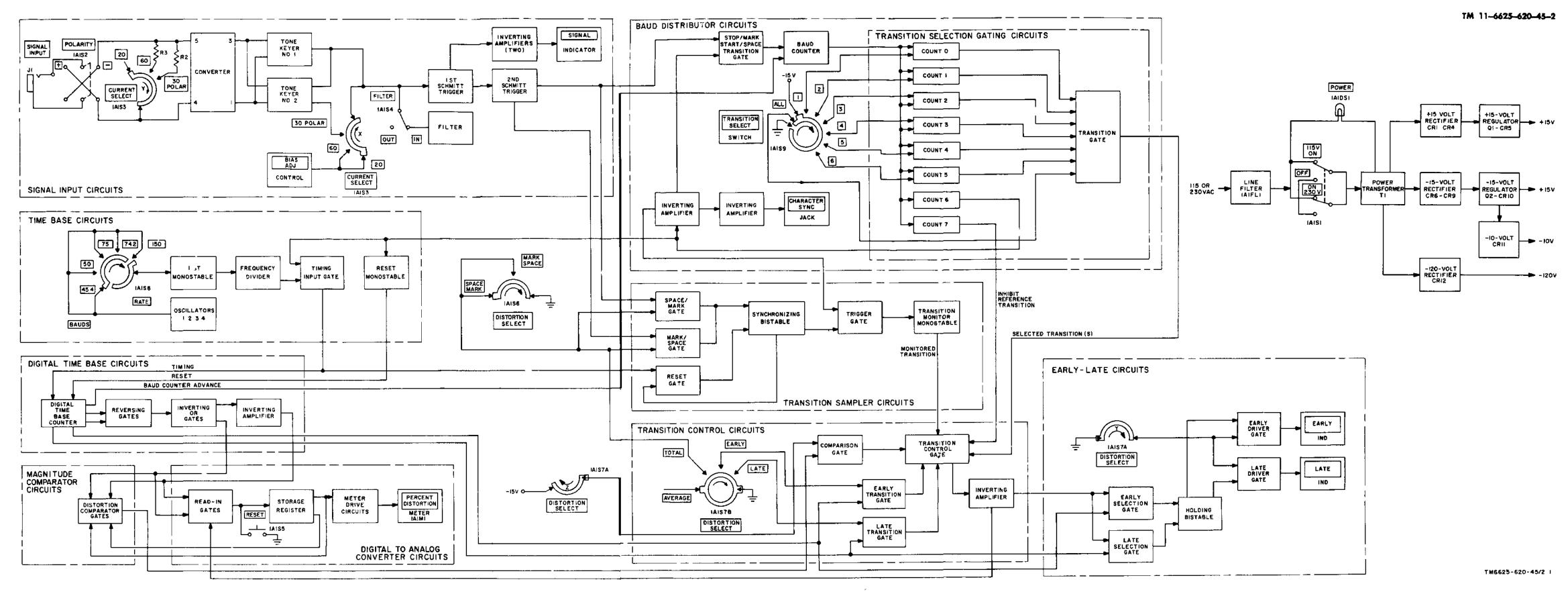

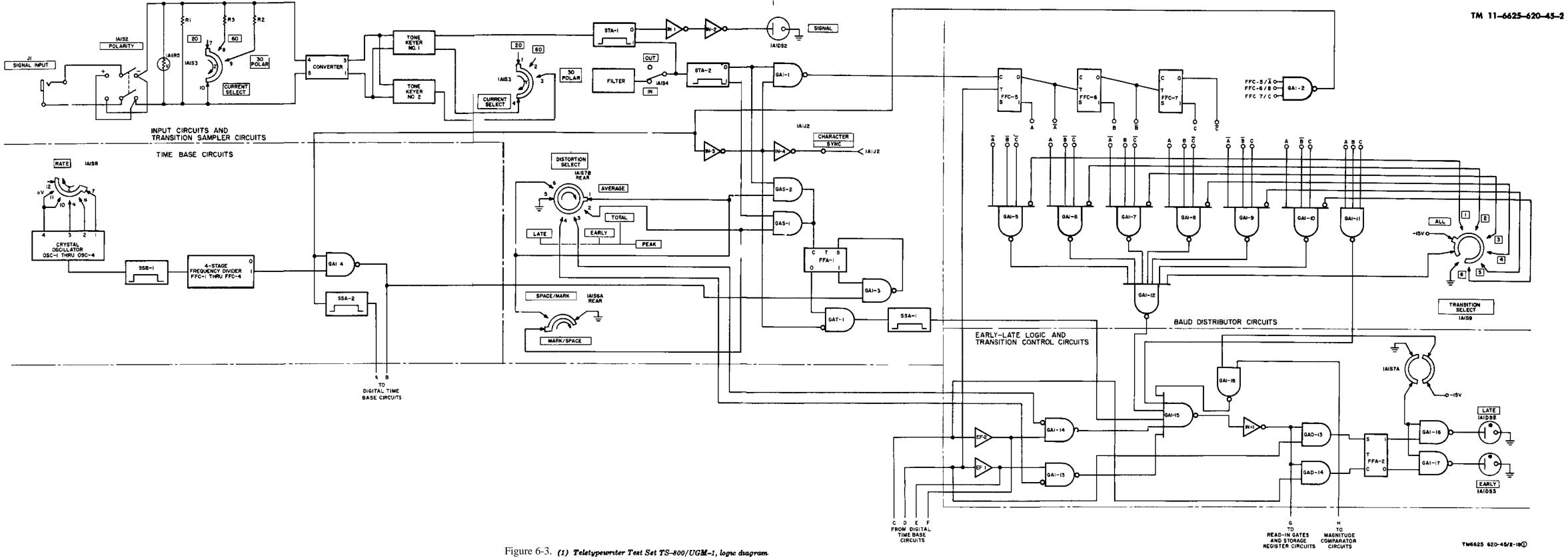

#### 1-4. Block Diagram Analysis

(fig. 6-2)

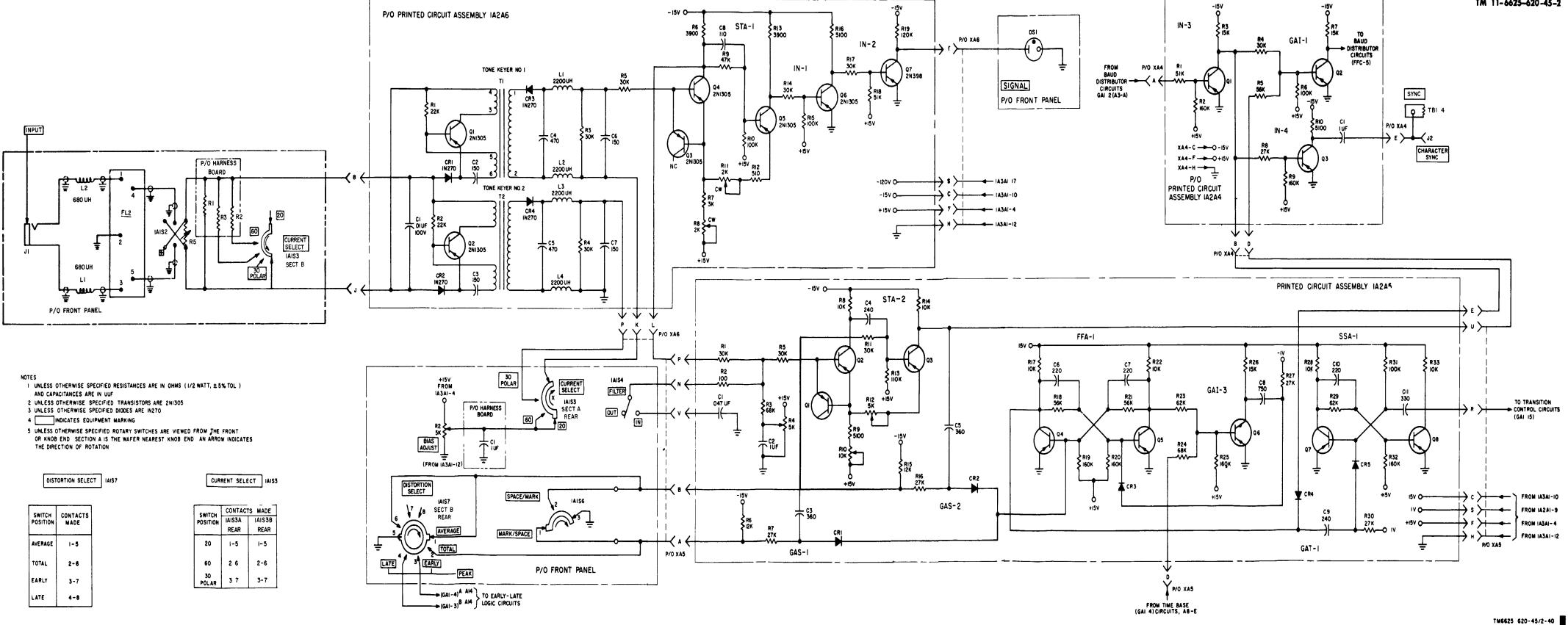

a. Signal-Input Circuits. The signal-input circuits accept either neutral or polar telegraph signals for distortion analysis.

(1) Neutral or polar telegraph signals are applied to neutral and polar marking tone keyer No. 1 or to polar spacing tone keyer No. 2, as applicable, through POLARITY switch 1A1S2, CURRENT SELECT switch 1A1S3, and a noiseand interference-rejecting filter assembly. The output from the tone keyers is applied to the first Schmitt trigger. When the FILTER switch is set to IN, an internal filter is connected to the input of the first Schmitt trigger which filters out any noise, spikes, or holes in the input signal that could cause erratic indications on the PERCENT DISTORTION meter.

(2) The output of the first Schmitt trigger is applied to the SIGNAL indicator lamp through two inverting amplifiers and also to a second Schmitt trigger. If the input signal to the distortion analyzer is in a marking state, the SIGNAL lamp lights.

(3) The output of the second Schmitt trigger is applied to the baud counter (i below) through the stop-mark and start-space transition gates. The second Schmitt trigger output is also applied to the synchronizing bistable through the mark-space and space-mark gates in the transition sampler circuits (f below).

*b. Time-Base Circuits.* A timing input signal from one of the four oscillators is selected by the RATE switch. The timing input signal is then shaped by the first monostable multivibrator and is applied to the frequency divider. The output of the frequency divider, which is 126 times the baud frequency, is applied to the timing input gate in order to control the timing signal applied to the digital time base counter (c below). A signal from the reset monostable is also applied to the digital time-base counter during the stop-mark as a set pulse.

*c.* Digital *Time-Base Circuits.* The digital timebase circuits include the digital time-base counter, reversing gates, inverting OR gates, and an inverting amplifier. (1) An output from the timing input gate in the time-base circuits is applied to the digital time-base counter to produce four signals as follows:

(a) A seven-digit running binary that counts from 0 to 127 for the length of a character, during each ideal bit, except during a stop-mark when it counts from 0 to 63 (only 1/2 bit of the stop-mark).

(b) A six-digit reversible running binary that counts from 0 to 63 and 63 to 0 during each ideal bit except during a stop-mark.

(c) An early pulse during the 1/2-bit period (63 to 0 count) preceding each ideal transition time (except for the stop-mark/start-space transition), and a late pulse during the 1/2-bit period (0 to 63 count) following each ideal transition time.

(d) A pulse 1/2-bit after the stop-mark/stopspace transition, and a pulse every 128 counts for the length *of* the character which advances the baud counter.

(2) An output from the last stage in the digital time-base counter is applied to the baud counter advance (i below). Other outputs are applied to the early transition gate and the late transition gate of the transition control circuits (g below), and to the early selection gate and late selection gate of the early-late circuits (h below). The first six stages of the seven-stage binary digital time-base counter provide a 0 to 63 and 63 to 0 count through the reversing gates, inverting OR gates, and inverting amplifier, to the distortion comparator gates of the magnitude comparator circuits (d below), and the read-in gates of the digital-toanalog converter circuits (e below). The direction of the count (0 to 63 and 63 to 0) is controlled by the reversing gates.

*d. Magnitude Comparator Circuits.* The magnitude comparator circuits compare the instantaneous output of the first six stages of the digital time-base counter with the number stored in the storage register of the digital-to-analog converter circuits (e below).

- (1) After the distortion comparator gates compare the number with the one stored in the storage register, it is transferred to the transition control gate through the comparison gate. When DISTORTION SELECT switch 1A1S7 is set to one of the PEAK positions, and the count in the first six stages of the digital time-base counter is less than the number held in the storage register, the comparison gate is inhibited. This inhibits the transition control gate and the output of the inverting amplifier, and prevents the digital time-base output number from being read into the storage register. In this way, only the highest distortion measurement is held in the storage register when measuring peak distortion.

- (2) Momentarily depressing the RESET switch will reset the storage register to binary 000000. When the RESET switch is released, the number present in the digital time-base counter will be read into the storage register. If the number held in the storage register is less than the number in the digital time-base counter, when measuring peak distortion, an enabling pulse is applied to the transition control gate through the comparison gate.

- (3) The inverting amplifier output now permits the number from the digital time-base counter to be read into the storage register. When DISTORTION SELECT switch 1A1S7 is set to AVERAGE, the comparison gate is inhibited and each new number in the digital time-base counter can be read into the storage register.

e. *Digital-to-Analog Converter Circuits.* The digital-to-analog converter circuits consist of read-in gates, a storage register, meter drive circuits, and the PERCENT DISTOR-TION meter. The number held in the storage register is in digital form. It is converted to analog form by the meter drive circuits and is displayed on the PERCENT DISTORTION meter. The storage register is reset to a new number by the read-in gates when it is enabled by the transition control gate (*d* above). The output of the storage register is applied to both the meter drive circuits and to the distortion comparator gates.

f. Transition-Sampler Circuits. The transition-sampler circuits include the space mark and mark-space gates, reset gate, synchronizing bistable, transition inhibit gate (trigger gate), and transition monitor monostable. The transition-sampler circuits determine the type of transition to be monitored.

- The output pulse from the transition monitor monostable is synchronized with the input signal transition by the synchronizing bistable. When a transition is received by the synchronizing bistable, an output is applied through the trigger gate to the transition monitor monostable. Another output of the synchronizing bistable, applied through a reset gate, immediately resets the synchronizing bistable to prepare it for the next transition.

- (2) When DISTORTION SELECT switch 1A1S7 is at TOTAL PEAK, both the space-mark and mark-space gates are enabled and all transitions are monitored. With DISTORTION SELECT switch 1A1S7 set at either EARLY PEAK or LATE PEAK, space-mark or mark-space transitions may be selected by the other DIS-TORTION SELECT switch, 1A1S6, and the corresponding early or late peak distortion will be monitored.

- (3) With DISTORTION SELECT switch 1A1S7 set at AVERAGE, space-mark or mark-space transitions

may again be selected by DISTOR-TION SELECT switch 1A1S6, and the corresponding average distortion of the selected transition will be monitored.

*g. Transition-Control Circuits.* The transition-control circuits include the transition-control gate, the early and late transition gates, the comparison gate, the inverting amplifier, and DISTORTION SELECT switches 1A1S6 and 1A1S7.

- (1) Six inputs are applied to the transition-control gate to determine exactly when a new number from the digital time-base counter should be read into the storage register.

- (a) The first input, applied through the comparison gate, is produced by the distortion comparator gates in the digital-to-analog converter circuits, which compare the six-digit binary number in the storage register to the reversible running output from the inverting OR gates and to the inverting amplifier of the digital time-base circuits.

- (b) Starting at each ideal transition time, the reversible running binary increases its count until the midpoint of a bit and then decreases its count until the next ideal transition time. The instantaneous value of the reversible running binary is always proportional to the displacement of a transition.

- (c) When the distortion analyzer is set to measure peak distortion and the reversible running binary count in the distortion comparator gates is less than the stored binary number in the storage register, the comparison gate will inhibit the transition control gate. In this way, it precludes the possibility of reading into the storage register any numbers that would indicate a level of distortion less than that already displayed on the PERCENT DIS-

TORTION meter. The transitioncontrol gate is not inhibited by the comparison gate during average distortion measurements.

- (d) The second and third inputs, early and late pulses from the early and late transition gates in the transition-control circuits, inhibit the transition-control gate during the 1/2-bit period after each ideal transition time. This will prevent measurements of early distortion during late peak distortion measurements, and before each ideal transition time to prevent measurements of late distortion during early peak distortion measurements.

- (e) The fourth input, from the transition gate of the baud distributor circuits (i below), enables the transition-control gate from a 1/2-bit period preceding to a 1/2-bit period following the ideal time of the transition as selected TRANSITION SELECT bv switch 1A1 S9. When TRANSI-TION SELECT switch 1A1S9 is set al ALL, the transition gate enables the tranistion-control gate for all transitions.

- (f) The fifth input, from the transition selection gating circuits (stop-mark/start-space transition inhibit gate), inhibits the transition-control gate during the first 1/2-bit period of each start-stop character, and thus establishes the stop-mark/start-space transition as the reference transition.

- (g) The sixth input, produced by the transition monitor monostable of the transition-sampler circuits, is a short enabling pulse produced at the time of each mark/space or space/mark transition (as determined by DISTORTION SELECT switches 1A1S6 and 1A1S7). During total peak distortion measurements, both monitored transitions

produce an enabling signal to the transition-control gate.

- (2) The output of the transition-control gate (a short pulse at the time of a selected transition) is inverted and applied to the read-in gates of the digital-to-analog converter circuits. During measurements of average distortion, the transition-control gate also enables the early and late selection gates through an inverting amplifier. To summarize, the function of the transition-control gate is to produce an enabling-pulse output for the read-in gates at the time of an input signal transition if the following is true:

- (a) The transition is of the polarity selected by DISTORTION SE-LECT switch 1A1S6 (both transitions during total peak distortion measurements).

- (b) The time is within the 1/2-bit period of the ideal time of the transition selected by TRANSI-TION SELECT switch 1A1S9.

- (c) The time is before the ideal transition time (early peak only).

- (d) The time is after the ideal transition time (late peak only).

- (e) The count in the digital time-base counter is greater than that stored in the storage register at the time of the transition (except during average distortion measurements).

*h. Early-Late Circuits.* The early-late circuits consist of the early and late selection gates, a holding bistable, early and late driver gates, and EARLY and LATE indicators.

- During measurements of average distortion, the digital time-base counter supplies a condition pulse of 1/2-bit duration to the early selection gate (63 to 0 count) and a condition pulse of 1/2-bit duration to the late selection gate (0 to 63 count).

- (2) The transition-control gate applies an enabling pulse, through an inverting amplifier, during an early

or late transition to control the EARLY and LATE indicators. The EARLY and LATE indicators are inhibited during peak distortion measurements by the application of -15 volts through DISTORTION SE-LECT switch 1A1S7 to the early and late driver gates.

*i. Baud Distributor Circuits.* The baud distributor circuits include the stop-mark/ start-space transition gate, the baud counter, transition selection gating circuits, inverting amplifiers, the transition gate, and the CHAR-ACTER SYNC jack.

- The digital time-base counter advances the baud counter one count for each ideal bit of any character (0 to 127 count) except the stopmark.

- (2) The baud counter, which is, in effect, a continuation of the digital timebase counter, produces a three-digit binary number proportional to the bit positions (start-space, first bit, second bit, third bit, fourth bit, fifth bit, stop-mark, and stop-mark/startspace transition). The first six digits are compared to the setting of TRANSITION SELECT switch 1A1S9, and cause the appropriate output to be selected from transition selection gating circuits.

- (3) One-half bit after the stop-mark transition, count-6 gate is enabled. The output of the count-6 gate is applied to the met monoatable of the timebase circuits (which resets the digital time-base counter to 127 or 1111111), and inhibits the timing input gate of the time-base circuits to insure that no timing pulses occur between characters.

- (4) The output of count-6 gate is also applied to the stop-mark/start-space transition gate through an inverting amplifier. It conditions the gate so that the stop-mark/start-space transition advances the baud counter one full count and enables the count-7 gate as described in (6) below.

- (5) The inverting amplifier output is also applied to the CHARACTER SYNC jack through a second inverting amplifier to provide a negative-going transition that coincides with the end of each character. A positive-going transition is also available to coincide with the start of each character. The output of the inverting amplifier also inhibits the transition inhibit (trigger) gate in the transition sampler circuits.

- (6) TRANSITION SELECT switch 1A1S9 conditions the selected transition gating circuits. The selected gates (count 0 through count 7) are enabled by an output from the baud counter. When a selected gate is enabled, its output triggers the transition gate. The transition gate conditions the transition-control gate of the transition-control gate of the transition-control circuits during the time of the transition to be monitored.

- (7) The output of the transition gate is a 1-bit pulse, centered about the ideal time of the selected transition. This is accomplished by comparing the output of the baud counter with the setting of TRANSITION SE-LECT switch 1A1S9. At the start of each character, the stop-mark/startspace transition of the baud counter enables the count-7 gate and inhibits the count-6 gate in the transition selection gating circuit.

- (8) The output of the count-7 gate inhibits the transition-control gate for 1/2 bit, and the stop-mark/start-space transition is not monitored. The number stored in the storage register of the digital-to-analog converter circuits does not change. The output of the inhibited count-6 gate enables the timing input gate in the time-base circuit, and the digital time-base counter is activated. The output of the count-6 gate also inhibits the stop-mark/start-space transition gate. At the count of 63, the

baud counter is advanced 1/2-bit after the stop-mark/start-space transition, and the count-0 gate is enabled.

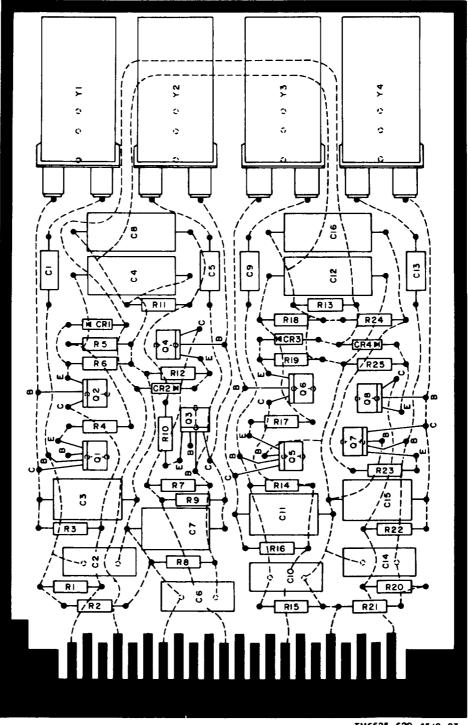

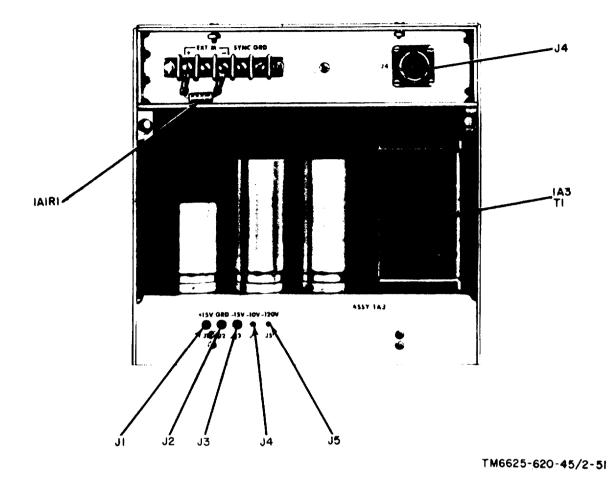

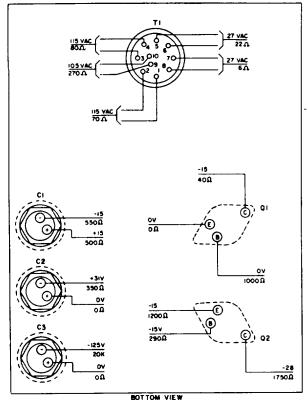

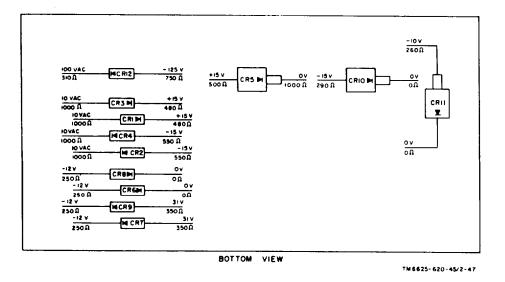

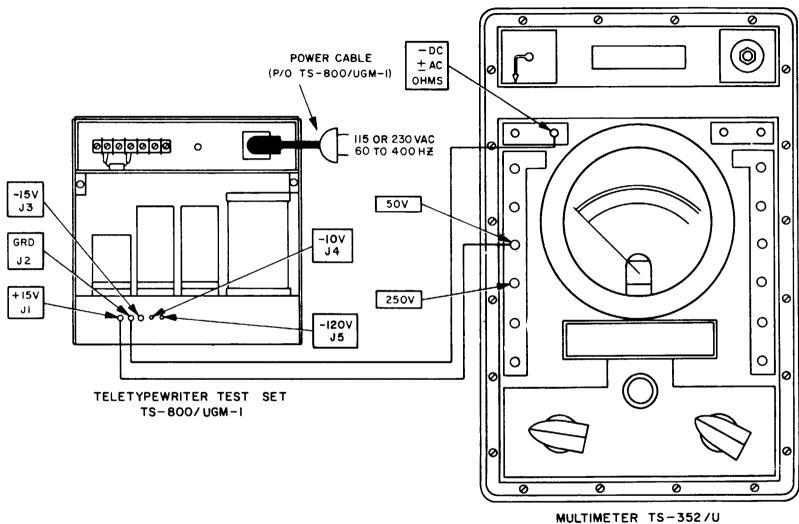

*j. Power Supply Block Diagram* (fig. 6-2). Output voltages are + 15, -15, -120 volts direct current (dc). These voltages are developed from a 115- or 230-volt alternating current (ac) power source. The input is applied through line filter 1A1FL1 and switch 1A1S1. The ac power is applied to the primary of transformer T1 from switch 1A1S1.

- Reguluted + 15-volt dc circuit. The ac voltage from transformer T1 is converted to dc by bridge rectifier diodes CR1 through CR4, and regulated by 15-volt regulator transistor Q1 and Zener diode CR5.

- (2) Regulated -15-volt dc circuits. Bridge rectifier diodes CR6 and CR7 convert the ac to a -15-volt dc voltage that is regulated by transistor Q2 and Zener diode CR10.

- (3) Regulated. -10-volt dc circuit. Zener diode CR11 regulates the -10 volts dc.

- (4) Unregulated -120-volt dc circuits. The ac voltage from transformer T1 is converted to dc by half-wave rectifier CR12.

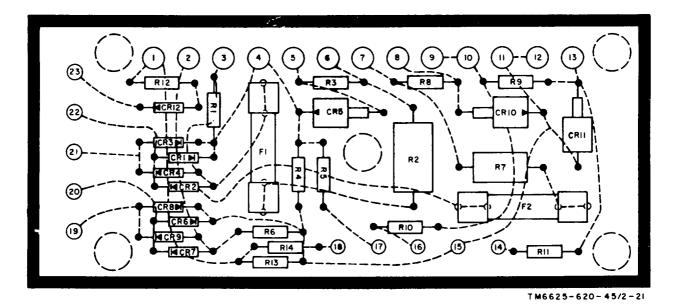

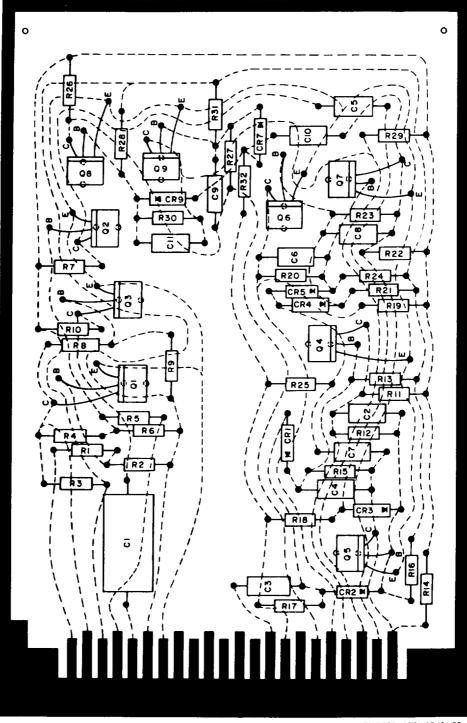

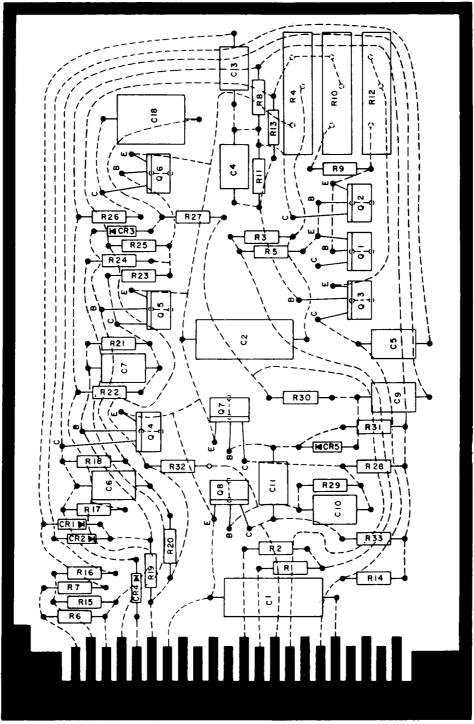

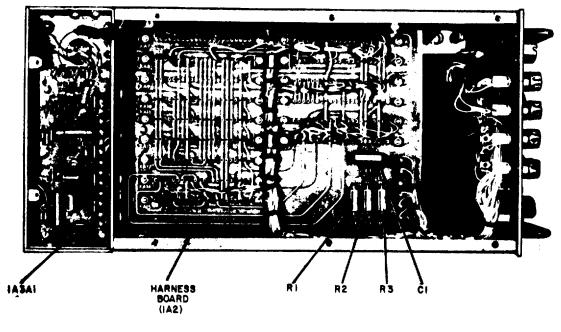

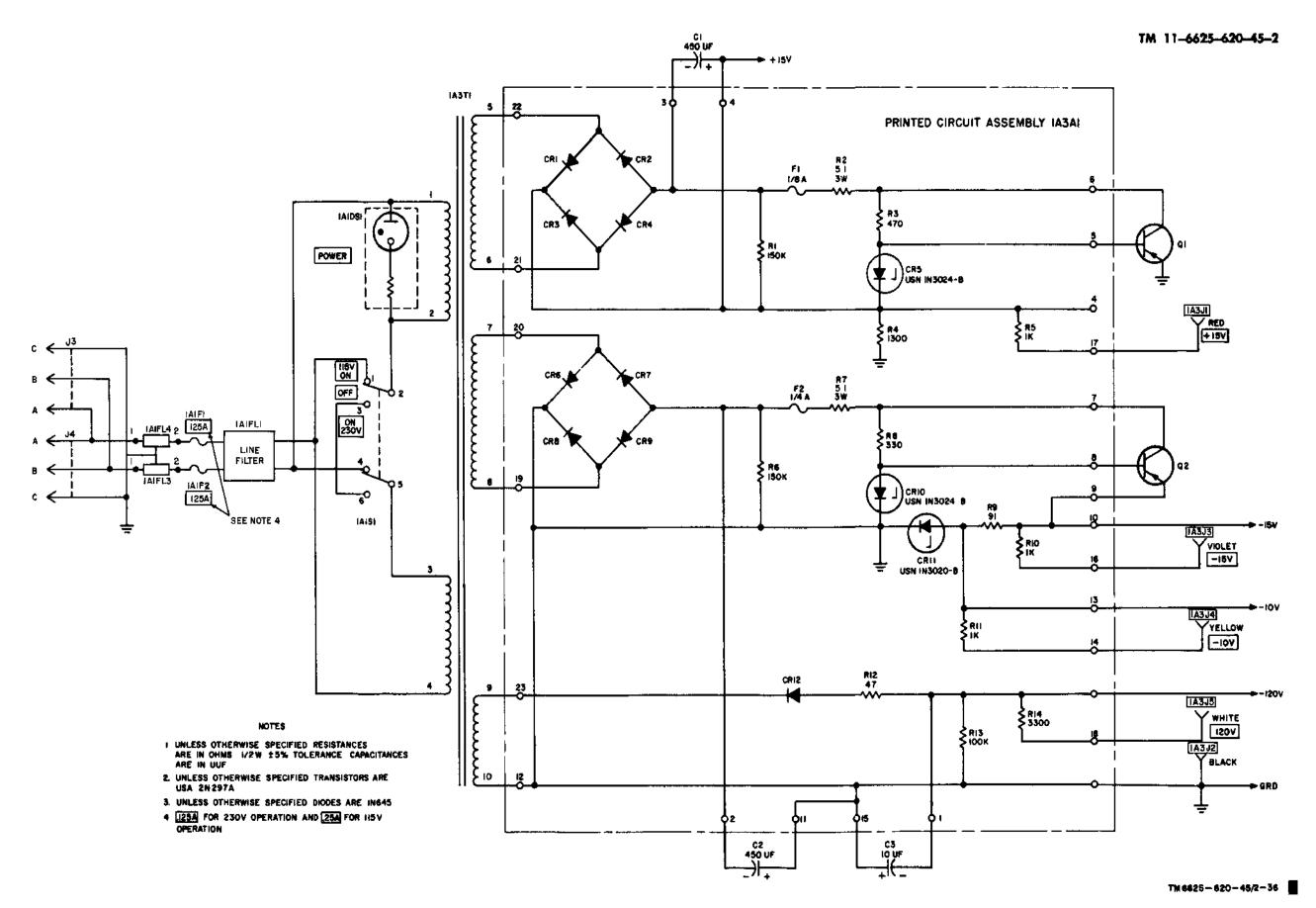

## *k. Power Supply Circuit Analysis* (fig. 6-10).

- (1) *Line voltage.* The line voltage (115 or 230 volts ac 50–60 Hertz (Hz)) is applied through line fuses 1A1F1 and 1A1F2 to line filter 1A1FL1 and to power switch 1A1S1, and then to the primary of transformer 1A3T1 and POWER lamp 1A1DS1. Transformer 1A3T1 has three stepdown secondary windings.

- (2) Regulated + 15-volt dc circuit. Bridge rectifier diodes CR1 through CR4 convert the ac from transformer 1A3T1 secondary (terminals 5 and 6) to dc and is filtered by capacitor C1. Resistor R1 provides a discharge path for capacitor C1. Fuse F1 protects the + 15-volt dc circuit from

overload. Resistor R2 provides current limiting. When the output voltage developed across resistor R4 drops, Zener diode CR5 forwardbiases transistor Q1, and allows more current to flow through transistor Q1 to provide the regulated +15 volts to associated assemblies. Resistor R3 provides current limiting for CR5 and the base of transistor Q1. If the output voltage developed across resistor R4 increases, CR5 reverse-biases the emitter-base junction of transistor Q1 and reduces the current through it. This reduces the voltage developed across resistor R4 to the regulated +15 volts. Resistor R5 provides isolation for test equipment connected to jack J1.

(3) Regulated -15-volt dc circuit. Bridge rectifier diodes CR6 through CR9 convert the ac from transformer 1A3T1 secondary (terminals 7 and 8) to dc, and is filtered by capacitor C2. Resistor R6 provides a discharge path for capacitor C2. Fuse F2 protects the -15-volt dc circuit from overload. Resistor R7 provides current limiting. When the output voltage developed across resistor R9 and Zener diode CR11 drops, CR10, forwarded-biases transistor Q2 and allows more current to be drawn through Q2 to provide a regulated -15 volts to associated assemblies. Resistor R8 provides current limiting for CR10 and the base of Q2. If the output voltage developed across CR11 and R9 increases, CR10 reverse-biases the emitterbase junction of Q2. This reduces the voltage developed across R9 and CR11 to the regulated -15 volts. Resistor R10 provides isolation for test equipment connected to jack J3.

- (4) Regulated -10 volts dc. Zener diode CR11 provides -10 volts regulation with voltage-dropping resistor R9. Resistor R11 provides isolation for test equipment connected to jack J4.

- (5) Unregulated -120-volt dc circuit. The output of transformer 1A3T1 (secondary terminals 9 and 10) is half-wave rectified by CR12 and filtered by R12 and capacitor C3. Resistor R14 provides isolation for test equipment connected to jack J5. Resistor R13 is the bleeder resistor that provides a discharge path for capacitor C3.

#### Section III. CIRCUIT ANALYSIS AND LOGIC SYMBOLS

#### 1-5. General

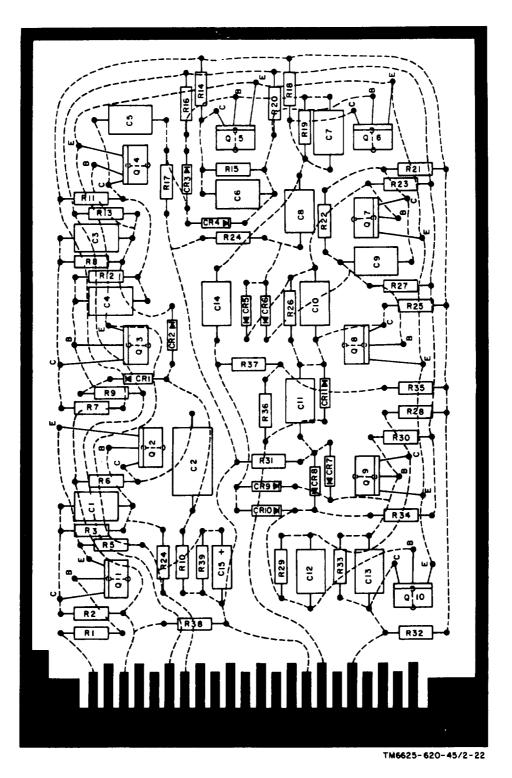

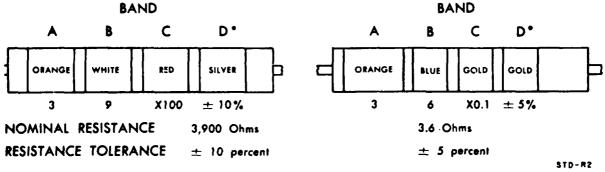

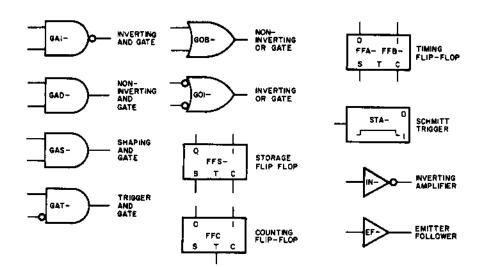

a. Many of the stages in the distortion analyzer are identical except for the parts values and the reference designations used. *For example*, the seven bistable multivibrator stages (FFC-8 through FFC-14) which make up the digital time-base counter contain identical circuits. Therefore, the circuit analysis of the distortion analyzer provided in this manual is of each type, rather than of each individual stage. The circuit analyses of the different types of stages are contained in paragraphs 1–6 through 1–14. All referenced symbols are shown on the logic diagram (fig. 6-3). b. References designations, such as Ca, Rc, and Qa (figs. 1-1 through 1-10) are arbitrarily assigned to assist in making the circuit analyses (paras 1-6 through 1-14). To determine the correct reference designation for a specific part within a particular stage, refer to the applicable schematic diagram.

c. Designations such as 0 and 1 are the logic symbols used to define voltage levels. A 0 represents a high-level potential very near ground (0 volt), and a 1 represents 2 low-level potential (approximately -15 volts). Because of the potential differences between 0 and *1*, a transition from 0 to *1* produces a negative pulse, and a transition from

*1 to 0* produces a positive pulse. The more negative of two given logic levels (*1*) is represented by the presence of a small circle at the input or output points of the logic sym bol; conversely, the more positive level (0) is represented by the absence of the circle. The logic levels shown at the inputs and outputs of gate and amplifier logic symbols are those present when the logic element is active (i.e., when it is performing its principal function). *For example*, if the symbol is that of an AND function, the logic levels shown include the required inputs and resultant output level developed when the AND stage is operating.

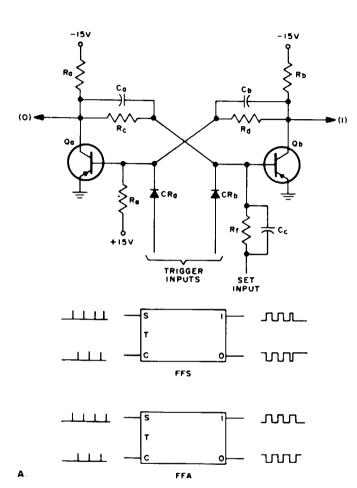

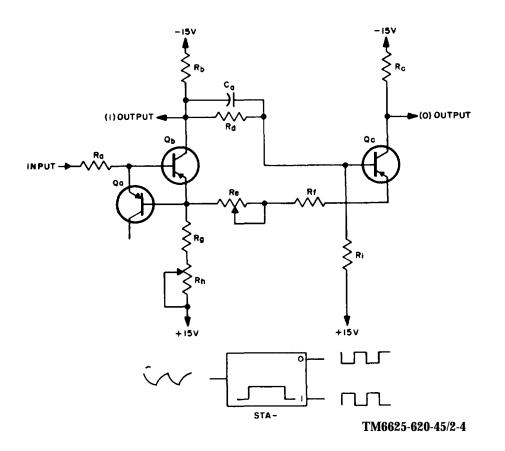

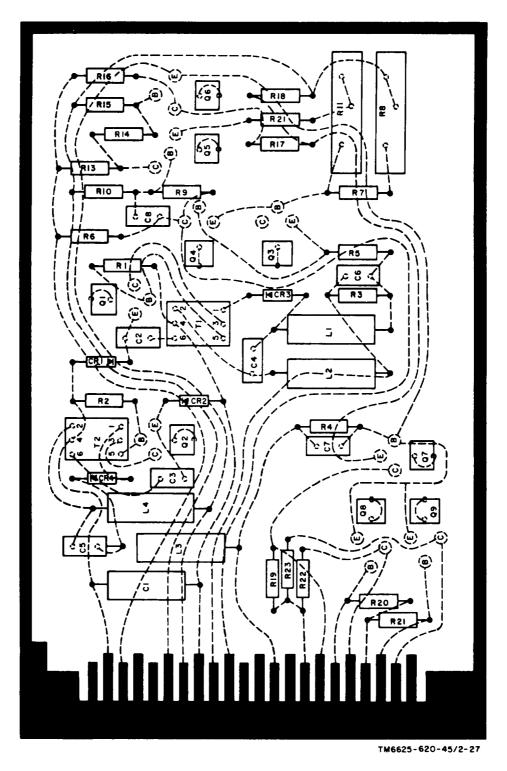

### **1-6. Bistable Multivibrator Stages** (fig. 1-1)

a. *General.* Three variations of a bistable multivibrator stage are used in the distortion analyzer, two of which are illustrated in figure 1-1. The logic symbol, used with the logic diagram (fig. 8-3) and shown directly below each bistable multivibrator stage, is the same for each bistable multivibrator, because their functions are the same.

- (1) The reference designations for the logic symbols of the bistable multivibrator stages differ, and indicate the manner in which they are triggered. The lines on the left side of the logic symbols represent inputs (including the reset provisions). The lines on the right side of the logic symbols represent outputs. The upper lines (left and right) of the logic symbol are associated with one of the transistors in the stage, and the lower lines (left and right) are associated with the other transistor.

- (2) Bistable multivibrators are set by applying a positive-going transition (logical-1 to logical-0) to the set (S) input, thereby producing a logical-1 at the 1 output and a logical-0 at the 0 output. An identical input transition applied to the clear (C) input resets the flip-flop, pro-

ducing a logical-0 at the 1 output and a logical-1 at the 0 output. When a logical-1 is present at the 1 output, the flip-flop is defined as being in its 1-state; a logical-0 at the 1 output defines the 0-state.

b. Circuit Analysis. Resistors Re and Rf establish the initial bias for transistors Qa and Qb, respectively. Resistors Ra and Rb are the collector load resistors. Resistors Rc and Rd and capacitors Ca and Cb determine the switching time required for the stage to change state. The outputs, which are 180° out of phase with each other, are developed across the collector and emitter of transistors Qa and Qb.

*c. Triggering.* The stages shown in figure 1-1 require positive pulses at the inputs If the transistor associated with a given input is conducting when the positive pulse is applied through steering diode CRa or CRb (B, fig. 1-1), the transistor will cut off. A second positive input pulse through the opposite steering diode will return the stage to its original state. The state shown in B, figure 1–1 will change each time a positive pulse is applied through differentiating network Cd and R3 and steering diodes CRa and CRb.

*d. Set.* The set input triggers (A and B, fig. 1–1) are employed to place the bistable multivibrators FFS stages into predetermined states. Bistable multivibrator FFA is the same as the FFS type (B, fig. 1-1), except that it does not have a set trigger.

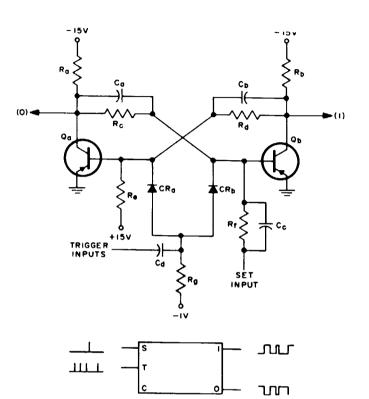

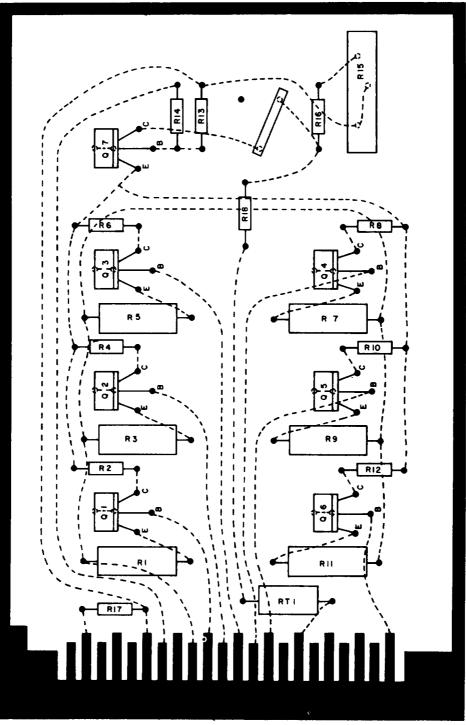

#### 1-7. Monostable Multivibrator Stages (fig. 1-2)

a. General. Three variations of a monostable multivibrator stage are used in the distortion analyzer, two of which are shown in figure 1-2. The logic symbol, used with the logic diagram (fig. 6-3) and shown directly below each monostable multivibrator stage, is the same for each monostable multivibrator, because their functions are the same. The reference designations for the logic symbols of the monostable multivibrator stages differ, and indicate the manner in which they are triggered. The lines on the left side of the logic symbols represent the inputs, and the lines on the right side represent the outputs.

FFC

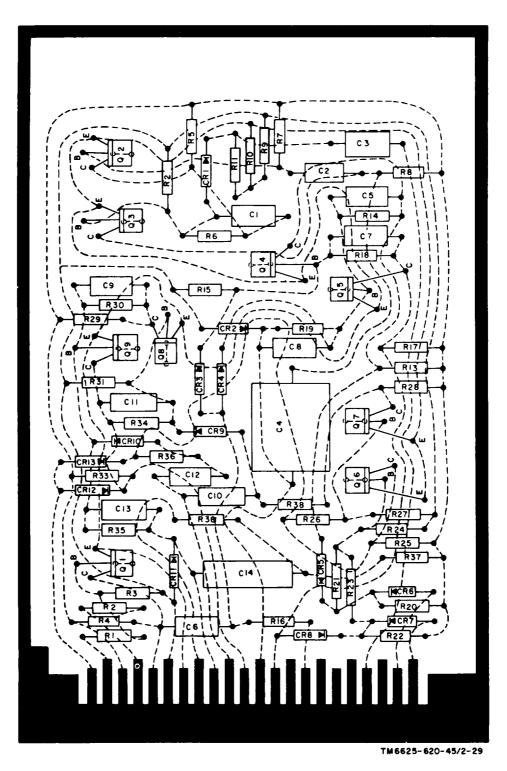

TM6625-620-45/2-2

Figure 1–1. Bistable multivibrator stage.

В.

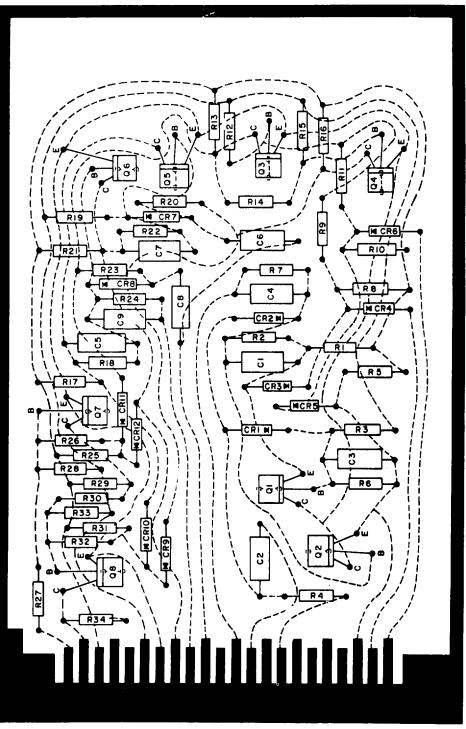

Figure 1-2. Monostable multivibrator stage.

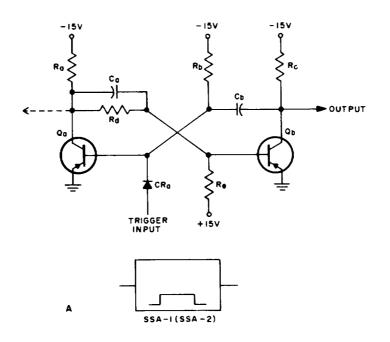

- b. Circuit Analysis.

- (1) The set-input trigger is applied through steering diode CRa to transistor Qa. which is normally conducting. A positive input pulse is then required to trigger the stage (A, fig. 1-2) (SSA-1). For SSA-2, the steering diode is reversed and the set-input trigger is applied to transistor Qb, which is normally cut off. In this case, a negative pulse is required to trigger the stage. Resistors Ra and Rc, (A, fig. 1-2) are collector load resistors; resistors Rb and Re establish the initial bias; and resistor Rd, with capacitors Ca and Cb, determines the switching time required to return the stage to its original state.

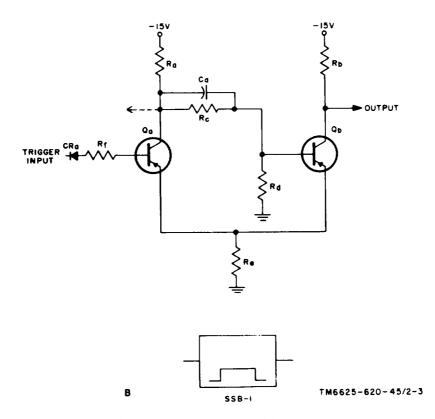

- (2) In B, figure 1-2 the set-input trigger is applied through steering diode CRa and limiting resistor Rf to the base of transistor Qa, which is normally cut off, A negative input pulse is then required to trigger the stage. Resistors Ra and Rb are collector load resistors; resistors Rd and Rc establish the initial bias; and resistor Rc, with capacitor Ca, determines the switching time required to return the stage to its original state.

#### **1-8. Schmitt Trigger Stages**

(fig. 1-3)

a. General. The two Schmitt Trigger Stages are of the same type. The logic symbol shown directly below each stage is used with the logic diagram (fig. 6-3). The line on the left side of the logic symbol represents the input, and the lines on the right side represent the output, The 0 output is in phase with the input, and the 1 output is  $18^{\circ}$  out of phase with the input.

*b. Circuit Analysis.* Transistor Qa and resistor Ra provide the stage with a relatively constant input resistance. Resistors Rb and Rc are collector load resistors, resistors, Rg and Rh are common emitter resistors, and Re and Rf compensate for hysteresis loss in the circuit. Voltage-dividing network resistors Rb, Rd, and Ri provide bias for transistor Qc; and capacitor Ca, with resistor Rd, provides coupling from the collector of transistor Qb to the base of transistor Qc.

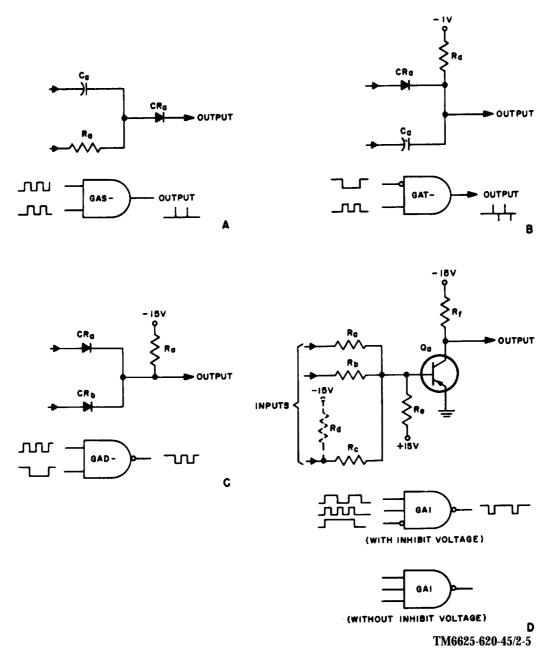

#### **1-9. AND Gate Stages** (fig. 1-4)

a. General. Four types of AND gate stages are used. The function of each AND gate is the same; therefore, the logic symbol shown directly below each stage and used with the logic diagram (fig. 6-3) is the same for each stage, except for the number of inputs available. The lines on the left side of the logic symbols represent inputs. A circle on an input line indicates that the signal is applied through a switch, and whenever the switch is in the open position, an inhibit voltage is applied to the gate. Typical input and output waveforms are shown for normal operation.

*b. Circuit Analysis.* An AND gate stage will develop an output when coincident input pulses are present on the input lines.

- (1) The AND gate stage shown in A, figure 1-4, uses capacitor Ca and resistor Ra in the inputs, and diode CRa in the output. The waveforms shown with the logic symbol indicate that the leading pulse of two positive coincident pulses is required to provide a positive output spike.

- (2) The AND gate shown in B, figure 1-4, uses diode CRa with forwardbiasing resistor Ra, and capacitor Ca for the inputs. The waveforms shown with the logic symbol indicate that, with a negative level applied to CRa, the leveling edge of a positive pulse will provide a positive output spike and the trailing edge of a positive pulse will provide a negative output spike.

- (3) The AND logic function shown in C, figure 1-4, is performed with input diodes CRa and CRb and load resistor Ra. The waveforms shown indicate that two negative coincident

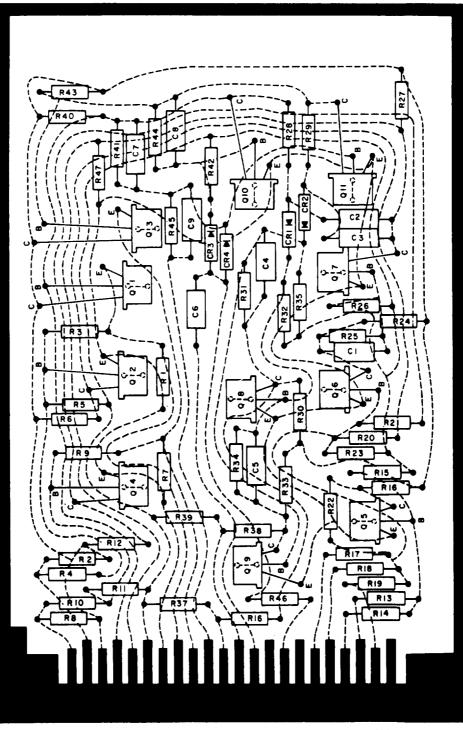

Figure 1-3. Schmitt trigger stage.

pulses are required to provide a negative output pulse.

(4) Resistors Ra, Rb, and Rc are input coupling resistors for the AND gate stage shown in D, figure 1-4. Resistor Rf is the collector load resistor and resistor Re establishes reverse bias for transistor Qa. Resistor Rd is the inhibit load resistor when the input is open. The waveforms shown with the logic symbol indicate that three positive coincident pulses are required to provide a negative output pulse.

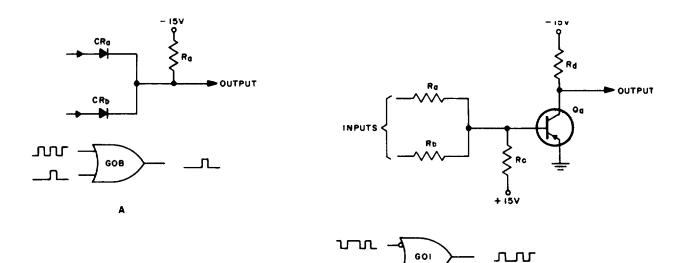

#### 1-10. OR Gate Stages

(fig. 1-5)

Two variations of OR gate stages are used. The function of each OR gate stage is the same; therefore, the logic symbol shown directly below each stage and used with the logic diagram (fig. 6-3) is the same for each stage. Typical input and output waveforms are shown for normal operation.

*a.* Input diodes CRa and CRb and load resistor Ra make up the OR gate stage shown in A, figure 1-5. The waveforms shown with the logic symbol indicate that a positive output pulse occurs when a positive input pulse is present on either input line.

b. Resistors Ra and Rb are input coupling resistors for the OR gate stage shown in B, figure 1-5. Resistor Rc establishes reverse bias, and resistor Rd is the collector load resistor for transistor Qa. The waveforms shown with the logic symbol indicate that negative pulses on any one of the input lines provide a positive output pulse.

#### Figure 1-4. AND gate stage.

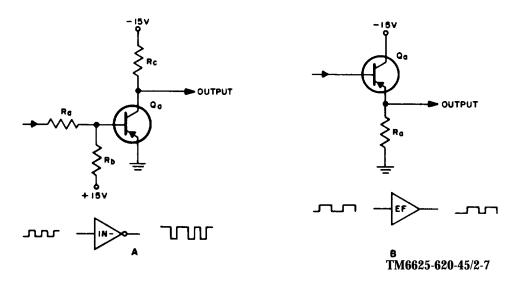

### **1-11. Amplifier Stages** (fig.1-6)

a. General. The inverting amplifier stage shown in A, figure 1-6 and the emitter follower shown in B, figure 1-6 are used. The lines on the left side of the logic symbol are input lines, and the lines shown on the right side are output lines. Typical input and output waveforms representing normal operation are shown with the logic symbols (A and B, fig. 1-0).

- b. Ciruit Analysis.

- (1) Resistor Ra is the input coupling resistor for the inverter stage shown

TM6625-620-45/2-6

Figure 1-5. OR gate stage.

ாா

in A, figure 1-6. Resistor Rb eatablishes reverse bias and resistor Rc is the collector load resistor for transistor Qa. The waveforms shown with the logic symbol indicate that the input waveform is amplified and inverted by the stage.

(2) Resistor Ra is the emitter load resis. tor for the emitter follower stage shown in B, figure 1-6. The waveforms shown with the logic symbol indicate that no amplification takes place because the emitter follower stage is primarily used for impedance matching.

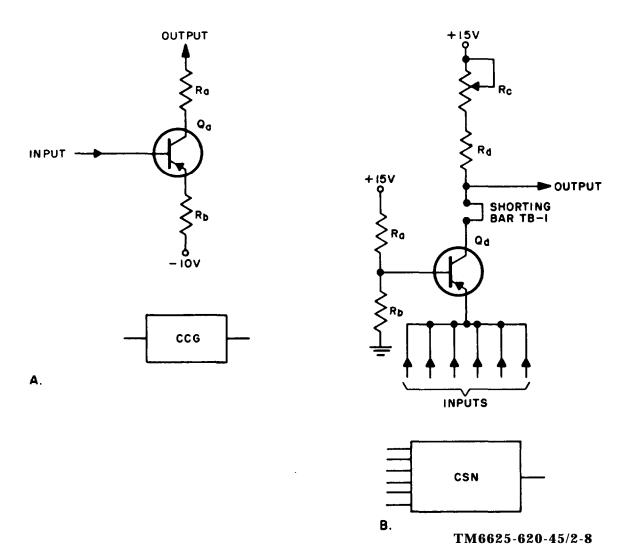

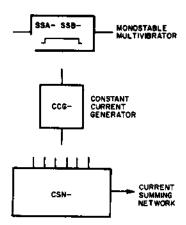

#### 1-12. Constant-Current Generator and Current Summary Circuits

#### (fig. 1-7).

a. General. The constant-current generator stage used with its logic symbol is shown in A, figure 1–7. The type of summing stage used with its logic symbol is shown in B, figure 1-7. The lines on the left side of the logic symbols represent input lines, and the lines on the right side represent output lines. The logic symbols are used with the logic diagram (fig. 6-3). No input or output waveforms are shown with these logic symbols (fig. 1–7) because both stages produce a current level in the output.

- b. Circuit Analysis

- The constant-current generator stage shown in A, figure 1-7 is a digitalto-analog converter. Resistor Rb establishes the direct current (dc) voltage level applied to the emitter of transistor Qa. Resistor Ra is the collector load. With the input voltage, either 0 or -15 volts dc, transistor Qa is reverse-biased, and no current is produced in the output.

- (2) Voltage-dividing resistors Ra and Rb shown in B, figure 1-7, bias transistor Qa in the active region.

Figure 1-7. Constant-current genarator and summing stages.

Variable resistor rc and resistor Rd make up the collector load. Shorting bar SB-1 is removable to permit measurement of the collector current. The input current to the summing stage is supplied by the constant-current generator stage ((1) above). The sum of the currents applied to the inputs of the summing stage provides the necessary current to operate the PERCENT **DISTORTION** meter (not shown), which is paralle-connected with variable resistor Rc and resistor Rd.

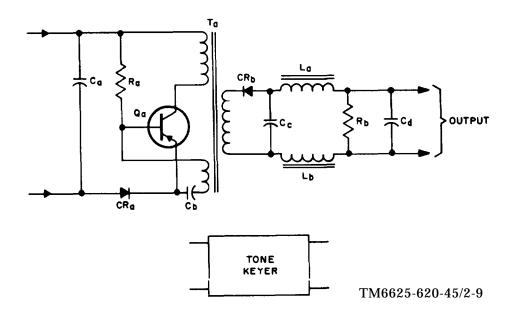

#### 1-13. Tone-Keyer Stages (fig. 1-8)

a. General. Two tone-keyer stages are used in the signal input circuit, and the type used is shown in the figure. The logic symbol shown directly below the stage is used with the logic diagram (fig. 6-3). The lines on the left side of the logic symbol represent inputs, and the lines on the right side represent the output. The waveforms shown with the logic symbol indicate that the tone-keyer stage will produce an output for a neutral signal and for positive or negative polar signals.

b. Circuit Analysis. Transistor Qa, resistor Ra, the primary of transformer Ta and the inherent capacitance of the circuit make up an oscillator circuit which is triggered by the input signal, Capacitor Ca isolates the oscillator from the signal input. Diode CRa isolates tone kever No. 1 from tone kever No. 2. Capacitor Cb prevents the base-emitter circuit of transistor Qa from shorting through the primary winding of transformer Ta. The output signal is applied through half-wave rectifier CRb, filter capacitors Cc and Cd, filter chokes La and Lb, and is developed across load resistor Rb.

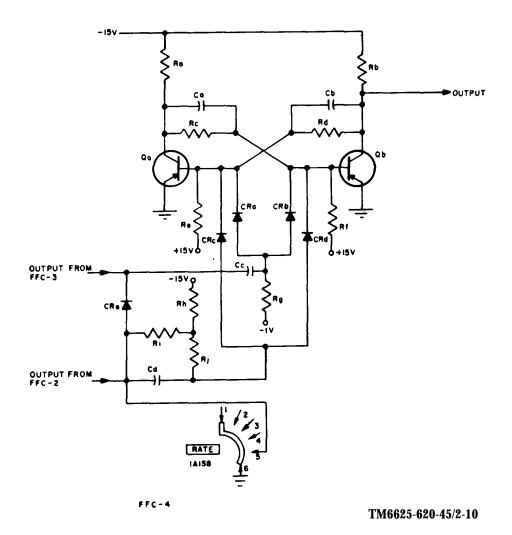

#### 1-14. Time Base Frequency-Divider Network

#### (fig. 1-9)

a. General. Four bistable multivibrator stages are used in the time-base circuits in a frequency-divider network, which divides the oscillator circuit output to a frequency which is equal to 128 times the baud rate. Stages FFC-1, FFC-2, and FFC-3 are the same as that shown in A, figure 1-1, except that the latter has no set input and the 0 output line is not used. Fourth bistable multivibrator

Figure 1-8. Tone-keyer stage.

FFC-4, of the time-base frequency-divider network, is shown in figure 1–9.

b. Circuit Analysis. Resistors Re and Rf establish the initial bias for transistors Qa and Qb, respectively; resistors Ra and Rb are the collector load resistors; and resistors Rc and Rd, with capacitors Ca and Cb, determine the switching time required for the stage to change state. Resistors Rh and Rj reverse-bias diodes CRC and CRd in all RATE switch 1A1S8 positions except for 150 BAUDS (position 5). When the RATE switch is set to position 5, resistors Rh and Ri are used to forward-bias diodes CRC and CRd. Diode CRe clamps FFC-3 at ground when the RATE switch is set to position 5.

c. Triggering. Bistable multivibrator stage FFC-4 requires a positive pulse at the inputs.. Because there are two sets of steering diodes (CRa and CRb, and CRC and CRd), this stage may be controlled by two separate inputs. When RATE switch 1A1S8 is set to 150 BAUDS (position 5), steering diodes CRC and CRd are forwarded-biased. Because a ground is also applied through diode CRe to the 1 output of FFC-3, the output from bistable multivibrator stage FFC-2 controls the stage. When RATE switch 1A1S8 is set to any other position, steering diodes CRC and CRd, as well as as diode CRe, are reverse-biased and cause the output from FFC-3 to control the stage.

Figure 1-9. Time-base frequency-divider network

#### 1-15. Signal Input Circuit

#### (fig. 6-3)

a. Neutral or polar telegraph signals are applied through SIGNAL INPUT jack 1A1J1, and then to POLARITY switch 1A1S2. The telegraph signal is converted from a current level signal to a voltage level signal by the converter to provide for operation of the tone keyers. Tone keyers No. 1 and No. 2 isolate all received telegraph signals from ground, thus providing an. output equivalent to a polartype telegraph signal. When POLARITY switch 1A1S2 is in the appropriate position for a particular type of input signal, tone keyer No. 1 is activated by either neutral or polar marking signals, and tone keyer No. 2 is activated by only polar spacing signals.

b. The output from the tone keyers is selected by CURRENT SELECT switch 1A1S3 and is applied to Schmitt trigger STA-1. Schmitt trigger STA-1 shapes the signal and drives Schmitt trigger STA-2. The output of STA-2 is applied through inverting amplifiers IN-1 and IN-2 to SIGNAL indicator lamp 1A1DS1, which lights when the input signal is in a marking condition. Spikes or holes in the signal, which could cause erroneous indications on PERCENT DISTORTION meter 1A1M1, are eliminated when FILTER switch 1A1S4 is set to IN.

c. Schmitt trigger STA-2 provides additional shaping of the signal, which is applied to inverting AND gate GAI-1. AND gate GAI-1 provides an output which is used to reset bistable FFC\5 (para 1-24) during the stopmark/start-space transitions only, to initiate each character cycle. The output of STA-2 is also applied to GAS-1 in the transition-sampler circuits (para 1-21).

#### 1-16. Time-Base Circuits

(fig. 6-3)

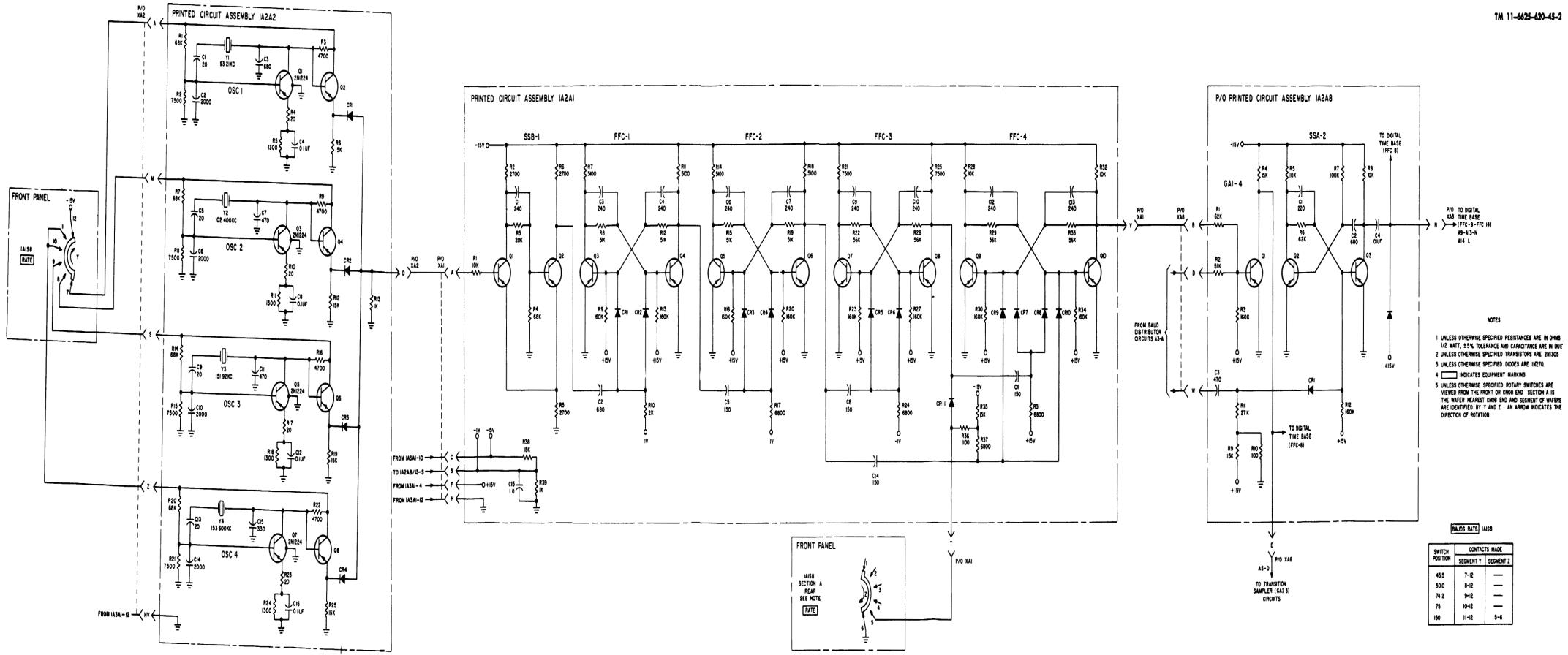

a. The timing signal to be used for the distortion measurements is generated by one of four crystal oscillators. The oscillator circuit to be used is selected by RATE switch 1A1S8. The output of the selected oscillator is a sine wave and is shaped into a square wave by monostable SSB-1. It is then applied to fourstage frequency divider FFC-1 through FFC-4. The oscillator frequency is such that, after division by the four-stage divider, a timing signal of 128 times the baud frequency of the input signal is obtained.

b. The output of the four-stage divider is applied to inverting AND gate GAI-4 together with an input from the inverting AND gate GAI-2 in the baud distributor circuits. AND gate GAI-2 supplies a high-level signal to GAI-4 from the start of a character through 1/2-bit of the stop-mark bit, This high-level signal from GAI-2 enables GAI-4 so that a timing signal from the frequency divider may be applied to the digital time-base circuits (para 1-17). The low-level signal from GAI-2 (from l/2-bit into the stop-mark bit until the stop-mark/start-space transition of the next character) inhibits GAI-4, and the timing signal is not applied to the digital time-base circuits.

c. When a low-level signal from GAI-2 is applied to monostable SSA-2, the negative low-level output of SSA-2 is applied to the digital time-base circuit as a set pulse for the digital time-base counter.

d. The output of GAI-4 is also applied to inverting AND gate GAI-3 in the transition-sampler circuits (para 1-21).

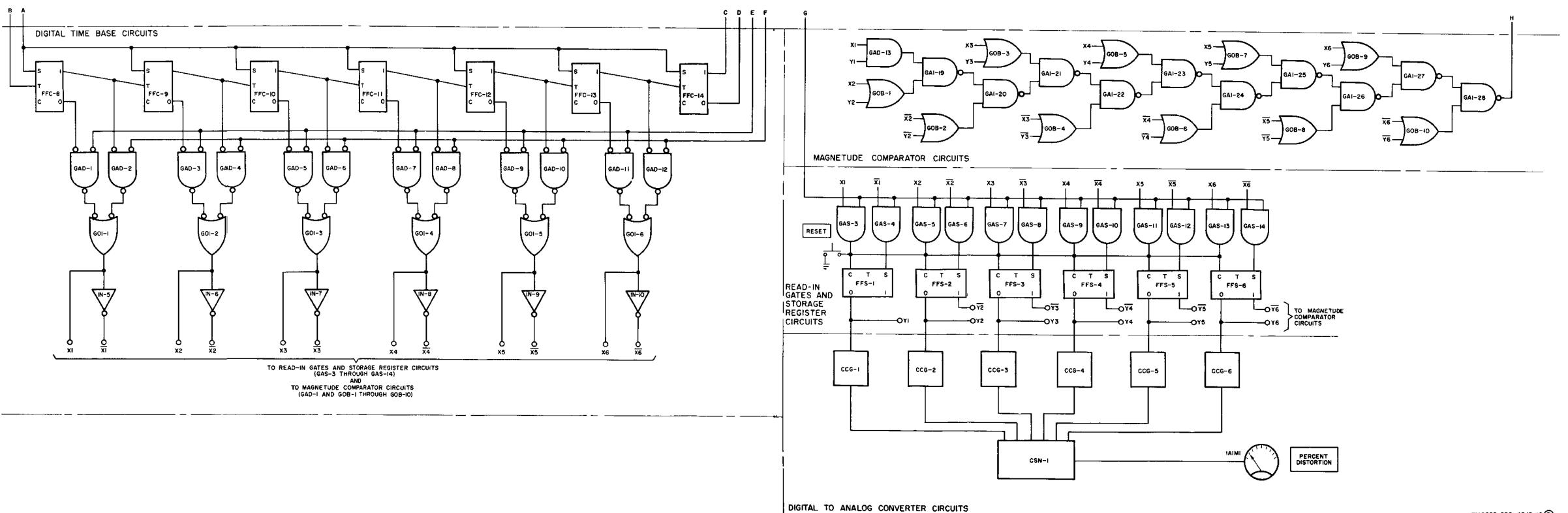

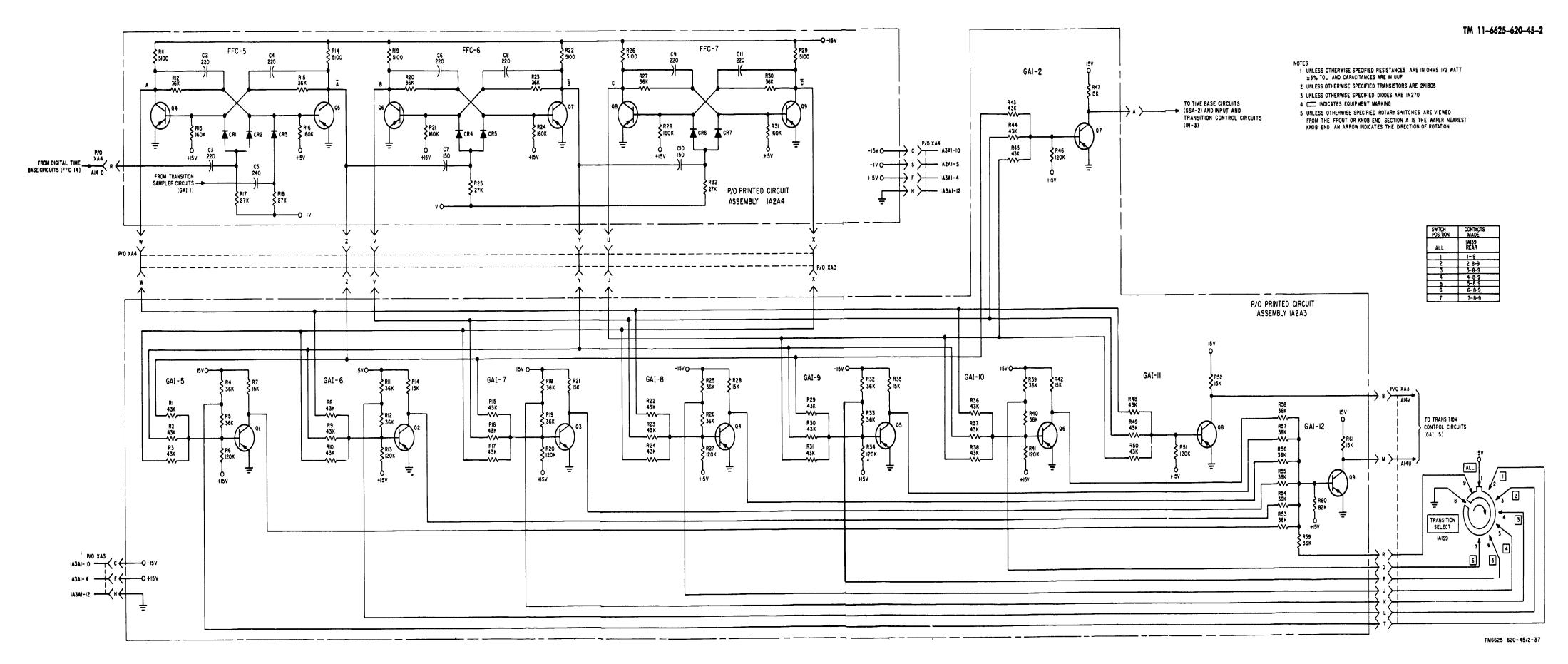

#### **1-17. Digital Time-Base Circuits** (fig. 6-3)

a. General. The digital time-base counter (FFC-8 through FFC-14) is controlled by AND gate GAI-4 in the time-base circuits. Because the signal from the time-base circuits is 128 times the baud frequency of the input signal, it enables the digital time-base counter to count from zero to 127 during each bit of the input signal, except during the stop mark (para 1–16b). The count from the digital time-base counter is taken from bistables FFC-8 through FFC-13, and only the zero to 63 count. is used. The outputs from the 0 output lines of bistables FFC-8 through FFC-13 (complementary count) are applied to oddnumbered AND gates GAD-1 through GAD- 11, and the outputs from the 1 output lines of bistables FFC-8 through FFC-13 (true count) are applied to even-numbered AND gate GAD-2 through GAD-12.

- (1) The output from the 0 output line of bistable FFC-14 is applied to the remaining input line of odd-numbered AND gates GAD-1 through GAD-11 through emitter follower EF-1, and the output from the 1 output line of bistable FFC-14 is applied to the remaining input line of evennumbered AND gates GAD-2 through GAD-2 through emitter follower EF-2. AND gates GAD-1 through GAD-12 are therefore controlled by bistable FFC-14, which can change its state only once during the entire zero to 127 count (the 0 output line of FFC-14 is at 1 from the 64 to 127 count). A true count (zero to 63 from the 1 output lines of bistable FFC-8 through FFC-13) is obtained at the output of the even-numbered AND gates (GAD-2 through GAD-12) as the digital time-base counter counts from zero to 63.

- (2) A complimentary count (63 to zero, from the 0 output lines of bistables FFC-8 through FFC-13) is obtained at the output of odd-numbered AND gates GAD-1 through GAD-11 as the digital time-base counter counts from 64 to 127. The outputs of AND gates GAD-1 through GAD-12 are applied, through inverting OR gates GOI-1 through GOI-6, to the X1 through X6 lines, respectively. The outputs on the X1 through X6 lines therefore provide a zero to 63 and 63 to zero count. The outputs from gates GOI-1 through GOI-6 are also applied, through inverters IN-5 through IN-10, to the  $\overline{X1}$  through  $\overline{\mathbf{X6}}$  lines, respectively. The outputs on the X through  $\overline{X6}$  lines therefore provide a 63 to zero and zero to 63 count.

*b. Operating Sequence.* The digital timebase counter counts from zero to 127 for each bit of a character except the stop mark. For the stop mark, the digital time-base counter counts from zero to 63 and stops until the stop-mark/start-space transition of the next character. The digital time-base counter is initially set to 127 (a 1 on each 1 output line of bistables FFC-8 through FFC-14 or 64 counts into the stop-mark bit) by monostable SSA-2. Monostable SSA-2 is triggered by count six AND gate GAI-2 in the baud distributor circuits, and monostable SSA-2, in turn, applies a set pulse to bistables FFC-8 through FFG 14.

- (1) The first pulse received from AND gate GAI-4 thus causes each bistable (FFC-8 through FFC-14) to change state. That is, the digital time-base counter advances one count from 127 (1111111) to zero (000000). The resulting transition from 1 to 0 on the 1 output line of bistable FFG 8 triggers each succeeding bistable. The 1 output on the 0 output line of bistable FFC-14 is applied to one input of odd-numbered AND gates GAD-1 through GAD-11. The other input to each of these gates is a 1 from the 0 output line of bistables FFC-8 through FFC-13. When two low-level inputs are applied to each odd-numbered AND gate GAD-1 through GAD-11, the output of these gates will be a 1.

- (2) The 1 output is then inverted by OR gates GOI-1 through GOI-6 and appears on each X1 through X6 line as a 0 (000000). Another output from OR gates GOI-1 through GOI-6 is inverted by inverters IN-5 also through IN-10 and appears on each  $\overline{\mathbf{X1}}$  through  $\overline{\mathbf{X6}}$  line as a 1 (111111), The second pulse received from GAI-4 changes the state of bistable FFC-8, but has no effect on bistable FFC-9. When this occurs, the count is changed to 100000 on the X lines and to 011111 on the  $\overline{\mathbf{X}}$  lines. The third input pulse changes the state of FFC-8 again, and it, in turn, changes the state of bistable FFC-9.

- (3) When the sequence of counting reaches 64, a 1 from the 1 output line of bistable FFC-14 is applied to even-numbered AND gates GAD-2 through GAD-12. The other input to each of these AND gates is a 0 from the 1 output line of bistables FFC-8 through FFC-13. Because only one input to each of the evennumbered AND gates is a high-level signal, the output of even-numbered AND gates GAD-2 through GAD-12 is a 0. Because the output from the odd-numbered gates is also a 0 (high-level input from each 1 output line), OR gates GOI-1 through GOI-6 are inhibited and the low-level output appears on the X1 through X6 lines as a 1 (111111).

- (4) The outputs of OR gates GOI-1 through GOI-6 are also inverted by inverters IN-5 through IN-10 and appear on the  $\overline{X1}$  through  $\overline{X6}$  lines as a 0 (000000). Thus, the outputs on the X lines are counts from zero to 63 and 63 to zero, and the outputs on the  $\overline{\mathbf{X}}$  lines are counts from 63 to zero and zero to 63 for each series of 128 pulses received from the timebase circuit. In addition to its use in complementing the outputs from bistables FFC-8 through FFC-13, bistable is used to trigger the earlylate circuits (para 1-23), and the early-late transition gates of the transition-control circuits (para 1-22), as well as to advance the baud counter in the baud distributor circuits (para 1-24).

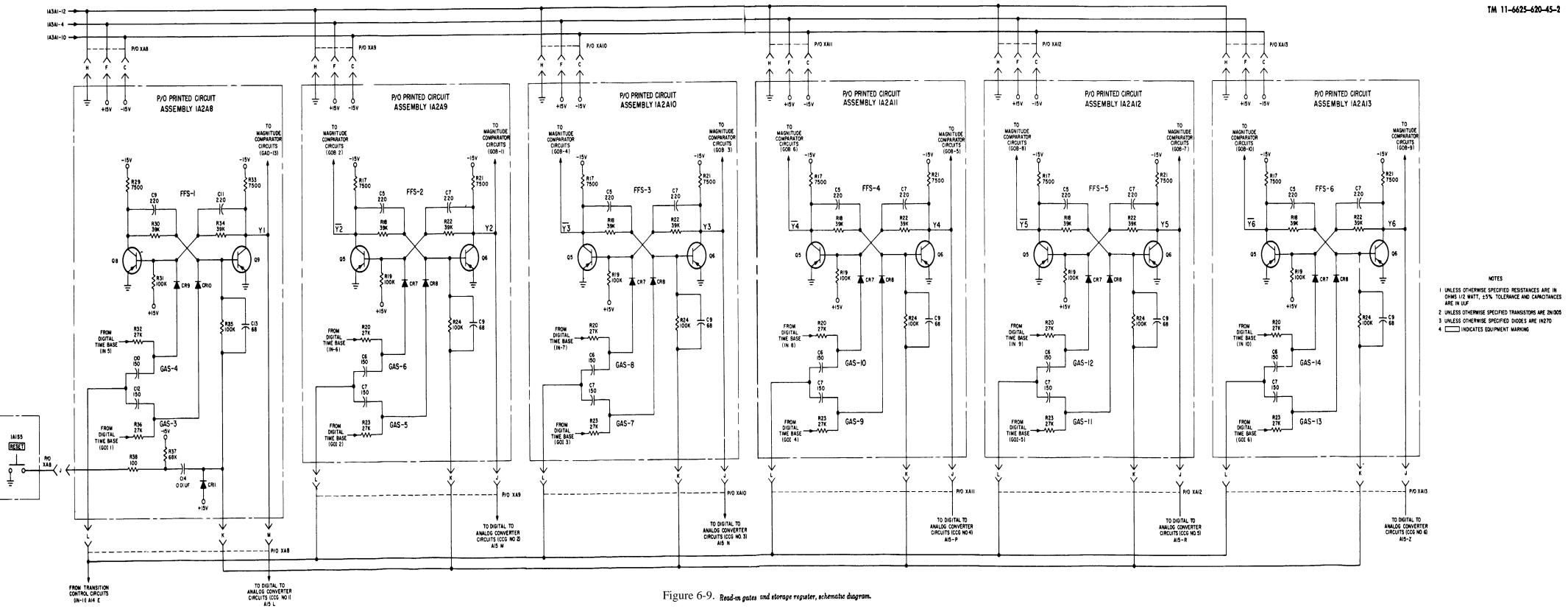

#### **1-18. Read-In Gates and Storage Register** (fig. 6-3)

a. Read-in gates GAS-3 through GAS-14, when enabled, apply input triggers to storage register bistables FFS-1 through FFS-6. The storage register bistables are thus set, or reset, depending on the condition of the X1 through X6 lines and the  $\overline{X1}$  through  $\overline{X6}$  lines in the digital time-base circuits. In order for the read-in gates to be enabled, two positive (high-level)

inputs must be applied. One of the inputs to the gates is from the digital time-base circuits; the other input is from transition-control AND gate GAI–15, through inverter IN–11 in the transition-control circuits.

b. AND gates GAS-3 through GAS-14 determine the number contained in the storage register. The X lines from the outputs of OR gates GOI-1 through GOI-6 provide one input to odd-numbered AND gates GAS-3 through GAS-13, and the  $\overline{X}$  lines from inverters IN-5 through IN-10 provide an input to even-numbered AND gates GAS-4 through GAS-14. The other input, common to all AND gates GAS-3 through GAS-3 through GAS-1, is received from transition-control gate GAI-15, through inverter IN-11 in the transition-control circuits (para 1-22). The X outputs of the AND gates are connected to the C (reset) input lines of bistables FFS-1 through FFS6.

c. The  $\overline{\mathbf{X}}$  outputs of the AND gates are connected to the S (set) input line of bistables FFS-1 through FFS-6. When a positive transition is applied to the common input line of AND gates GAS-3 through GAS-14<sub>A</sub> the AND gates that have a 0 on their X or X line place a 0 on the input to the storage register bistable to which they connect.

d. Thus, a 0 appearing on the X line causes a 0 to be stored in the associated storage register bistable, and a 0 appearing on the  $\mathbf{X}$  line causes a 1 to be stored in the associated storage register bistable. Therefore, the number placed in the storage register bistable is the output of the digital time-base counter as it appears on the X lines.

e. When RESET switch 1A1S5 is momentarily depressed, a ground potential is applied to the C (reset) input of each storage register bistable, which then resets the storage register to binary number 000000.

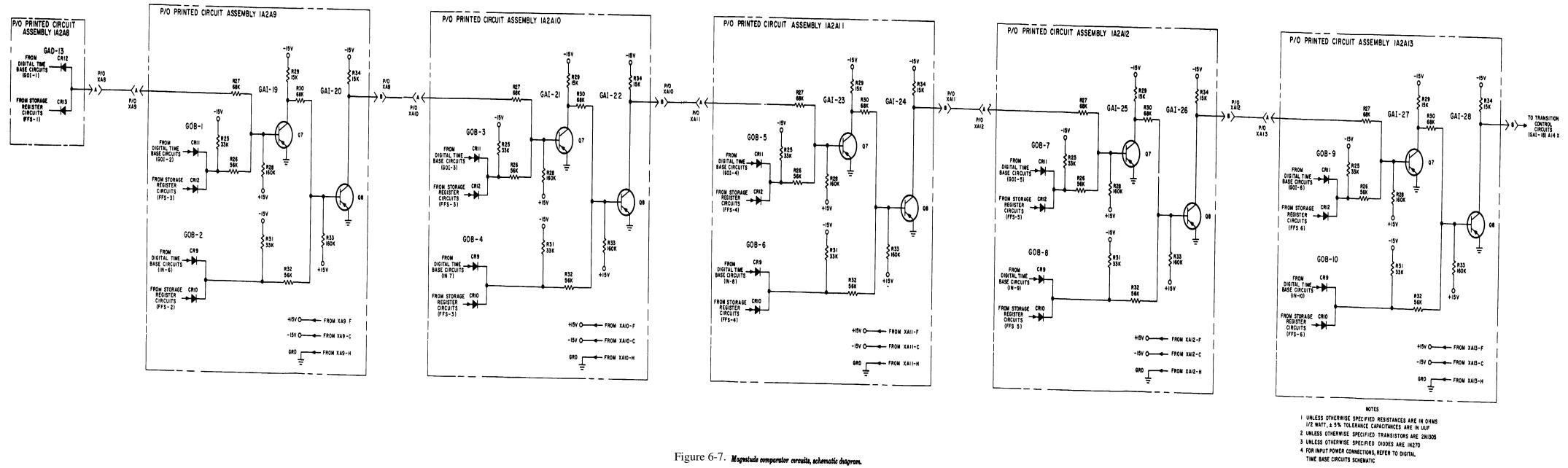

#### 1-19. Magnitude Comparator Circuits (fig. 6-3)

a. The magnitude comparator circuits compare the binary number stored at the  $\overline{\mathbf{Y}}$ lines of the storage registers with the binary number present at the X output lines of the digital time-base counter for each transition during peak distortion measurement-s. When the binary number held in the storage registers (Y lines) is larger than the binary number present at the output of the digital time-base counter (X lines), the magnitude comparator circuits prevent a new read-in from entering the storage registers. This insures an indication of maximum distortion on PERCENT DIS-TORTION meter 1A1M1 when measuring peak distortion.

b. When DISTORTION SELECT switch 1A1S7A is set to AVERAGE, a 1 is applied to comparison AND gate GAI-18. However, AND gate GAI-18 requires a 0 on each input line in order to apply a 1 to transition-control gate GAI-15. Therefore, with a 1 always applied to one input line, AND gate GAI-18 always applies a 0 to transition-control gate GAI-15 during average distortion measurement. Assuming each input of transition-control gate GAI-15 to be 0, the resultant 1 output will be inverted by inverter IN-11 and applied as a 0 to read-in AND gates GAS-3 through GAS-14. This will cause those readin gates with a 0 on the other input line to trigger the storage register.

C. When DISTORTION SELECT switch 1A1S7 is set to any other position, a 0 is applied to one input of AND gate GAI-18. The other input to AND gate GAI-18 is obtained from AND gate GAI-28 in the magnitude comparator circuits. When a 0 is received at the input of AND gate GAI-18 from AND gate GAI-28 (the binary number held in the storage register is greater than the binary number present at the output of the digital time-base counter), AND gate GAI-18 applies a 1 to transfer control gate GAI-15, Each input of transition-control gate GAI-15 must be a 0; therefore, the resulting output from inverter IN-11 will inhibit a read-in from the digital time-base counter to the storage register.

d. Thus, when a 1 output is present at AND gate GAI-28 (binary number held in the storage register is less than the binary number present at the output of the digital time-base counter), AND gate GAI-18 applies a 0 to transition-control gate GAI-15. When each input of transfer control gate GAI-15 is at 0, the output from inverter IN-11 enables a new read-in from the digital time-base counter to the storage register.

e. When the binary number stored at the  $\overline{\mathbf{Y}}$  lines of the storage register is smaller than the binary number present at the X lines of the digital time-base counter, the magnitude comparator circuits apply the 0 from the output of AND gate GAI-18 to transition-control gate GAI-15. Assume that the output on the X lines of the digital time-base counter is the binary number 20 (010100), and the binary number stored on the Y lines of the storage register is 13 (001101); then the binary number present on the  $\overline{\mathbf{X}}$  lines of the digital time-base counter would be 43 (101011) and the binary number stored on the Y lines of the storage register would be 50 (110010).

f. Reading from right to left in each of these binary numbers, the 0's and 1's would corrspend to the 0's and 1's present on the X1 through X6,  $\overline{Y1}$  through  $\overline{Y6,1}$  through  $\overline{X6}$ , and Y1 through Y6 lines, respectively. The X1 and Y1 inputs to AND gate GAD-13 would be 0 and 0, respectively, and the 0 output would be applied to the upper input of inverting AND gate GAI-19. The X2 and Y2 inputs to OR gate GOB-1 would be 0 and 1, respectively, and the 0 output would be applied to the lower input of inverting AND gate GAI-19.

g. The two 0 inputs produce a 1 in inverting AND gate GAI-19 output, which is then applied to the upper input of inverting AND gate GAI-20. The  $\overline{X2}$  and  $\overline{Y2}$  inputs to OR gate GOB-2 would be a 1 and 0, respectively, producing a 0 which would be applied to the other input of inverting AND gate GAI-20. With a 0 and a 1 present at the inputs of inverting AND gate GAI-20, a 0 would be pro duced and applied to the lower input of inverting AND gate GAI-21. The X3 and Y3. inputs of OR gate GOB-3 would be a 1 and 0, respectively, and the 0 output produced would be applied to inverting AND gate GAI-21.

h. With two 0 inputs, inverting AND gate GAI-21 would produce a 1 which would be applied to the upper input line of inverting AND gate GAI-22. The  $\overline{X3}$  and  $\overline{Y3}$  inputs of

OR gate GOB-4 would be 0 and 1, respectively, and the 0 output produced would be applied to inverting AND gate GAI-22. With a 1 and a 0 present at the inputs of inverting AND gate GAI-22, a 0 would be produced and applied to the lower input of inverting AND gate GAI-23. The X4 and Y4 inputs of OR gate GOB-5 would each be 0 and the resulting 0 output would be applied to the other input of inverting AND gate GAI-23.

i. With two 0 inputs, inverting AND gate GAI-23 would produce and apply to a 1 to the upper input of GAI-24. The X4 and Y4 inputs of OR gate GOB-6 would each be 1 and would apply the 1 produced in the output to the other input of inverting AND gate GAI-24. With two 1 inputs, inverting AND gate GAI-24 would apply a 0 to the lower input of inverting AND gate GAI-25. The X5 and Y5 inputs to OR gate GOB-7 would each to 1; therefore, a 1 would be applied to the other input of inverting AND gate GAI-25. With a 0 and a 1 present on the inputs of inverting AND gate GAI-25, a 0 would be produced and applied to the upper input of inverting AND gate GAI-26.

j. The  $\overline{X5}$  and  $\overline{Y5}$  inputs of OR gate GOB-8 would each be 0, and a 0 would be produced and applied to the other input of GAI-26. With two 0 inputs, inverting AND gate GAI-26 would apply a 1 to the lower input of inverting AND gate GAI-27. The X6 and Y6 inputs of OR gate GOB-9 would be 0 and 1, respectively; therefore, a 0 would be produced and applied to the other input of inverting AND gate GAI-27.

k. With a 0 and a 1 present on the inputs of inverting AND gate GAI-27, a 0 would be produced and applied to the upper input of AND gate GAI-28. The  $\mathbf{X6}$  and  $\mathbf{Y6}$  inputs of OR gate GOB-10 would be 1 and 0, respectively, and a 0 output produced would be applied to the other input of inverting AND gate GAI-28. With two 0 inputs, inverting AND gate GAI-28 would produce and apply a 1 to inverting AND gate GAI-18. Inverting AND gate GAI-18 would therefore apply a 0 to transition-control AND gate GAI-15, The output of transition-control AND gate GAI-15, which is inverted by inverter IN-11, triggers AND gates GAS-3 through GAS-14 to provide a new read-in from the digital time-base counter to the storage register.

l. When the binary number stored in the  $\overline{\mathbf{Y}}$  lines of the storage register is larger than the binary number present at the X lines of the digital time-base counter, the magnitude comparator circuits apply a 1 from the output of inverting AND gate GAI-18 to transition-control gate GAI-15. In this condition, transition-control gate GAI-15 cannot enable AND gates GAS-3 through GAS-14. Therefore, no read-in from the digital time-base counter to the storage register is possible.

m. Assume that the output on the X lines of the digital time-base counter is the binary 13 (001101) and the binary number stored on the  $\overline{\mathbf{Y}}$  lines of the storage register is 20 (010100); then the binary number present on the  $\overline{\mathbf{X}}$  lines of the digital time-base counter would be 50 (110010) and the binary number stored on the Y lines of the storage register would be 43 (101011).

n. When RESET switch 1A1S5 is momentarily depressed, a 0 is applied to the C input lines of the storage register (bistables FFS-1 through FFS-6). This resets the storage register to binary 000000, and PERCENT DIS-TORTION meter 1A1M1 will indicate zero. When RESET switch 1A1S5 is released, the number in the digital time-base counter will be read into the storage register, since the binary number stored at the  $\mathbf{Y}$  lines of the storage register is smaller than the binary number present at the X lines of the digital time-base circuits (c above).

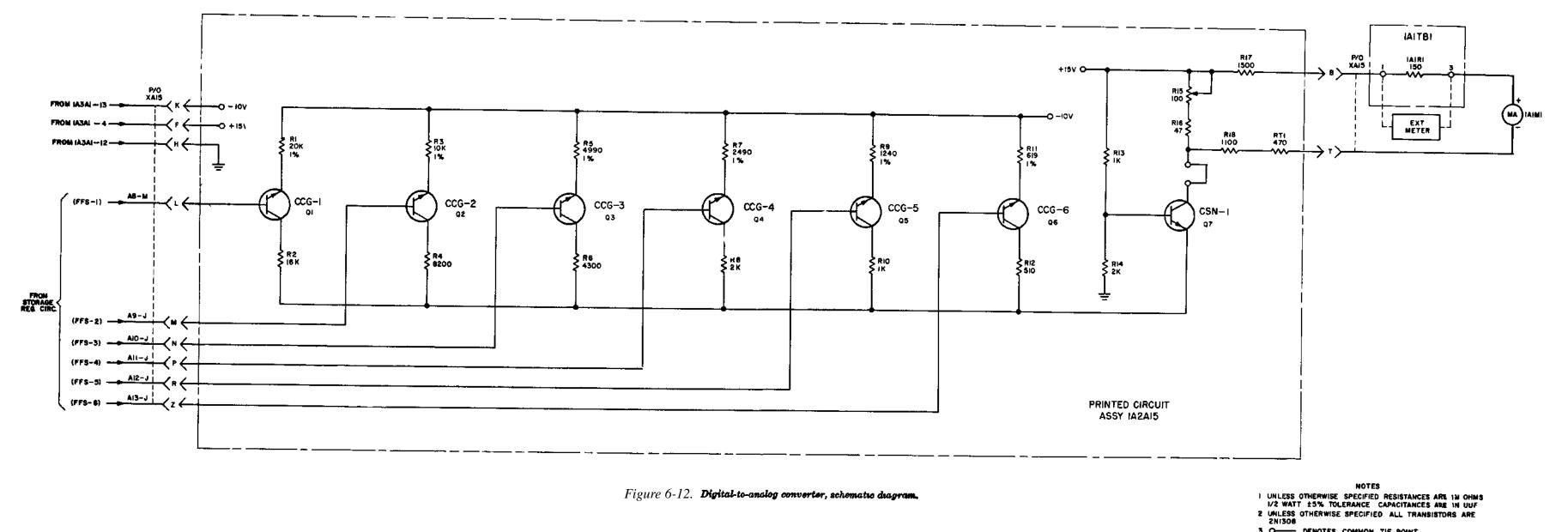

#### 1-20. Digital-to-Analog Converter Circuits (fig. 6-3)

a. The meter-drive circuits in the digitalto-analog converter circuits contain constantcurrent generators CCG-1 through CCG6. These constant-current generators convert the digital number (states of FFS-1 through FFS-6) stored in the storage-register bistables to an analog form (current level signals). Current summing network CSN-1 adds up the current levels and then attenuates the sum by a factor of 1/32 before applying the result to PER- CENT DISTORTION meter 1A1M1. PER-CENT DISTORTION meter 1A1M1 requires 1 milliampere to provide a full-scale deflection (50-PERCENT DISTORTION indication).

b. The binary number stored in the storageregister bistables (FFS-1 through FFS-6) on the Y1 through Y6 lines is applied direct to constant-current generators CCG-1 through CCG6, respectively. A 1 stored on the Y line in a particular storage register turns on the associated constant-current generator, and a 0 stored on the Y line turns it off. The largest number that can be held in the storage register is 63 (11111), which represents 49.2percent distortion. When a 1 is present on each Y line of the storage register, a total current of 31.5 milliamperes is applied to current summing network CSN-1. Current summing network CSN-1 then attenuates the current to 0.984 milliampere  $(31.5 \times 1/32)$ . This causes a deflection of 98.4 percent of full scale, or a reading of 49.2 PERCENT DISTORTION on meter 1A1M1.

#### 1-21. Transition-Sampler Circuits (fig. 6-3)

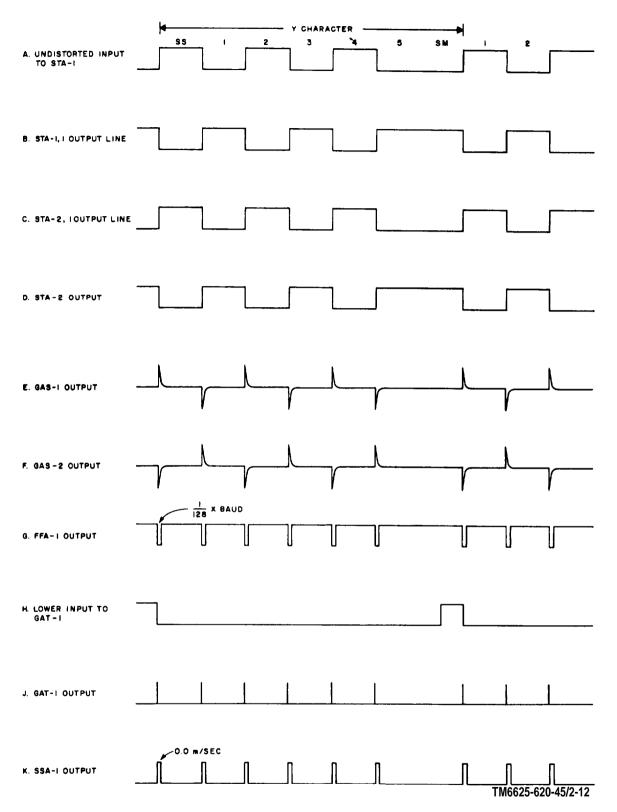

a. The transition-sampler circuits are controlled by DISTORTION SELECT switch 1A1S7 and DISTORTION SELECT switch 1A1S6. The transition-sampler circuits determine whether the distortion measurements involve all transitions, the space-to-mark transitions, or the mark-to-space transitions. When DISTORTION SELECT switch 1A1S7 is at TOTAL PEAK, a high-level 0 is applied to the lower inputs of AND gates GAS-1 and GAS-2. The other input to AND gate GAS-1 is obtained from the 1 output line of Schmitt trigger STA-2 (C, fig. 1-10), and the other input to AND gate GAS-2 is obtained from the 0 output line of Schmitt trigger STA-2(D, fig. 1-10). Thus, the 0 output line from STA-2, which is positive-going for a space-tomark transition (D, fig. 1-10), will enable AND gate GAS-2.

*b.* The 1 output line from STA-2, which is positive-going for a mark-to-space transition (C, fig. 1-10), will enable AND gate GAS-1. Thus, each AND gate, GAS-1 and GAS-2 (E and F, fig. 1-10), passes a transition, and both types of transitions are applied to bistable

FFA-1 as positive triggers. The positive signal transitions from AND gates GAS-1 and GAS-2 are applied to the S input of synchronizing bistable FFA-1.

c. Bistable FFA-1 and inverting AND gate GAI-3 then synchronize the transitions to be measured with the timing pulses from AND gate GAI-4 in the time-base circuits (para 1-7). The 0 output from bistable FFA-1 (G, fig. 1-10) is applied through AND gate GAT-1 to the input of monostable SSA-1. The output from monostable SSA-1 (J, fig. 1-10) is applied to transition-control gate GAI-15 to provide the proper read-in to the storage register bistables.

d. When a positive transition is applied to the C input of bistable FFA-1, the 1 output line provides a high level to AND gate GAI-3 and the 0 output line provides a low level to AND gate GAT-1. When the next positive timing pulse (timing pulses are 128 times the baud frequency), from AND gate GAI-4 is applied to AND gate GAI-3, GAI-3 is enabled and provides a low level, which has no effect, to FFA-1. When the timing pulse is removed, GAI-3 is inhibited and a high level is applied to the S input of bistable FFA-1. The 1 output line provides a low level to AND gate GAI-3 and the 0 output line provides a high level to AND gate GAT-1. AND gate GAT-1 is thus enabled and applies a low level to monostable SSA-1.

e. When the next positive transition is applied to the C input of bistable FFA-1, the 1 output line again provides a high level to AND gate GAI-3, and the 0 output line provides a low level to AND gate GAI-1. The next timing pulse will again set bistable FFA-1. Thus, when left-hand DISTORTION SELECT switch 1A1S7 is set to TOTAL PEAK, each transition of the input signal (A, fig. 1–10) is applied to monostable SSA-1 from AND gate GAT-1 (J, fig. 1-10),

f. When DISTORTION SELECT switch 1A1S7 is in any position other than TOTAL PEAK, DISTORTION SELECT switch 1A1S6A determines whether a mark/space or space/mark transition is applied to transitioncontrol gate GAI-15. When DISTORTION SELECT switch 1A1S6A is set to MARK/ SPACE, AND gate GAS-1 is enabled (E, fig.

Figure 1-10. Transition sampler circuits, timing diagram.

1-24

1-10) and AND gate GAS-2 is inhibited. Thus, the output from monostable SSA-1 will occur only during the mark-to-space transitions. When right-hand DISTORTION SELECT switch 1A1S6 is set to SPACE/MARK, AND gate GAS-1 is inhibited and AND gate GAS-2 is enabled (F, fig. 1–10). Thus, the output from monostable SSA-1 will ocurr during the space-to-mark transition.

#### **1-22. Transition-Control Circuits**

(fig. 6-3)

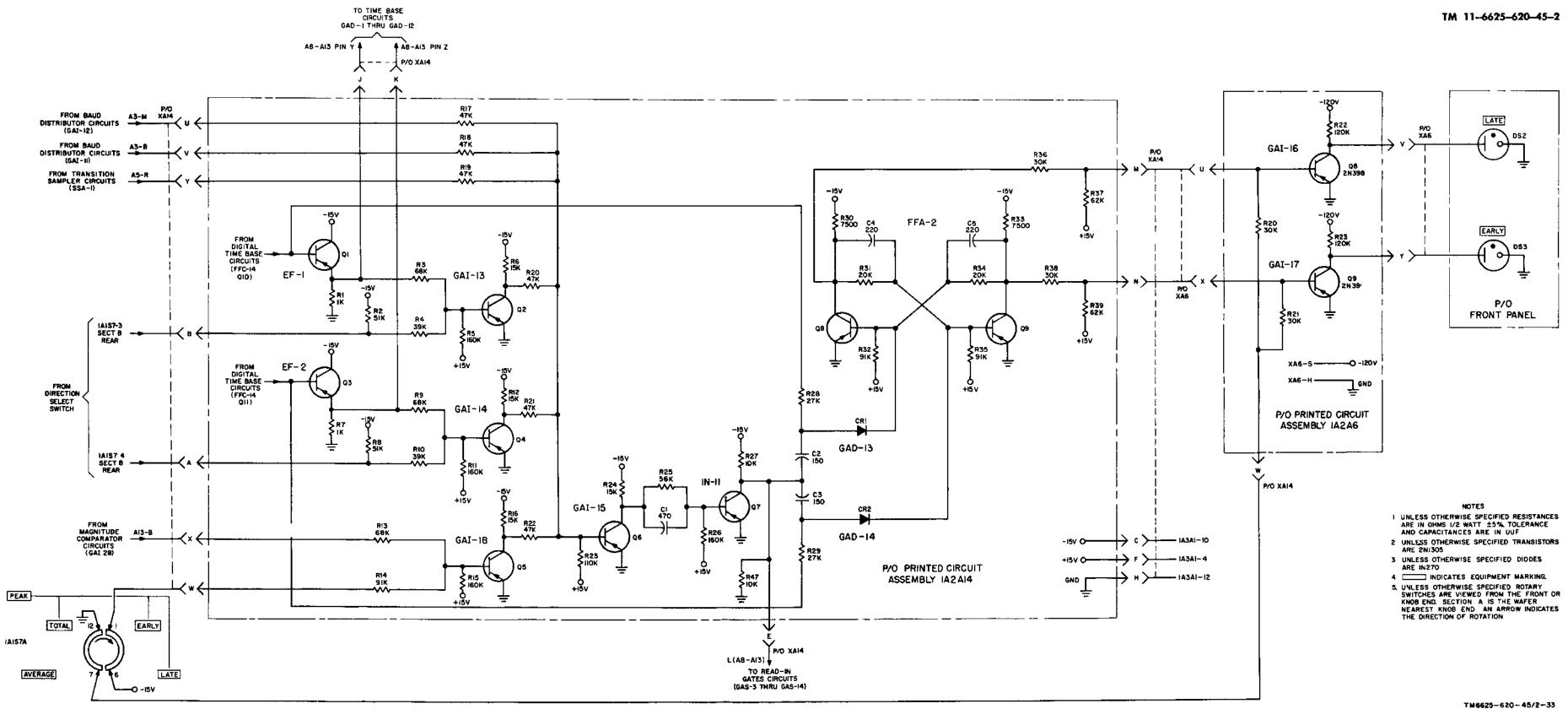

a. When DISTORTION SELECT switch 1A1S7A is set to AVERAGE, a low-level inhibit signal is applied to comparison AND gate GAI-18. Thus, AND gate GAI-18 applies a constant high-level enable signal to transition-control gate GAI-15 during average distortion measurements. When DISTORTION SELECT switch 1A1S7A is set to any other position, a high-level signal is applied through the switch to one input line of AND gate GAI-18.

b. The other input to comparison AND gate GAI-18 is obtained from AND gate GAI-28 in the magnitude comparator circuits (para 1-19). When the binary number held in the storage register is greater than the binary number present at the output of the digital time-base counter, AND gate GAI-28 provides a high-level output to AND gate GAI-18, which then applies a low-level enable signal to transition-control gate GAI-15. When the binary number held in the storage register is less than the binary number present at the output of the digital time-base counter, AND gate GAI-28 provides a low-level output to AND gate GAI-18, which then applies a highlevel inhibit signal to transition-control gate GAI-15.

c. When DISTORTION SELECT switch 1A1S7B is set to AVERAGE or TOTAL PEAK, a low-level signal is applied to early transition AND gate GAI-14 and to late transition AND gate GAI-13 (no switch connection provides -15 volts to the open lead). Early transition AND gate GAI-14 and late transition AND gate GAI-13 require highlevel inputs at the input lines in order to apply a low-level signal to transition-control gate GAI-15. Therefore, early transition AND gate GAD-14 and late transition AND gate GAI-13 apply a constant high-level signal to transition-control gate GAI-15 during average and total peak distortion measurements.

d. When DISTORTION SELECT switch 1A1S7A is set to EARLY PEAK, a high-level signal is applied to one input line of early transition AND gate GAI–14, and a low-level signal is applied to one input of late transition AND gate GAI–13. The other input to early transition AND gate GAI-14 is from the 1 output line of bistable FFC-14 in the digital time-base circuits (para 1–17). When a highlevel signal is present at the 1 output line of bistable FFC–14 in the digital time-base circuits (the digital time-base counter is counting from zero to 63), AND gate GAI–14 applies a low-level signal to transition-control gate GAI-15.

e. When a low-level signal is applied to the input of early transition AND gate GAI-14 from the digital time-base counter (digital time-base counter is counting from 63 to zero), AND gate GAI-14 applies a high-level signal to transition-control gate GAI-15. Thus, a high-level signal is present at the output of late transition AND gate GAI-13 at all times during early peak-distortion measurements, and a high-level signal is present at the output of early transition AND gate GAI-14 for only the 1/2 bit preceding each ideal transition time (early transitions), except during the stop-mark/start-space transition. When DIS-TORTION SELECT switch 1A1S7 is set to LATE peak, a high-level signal is applied to one input line of late transition AND gate GAI-13, and a low-level signal is applied to one input line of early transition AND gate GAI-14.

j. The other input to late transition AND gate GAI-13 is from the 0 output line of bistable FFC-14 in the digital time-base circuits. When a high-level signal is present at the 0 output line of bistable FFC-14 (the digital time-base counter is counting from 64 to 127), AND gate GAI-13 applies to a low-level signal to transition-control gate GAI-15.

g. When a low-level signal is present on the 0 output line of bistable FFC-14 (the digital time-base counter is counting from zero to 63), AND gate GAI–13 applies a high-level signal to transition-control gate GAI–15. Thus, a high-level signal is present at the output of early transition AND gate GAI–14 at all times during late peak-distortion measurements, and a high-level signal is present at the output of late transition AND GATE GAI–13 for only the 1/2 bit following each ideal transition time (late transitions),

h. Transition-control gate GAI-15 controls the read-in gates to insure that the storate register will provide the proper output, through the meter drive circuits, to PERCENT DIS-TORTION meter 1A1M1, for the type of distortion measurement being made. The output transition-control AND gate GAI-15 is applied through inverter IN-11 to read-in gates GAS-3 through GAS-14 (para 1–18) and to early selection AND gate GAD-3 and late selection AND gate GAD-4 in the early-late circuits (para 1-23).

i. When a high-level signal is applied to the read-in gates, the gates are enabled, and when a low-level signal is applied to the read-in gates, the gates are inhibited. To enable the read-in gates, all high-level inputs must be present at transition-control gate GAI-15.

j. Because transition-control gate GAI-15 is controlled by the outputs of six other circuits, the read-in gates will be enabled only when the proper timing waveforms are present on the input lines of transition-control gate GAI-15. The relationship between the various input and output waveforms at transitioncontrol gate GAI-15, when various distortion measurements are made with the distortion analyzer, is discussed in (1) through (4) below.

k. The six inputs to transition-control gate GAI-15 are as follows: Two inputs are from AND gates GAI-14 and GAI-13 (c above); two inputs are from AND gates GAI-11 AND GAI-12 in the baud distributor circuits (para 1-24); one., input is from monostable SSA-1 in the transition-sampler circuits (para 1-21); and the last input is from AND gate GAI-18 (a above).

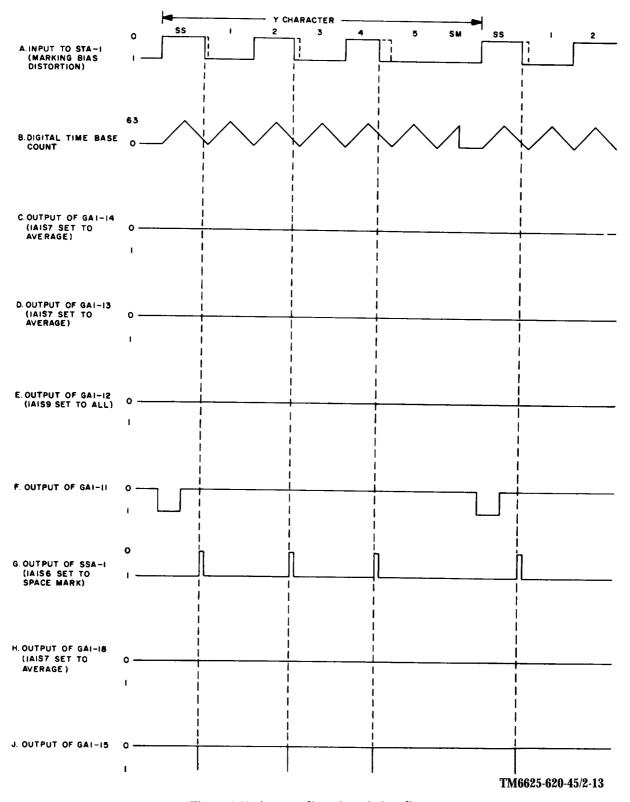

(1) Average distortion measurements.

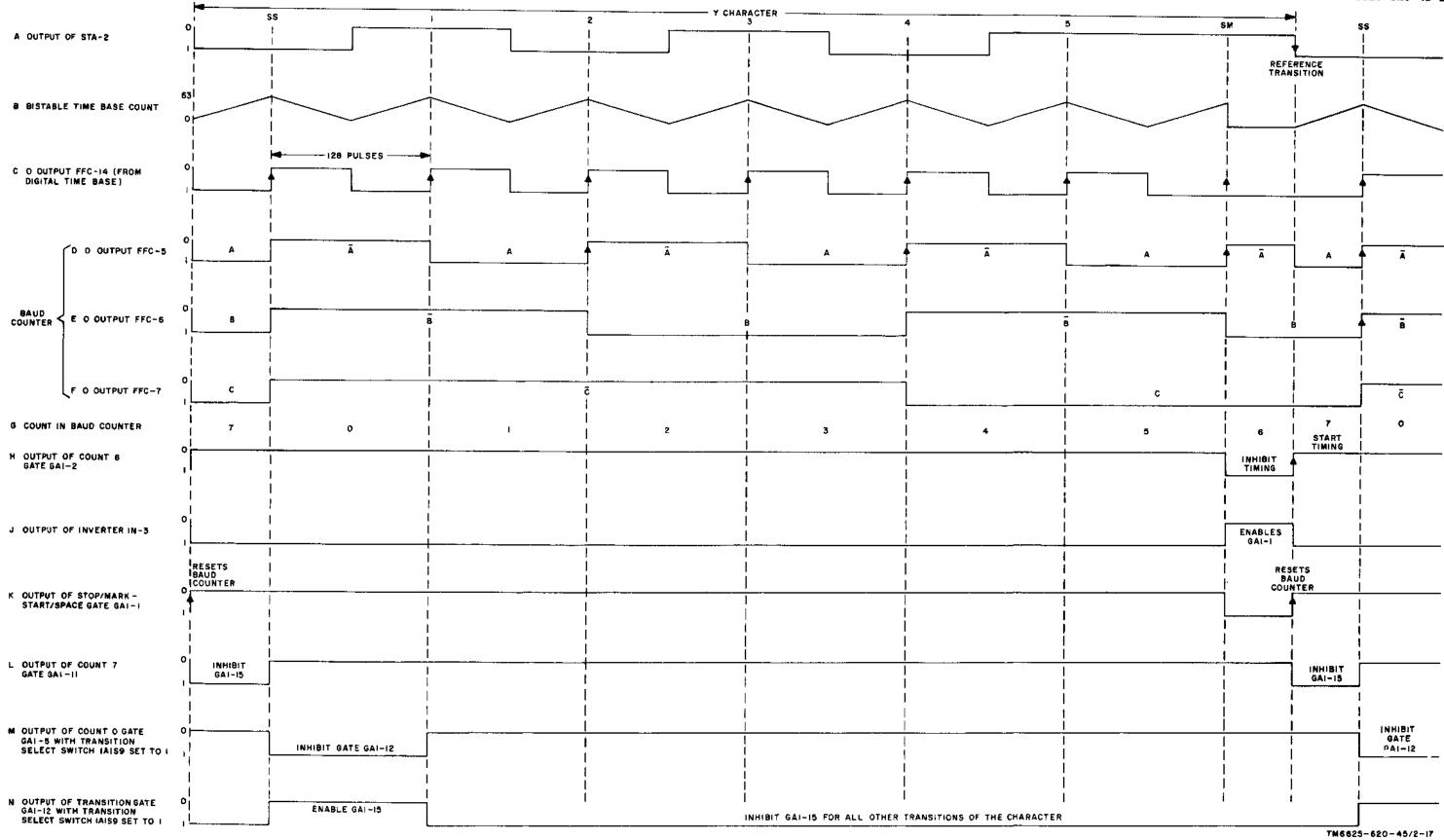

Waveforms C through H in figure 1-11 at the input to transition-control gate GAI-15 are representative of the waveforms present during the analysis of a character, with DIS-TORTION SELECT switch 1A1S7 set to AVERAGE and DISTORTION SELECT switch 1A1S6 set to SPACE/MARK. Waveform J, figure 1–11 represents the waveform present at the output of GAI–15. Other waveforms shown are A, which represents a distorted Y-character signal present at the input of STA–1, and waveform B, which shows the time relationships of the count in the digital time-base counter with respect to the other waveforms.

- (a) The zero points on waveform B correspond to the time when transitions would occur in an ideal character waveform. Waveforms C and D, figure 1-11 indicate that a 0 is present at all times at the early transition AND gate GAI-14 and at late transition AND gate GAI-13. When TRANSITION SELECT switch 1A1S9 is set to ALL, a high-level signal is present at all times at the transition gate GAI-12 output (waveform E).

- (b) A high-level input is also present from the count seven AND gate GAI-11 in the baud distribution circuits (para 1-23), except during the first 1/2-bit period of the character (waveform F), thus inhibiting transition-control gate GAI-15 (fig. 5-4) during the stop-mark/ start-space transition. Because a high-level signal is present at all times from comparison AND gate GAI-18 (waveform H, fig. 1-11), and because a high-level input from the monostable SSA-1 in the transition-sampler circuits (para 1-8) is present only during the space/mark transition (waveform G) of the character, transition-control gate GAI-15 is enabled only during the space/mark transitions of the character (waveform J).

- (c) When DISTORTION SELECT switch 1A1S7 is set to AVERAGE and DISTORTION SELECT switch 1A1S6 is set to MARK/SPACE, the waveforms shown in A through F and H of fig. 1-11 would be the same. The output of monostable SSA-1 (waveform G) would enable transition-control gate GAI-15 only during the mark/space transitions (except for the stopmark/start-space transition).

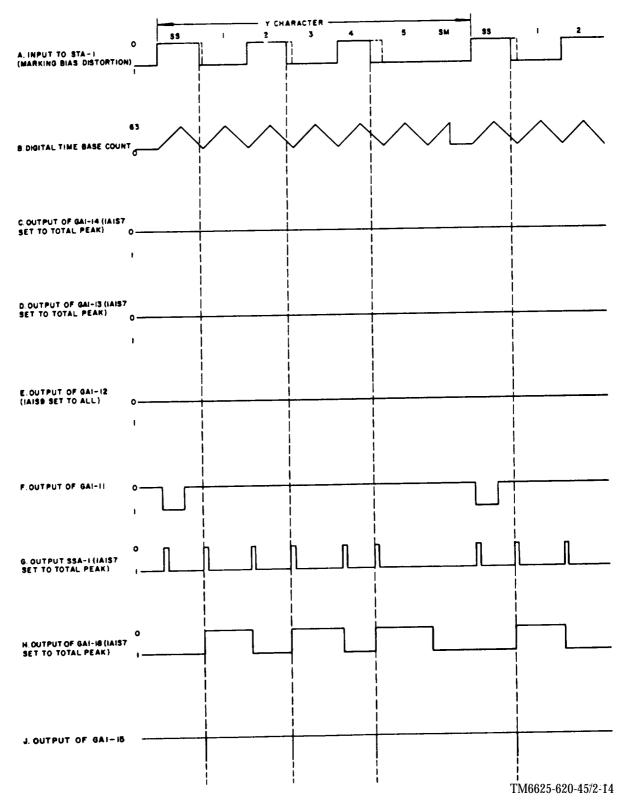

- (2) Total peak-distortion measrements. The waveforms shown in figure 1-12 are typical of those present during the analysis of a Y-character when left-hand DISTORTION SELECT switch 1A1S7 is set to TOTAL PEAK. Waveforms A through F of figure 1-12 are the same as those in figure 1-11 and have been described in (1) above.

- (a) A high-level input from monostable SSA-1 in the transition-sampler circuits is present at the input of GAI-15 for each mark/space and space/mark transition (waveform G, fig. 1–11). The output from the comparison AND gate GAI-18 will be a high level only when the count in the storage register is smaller than the count in the digital time-base counter.

- (b) The duration of the high-level output from comparison AND gate GAI-18 (waveform H) therefore, depends on the amount of distortion present in the input signal (waveform A). Thus, transitioncontrol gate GAI-15 will be enabled only when the high-level inputs of monostable SSA-1 waveform G) and comparison AND gate GAI-18 are in coincidence (waveform J).

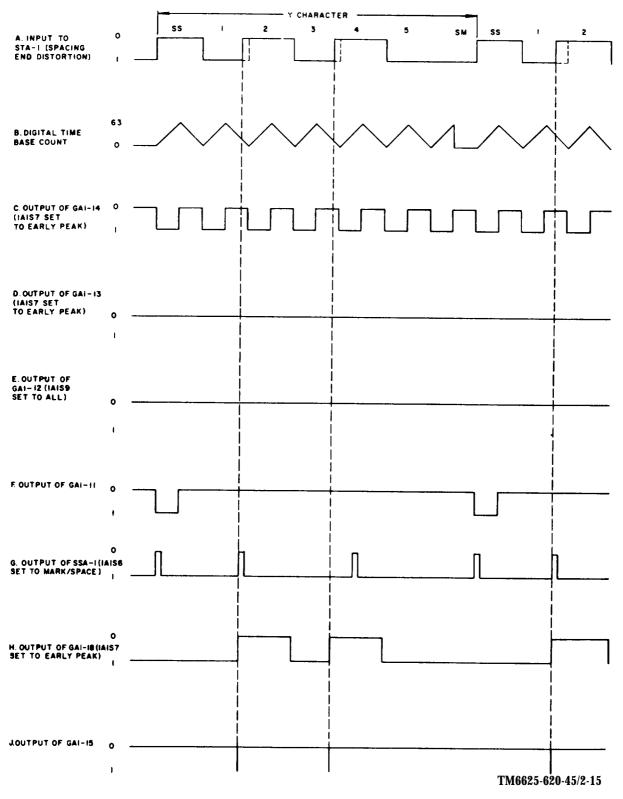

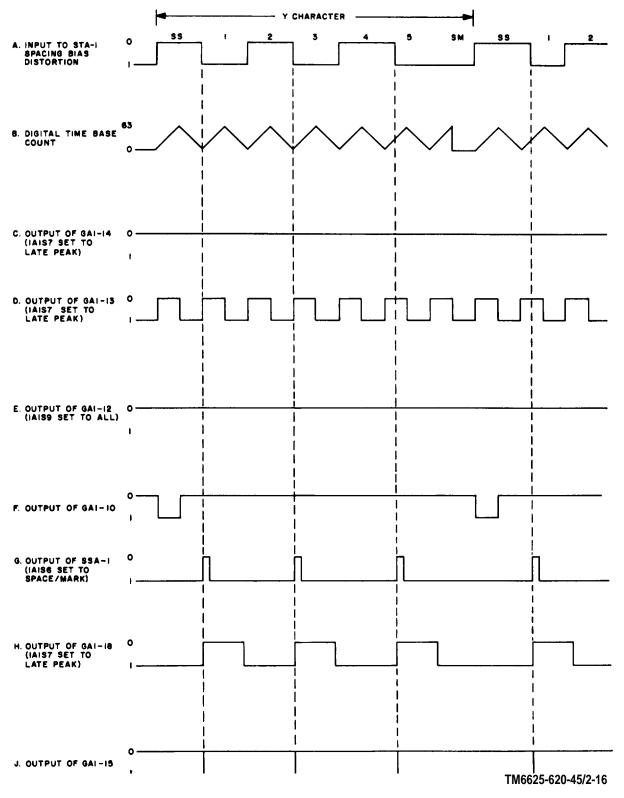

- (3) Early peak-distortion measurement. The waveforms shown in figure 1-13 are typical of those presented during the analysis of a Y-character when DISTORTION SELECT switch

1A1S7 is set to EARLY PEAK and DISTORTION SELECT switch 1A1S6 is set to MARK/SPACE.