# **TECHNICAL MANUAL**

# OPERATOR' S, ORGANIZATIONAL,

# AND DIRECT SUPPORT

# MAINTENANCE MANUAL

# INTERFACE UNIT TEST SET TS-4221/U (NSN 6625-01-323-3125) (EIC: N/A)

This publication is required for official use or for administrative or operational purposes only. Distribution is limited to US Government agencies. Other requests for this document must be referred to Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: AMSEL-LC-LM-LT, Fort Monmouth, New Jersey 07703-5007.

DESTRUCTION NOTICE - Destroy by any method that will prevent disclosure of contents or reconstruction of the document.

| INTRODUCTION |     |

|--------------|-----|

| PAGE         | 1-1 |

OPERATING INSTRUCTIONS PAGE

2-1

OPERATOR MAINTENANCE PAGE 3-1

ORGANIZATIONAL MAINTENANCE PAGE 4-1

DIRECT SUPPORT MAINTENANCE PAGE 5-1

APPENDIX A REFERENCES PAGE

APPENDIX B MAINTENANCE ALLOCATION PAGE A-1

**B-1**

TM 11-6625-3150-13 C1

HEADQUARTERS DEPARTMENT OF THE ARMY Washington, DC, 1 March 1997

## Operator's, Unit, And Direct Support Maintenance Manual

## INTERFACE UNIT TEST SET TS-4221/U (NSN 6625-01-323-3125) (EIC: N/A)

TM 11-6625-3150-13, 15 March 1992, is changed as follows:

1. Remove old pages and insert new pages as indicated below. New or changed material is indicated by a vertical bar in the margin of the page. Added or revised illustrations are indicated by miniature pointing hands

| Remove Pages                                            | Insert Pages                                                                               |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------|

| A and B                                                 | A and B                                                                                    |

| 1-0                                                     | 1-0                                                                                        |

| 1-3 through 1-12                                        | 1-3 through 1-12                                                                           |

| None                                                    | 1-12.1 and 1-12.2                                                                          |

| 1-13 and 1-14                                           | 1-13 and 1-14                                                                              |

| 1-63 through 1-66                                       | 1-63 through 1-66                                                                          |

| 2-1 and 2-2                                             | 2-1 and 2-2                                                                                |

| 4-3 through 4-8                                         | 4-3 through 4-8                                                                            |

| 4-9/(4-10 blank)                                        | 4-9/(4-10 blank)                                                                           |

| 5-1 through 5-4                                         | 5-1 through 5-4                                                                            |

| None                                                    | 5-4.1 and 5-4.2                                                                            |

| 5-5 and 5-6                                             | 5-5 and 5-6                                                                                |

| 5-17 and 5-18                                           | 5-17 and 5-18                                                                              |

| 5-23 through 5-36<br>5-41 and 5-42<br>5-43 through 5-52 | 5-23 through 5-36<br>(5-41 blank)/5-42<br>5-43 through 5-52<br>P.1 through P.7/(P.8 blank) |

| B-1 through B-8                                         | B-1 through B-7/(B-8 blank)                                                                |

| FO-1 (Sheet 1 of 2)                                     | FO-1 (Sheet 1 of 2)                                                                        |

| FO-1 (Sheet 2 of 2)                                     | FO-1 (Sheet 2 of 2)                                                                        |

| FO-2                                                    | FO-2                                                                                       |

| None                                                    | FO-17                                                                                      |

| Cover                                                   | Cover                                                                                      |

2. File this change sheet in front of the publication for reference purposes.

This publication is required for official use or for administrative or operational purposes only. Distribution is limited to US Government agencies. Other requests for this document must be referred to Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: AMSEL-LC-LEO-E-EQ-P, Fort Monmouth, New Jersey 07703-5007.

DESTRUCTION NOTICE -- Destroy by any method that will prevent disclosure of contents or reconstruction of the document.

Change

No. 1

DENNIS J. REIMER General, United States Army Chief of Staff

Official:

Joel B. Hulm

JOEL B. HUDSON Administrative Assistant to the Secretary of the Army 04314

**DISTRIBUTION:**

To be distributed in accordance with the initial distribution number (IDN) 369224 requirements for TM 11-6625-3150-13.

SAFETY STEPS TO FOLLOW IF SOMEONE IS THE VICTIM OF ELECTRICAL SHOCK

DO NOT TRY TO PULL OR GRAB THE INDIVIDUAL

IF POSSIBLE, TURN OFF THE ELECTRICAL POWER

IF YOU CANNOT TURN OFF THE ELECTRICAL POWER, PULL, PUSH, OR LIFT THE PERSON TO SAFETY USING A DRY WOODEN POLE OR A DRY ROPE OR SOME OTHER INSULATING MATERIAL

SEND FOR HELP AS SOON AS POSSIBLE

AFTER THE INJURED PERSON IS FREE OF CONTACT WITH THE SOURCE OF ELECTRICAL SHOCK, MOVE THE PERSON A SHORT DISTANCE AWAY AND IMMEDIATELY START ARTIFICIAL RESUSCITATION

#### SAFETY SUMMARY

### WARNING

- Soldering operations can cause serious burns and eye injuries. Gloves, safety glasses, and protective apron are required (para 5-13, 5-14, 5-15, 5-19, 5-20 and 5-21).

- Zinc chromate dust primer is highly toxic to eyes, skin, and respiratory tract. Eye and skin protection required. Good general ventilation is normally adequate (para 5-22).

- Isopropyl alcohol is flammable and moderately toxic to eyes, skin, and respiratory tract. Eye and skin protection required. Good general ventilation is normally adequate (para 5-22).

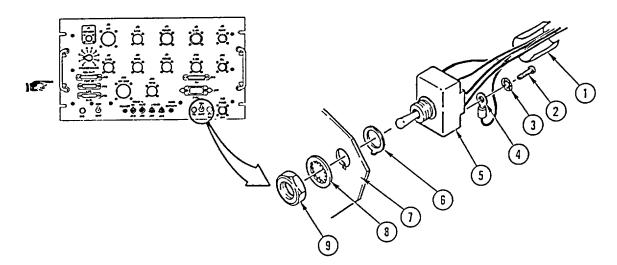

- Set POWER ON/OFF switch to OFF, unplug ac power cord, before removing fuse cover to prevent electrical shock (para 4-9).

- When lifting or handling heavy objects, use two people to prevent possible back injury (para 5-8, 5-16).

- Capacitors hold voltages after power is removed. Ground C1 before working inside IUTS to prevent injury to personnel (para 5- 8, 5-11, 5-16).

### HOW TO USE THIS MANUAL

- 1. HOW DO I FIND INFORMATION? To help you locate information, this manual has three types of indexes.

- <u>a</u>. <u>Front Cover</u>. Use front cover index and black tabs at the edge of pages to quickly find the chapters or this manual shown on the cover.

- b. <u>Table of Contents</u>. Entries within the main table of contents duplicate the entries on the front cover and are highlighted. This is in case the cover is torn off or soiled beyond legibility.

- c. <u>Chapter Indexes</u>. These indexes are located in the front of each chapter. The listings are in the order of appearance.

- 2. HOW DO I BECOME FAMILIAR WITH THE EQUIPMENT? See chapter 1 for physical and functional descriptions.

- 3. **DOES THE MANUAL CONTAIN OPERATOR INSTRUCTIONS?** See chapter 2 and 3.

- 4. WHAT IS THE EXTENT OF ORGANIZATIONAL MAINTENANCE? See chapter 4. Normally, organizational maintenance is limited to quarterly preventive maintenance checks and services and replacement of defective line replaceable units (LRUs).

- 5. WHERE IS DIRECT SUPPORT MAINTENANCE COVERED? See chapter 5.

- 6. **ARE OTHER MANUALS REQUIRED?** Refer to appendix A for a list. Obtain these manuals through supply channels.

- 7. WHAT TOOLS AND EQUIPMENT ARE REQUIRED? Turn to appendix B (Maintenance Allocation) for a listing.

- 8. **HOW DO I GET SPARE PARTS?** Refer to paragraph 4-3 and 5-3.

- 9. WHAT ACTIONS ARE TAKEN IF MISTAKES ARE FOUND IN THE MANUAL? See the block on the table of contents and paragraph 1-3 for procedures.

### HOW TO USE THIS MANUAL - Continued

- 10. **DO I NEED TO KNOW ANY SPECIAL SAFETY INSTRUCTIONS?** Ensure you understand the information on page A and B before you operate or maintain the equipment.

- 11. WHAT OTHER FEATURES SHOULD I KNOW ABOUT THIS MANUAL? You should know the use of NOTES, CAUTIONS, AND WARNINGS. Definitions are:

### NOTE

An essential operating or maintenance procedure, caution, or statement which must be highlighted.

### CAUTION

An operating or maintenance procedure, practice, condition, statement, etc., which, if not strictly observed, could result in damage to, or destruction of, equipment or loss of mission effectiveness or long term health hazards to personnel.

#### WARNING

An operating or maintenance procedure, practice, condition, statement, etc., which, if not strictly observed, could result in INJURY to or DEATH of personnel.

D

**Technical Manual**

No. 11-6625-3150-13

HEADQUARTERS, DEPARTMENT OF THE ARMY Washington, DC 15 March 1992

## OPERATOR'S, ORGANIZATIONAL, AND DIRECT SUPPORT MAINTENANCE MANUAL TEST SET, INTERFACE UNIT TS-4221/U (NSN 6625-01-323-3125) (EIC: N/A)

## REPORTING ERRORS AND RECOMMENDING IMPROVEMENTS

You can help improve this manual. If you find any mistakes, or if you know of a way to improve the procedures, please let us know. Mail your letter, DA Form 2028 (Recommended Changes to Publications and Blank Forms) or DA Form 20282 located in back of this manual direct to: Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: AMSEL-LC-LM-LT, Fort Monmouth, New Jersey 07703-5007.

In either case a reply will be furnished direct to you.

|         |    | HOW TO USE THIS MANUAL                                    | С    |

|---------|----|-----------------------------------------------------------|------|

| CHAPTER | 1  | INTRODUCTION                                              |      |

| Section | I  | General Information                                       | 1-1  |

|         | II | Equipment Description                                     | 1-5  |

|         | Ш  | Technical Principles of Operation                         | 1-11 |

| CHAPTER | 2  | OPERATING INSTRUCTIONS                                    | 2-1  |

| Section | I  | Description and Use of Operator's Controls and Indicators | 2-1  |

| Section | II | Operation Under Unusual Conditions                        | 2-3  |

| Section | Ш  | Operation Under Unusual Conditions                        | 2-3  |

| CHAPTER | 3  | OPERATOR MAINTENANCE                                      | 3-1  |

# Page

# CHAPTER 4 ORGANIZATIONAL MAINTENANCE

| Section  | <br>  <br>   <br> V  | Repair Parts, Special Tools, TMDE,<br>and Support Equipment<br>Service Upon Receipt<br>Preventive Maintenance Checks and Services (PMCS)<br>Maintenance | 4-1<br>4-2<br>4-2<br>4-7   |

|----------|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| CHAPTER  | 5                    | DIRECT SUPPORT MAINTENANCE                                                                                                                              |                            |

| Section  | I<br>II<br>III<br>IV | Repair Parts, Special Tools, TMDE,<br>and Support Equipment<br>Troubleshooting<br>Maintenance<br>Preparation for Storage or Shipment                    | 5-2<br>5-2<br>5-22<br>5-56 |

| APPENDIX | Α                    | REFERENCES                                                                                                                                              | A-1                        |

# APPENDIX B MAINTENANCE ALLOCATION

| Section | I   | Introduction                          | B-1 |

|---------|-----|---------------------------------------|-----|

|         | П   | Maintenance Allocation Chart          | B-5 |

|         | 111 | Tools and Test Equipment Requirements | B-6 |

|         | IV  | Remarks                               | B-7 |

# ii/(iii blank)

INTERFACE UNIT TEST SET TS-4221/U

# **CHAPTER 1**

### INTRODUCTION

| CHAPTER CONTENTS |      |                                                         | Pag  |

|------------------|------|---------------------------------------------------------|------|

| Section          | I    | General Information                                     |      |

|                  | 1-1  | Scope                                                   | 1-1  |

|                  | 1-2  | Maintenance Forms, Records, and Reports                 |      |

|                  | 1-3  | Reporting Equipment Improvement Recommendations (EIR)   | 1-2  |

|                  | 1-4  | Consolidated Index of Army Publications and Blank Forms | 1-2  |

|                  | 1-5  | Administrative Storage                                  | 1-2  |

|                  | 1-6  | Destruction of Army Electronics Materiel                | 1-2  |

|                  | 1-7  | Reference Information                                   | 1-2  |

|                  | 1-8  | Safety, Care, and Handling                              |      |

| Section          | П    | Equipment Description                                   |      |

|                  | 1-9  | Characteristics, Capabilities, Features                 | 1-5  |

|                  | 1-10 | Location and Description of Major Components            |      |

|                  | 1-11 | Equipment Data                                          |      |

| Section          | 111  | Technical Principles of Operation                       |      |

|                  | 1-12 | Overview                                                | 1-11 |

|                  | 1-13 | Detailed Operation                                      | 1-12 |

## Section I. Introduction

### 1-1. SCOPE

<u>Type of Manual</u>: Operator's, Organizational, and Direct Support Maintenance

Model Number and Equipment Name: TS-4221/U - Interface Unit Test Set

<u>Purpose of Equipment</u>: Used to test the interface unit (IU), computer processor (CP), and receiver, digital control (RDC).

# **1-2. MAINTENANCE FORMS, RECORDS, AND REPORTS**

a. <u>Reports of Maintenance and Unsatisfactory Equipment</u>. Department of the Army forms and procedures used for equipment maintenance will be those prescribed by DA Pam 738-750, as contained in Maintenance Management Update.

b. <u>Reporting of Item and Packaging Discrepancies</u>. Fill out and forward SF 364 (Report of Discrepancy (ROD)) as prescribed in AR 735-11-2/DLAR 4140.55/ SECNAVINST 4355. 18/AFR 400-54/MCO 4430.3J.

## 1-2. MAINTENANCE FORMS, RECORDS, AND REPORTS - Continued

c. <u>Transportation Discrepancy Report (TDR) (SF 361).</u> Fill out and forward Transportation Discrepancy Report (TDR) (SF 361) as prescribed in AR 55-38/NAVSUPINST 4610.33C/AFR 75-18/MCO P4610.19D/DLAR 4500.15.

## 1-3. REPORTING EQUIPMENT IMPROVEMENT RECOMMENDATIONS (EIR)

If your equipment needs improvement, let us know. Send us an EIR. You, the user, are the only one who can tell us what you don't like about your equipment. Let us know why you don't like the design or performance. Put it on an SF 368 (Product Quality Deficiency Report). Mail it to: Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: AMSEL-ED-PH, Fort Monmouth, New Jersey 07703-5007. We'll send you a reply.

### 1-4. CONSOLIDATED INDEX OF ARMY PUBLICATIONS AND BLANK FORMS

Refer to the latest issue of DA Pam 25-30 to determine whether there are new editions, changes, or additional publications pertaining to the equipment.

### 1-5. ADMINISTRATIVE STORAGE

Administrative storage of equipment issued to and used by Army activities will have Preventive Maintenance Checks and Services (PMCS) performed before storing. When removing the equipment from administrative storage, the PMCS checks should be performed to assure operational readiness.

### 1-6. REPORTING EQUIPMENT IMPROVEMENT RECOMMENDATIONS (EIR)

If your equipment needs improvement, let us know. Send us an EIR. You, the user, are the only one who can tell us what you don't like about your equipment. Let us know why you don't like the design or performance. Put it on an SF 368 (Product Quality Deficiency Report). Mail it to: Commander, US Army Communications-Electronics Command and Fort Monmouth, ATTN: AMSEL-ED-PH, Fort Monmouth, New Jersey 07703-5007. We'll send you a reply.

### 1-7. REFERENCE INFORMATION

This listing includes the nomenclature cross reference list and list of abbreviations used in this manual.

a. Nomenclature Cross Reference List

| Common Name                | Official Nomenclature                         |

|----------------------------|-----------------------------------------------|

| Computer processor (CP)    | Computer Processor<br>CP-1692/U               |

| Frequency synthesizer (FS) | Frequency Synthesizer<br>O-1833/U             |

| IF processor (IFP)         | Intermediate Frequency<br>Processor CV-4008/U |

# 1-7. REFERENCE INFORMATION - Continued

| Common Name                                   | Official Nomenclature                                  |

|-----------------------------------------------|--------------------------------------------------------|

| IF switch (IFS)                               | Intermediate Frequency Switch SA-2542/U                |

| Interface unit (IU)                           | Interface Unit J-4522/U                                |

| Interface unit test set (IUTS)                | Interface Unit Test Set TS-4221/U                      |

| NAV Set                                       | Carousel IV-E High-Accuracy Inertial Navigation System |

| Operator terminal                             | Alphanumeric Display Station HP2645A                   |

| Radio frequency antenna (RFA)                 | Radio Frequency Antenna AS-3901/U                      |

| Receiver digital control (RDC)                | Control, Receiver C- 11634/U                           |

| Receiver PS                                   | Power Supply-Receiver PP- 8184/U                       |

| System PS                                     | Power Supply PP-8158/U                                 |

| Wide band data link                           | Interoperable Airborne Data Link                       |

| Oscillator (OSC) (G1)                         | Assy, Oscillator Rubidium (G1)                         |

| Tick generator (A2)                           | CCA, Tick Generator (A2) (C5090411)                    |

| Computer processor interface (CPIF)<br>(A3)   | CCA, Computer Processor Interface (A3)<br>(C5116808)   |

| Computer processor simulator<br>(CP SIM) (A4) | CCA, Computer Processor Simulator (A4)<br>(C5117002)   |

| Test set digital/analog (TSD/A) (A5) (A6)     | CCA, Test Set Digital/Analog (A5) (A6) (C5117012)      |

| Test set, IF processor (TSIFP) (A7)           | CCA, Test Set IF Processor (A7) (C5117017)             |

| Test set local oscillator (TSLO) (A8)         | CCA, Test Set, Local Oscillator (AS) (C5117022)        |

| Test set radio frequency (TSRF) (A9)          | CCA, Test Set Radio Frequency (A9) (C5117027)          |

| 1553B interface (1553B IF) (A10)              | CCA, 1553B Interface (A10) (SM-D-873904)               |

| IU data link (IUDL) (A11)                     | CCA, Interface Unit Data Link (A11) (SM-D-873900)      |

| IU navigation (IUNAV) (A12)                   | CCA, Interface Unit Navigation (A12) (SM-D-873908)     |

| Test set bus (TSBUS) (A13)                    | CCA, Test Set Bus (A13) (C5117007)                     |

| Dual bus processor (DBP) (A14)                | CCA, Dual Bus Processor (A 14) (C5116888)              |

# 1-7. REFERENCE INFORMATION - Continued

<u>b</u>.

| Programmable static random-access<br>memory (PSRAM) (A15) | CCA, Programmable Static<br>Random-Access Memory (A15) (C5117032)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Power supply (A17)                                        | Power Supply (A17) (C5118502)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| List of Abbreviations.                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| CP                                                        | Computer processor<br>first-in-first out memory<br>Frequency synthesizer<br>general purpose interface bus<br>global positioning satellite<br>IF processor<br>IF switch<br>Interface unit<br>Interface unit test set<br>local oscillator<br>Megahertz<br>Pulse generator control<br>Radio frequency antenna<br>Receiver digital control<br>Read-only memory<br>Oscillator (G1)<br>computer processor interface (A3)<br>computer processor simulator (A4)<br>Test Set D/A (A5) (A6)<br>Test Set IF Processor (A7)<br>Test set local oscillator (A8)<br>Test set radio frequency (A9)<br>Transistor-transistor logic<br>Universal time interval counter<br>1553B interface (A10)<br>IU data link (A11)<br>IU navigation (A12)<br>Test set bus (A13)<br>Dual bus processor (A14)<br>Programmable static random-access<br>memory (A15) |

|                                                           | - ( )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# 1-8. SAFETY, CARE, AND HANDLING

- <u>a</u>. <u>Safety</u>. For artificial respiration, refer to FM -21-11. When lifting or handling heavy objects, use two persons to prevent possible back injury.

- b. Care. Do not use the equipment as a step or a seat.

- c. <u>Handling</u>. Do not drop the equipment or turn it over roughly. Avoid damage to connectors.

### SECTION II. EQUIPMENT DESCRIPTION

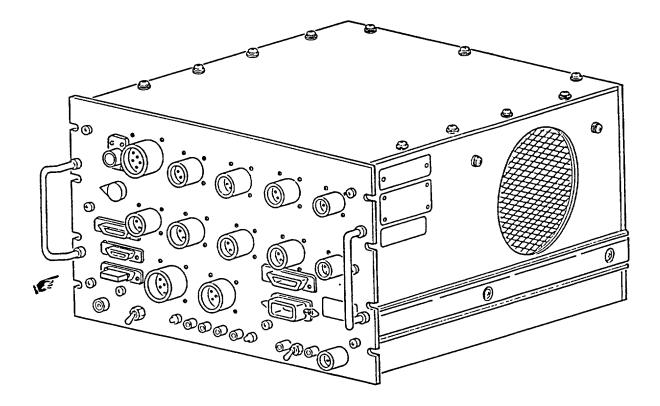

## 1-9. CHARACTERISTICS, CAPABILITIES, FEATURES

#### CHARACTERISTICS

- MODULAR CONSTRUCTION

- OPERATES ON STANDARD AC LINE VOLTAGE

- DESIGNED FOR RACK OR BENCH MOUNTING

## CAPABILITIES

- SIMULATES ANALOG IF PROCESSOR (IFP) OUTPUT SIGNALS TO TEST INTERFACE UNIT (IU)

- SIMULATES THE FOLLOWING DIGITAL OUTPUTS:

- IU DATA TO TEST COMPUTER PROCESSOR (CP)

- FREQUENCY SYNTHESIZER (FS) AND RADIO FREQUENCY ANTENNA (RFA) DATA TO TEST RECEIVER DIGITAL CONTROL (RDC)

- CP, NAV SET, AND WIDE BAND DATA LINK DATA TO TEST IU

### FEATURES

- REQUIRES OPERATOR INTERFACE DEVICE (OPERATOR TERMINAL)

- FRONT PANEL INTERFACE FOR OPERATOR TERMINAL OR OTHER PERIPHERAL DEVICES

- COMPLETE, SELECTABLE, INTERNALLY STORED TEST PROGRAMS FOR IU, CP, AND RDC

- DIAGNOSTIC PROGRAM LOAD SELECTION VIA SINGLE FRONT PANEL SWITCH

- BUILT-IN COOLING FAN

- COMPLETE TEST CABLE SET

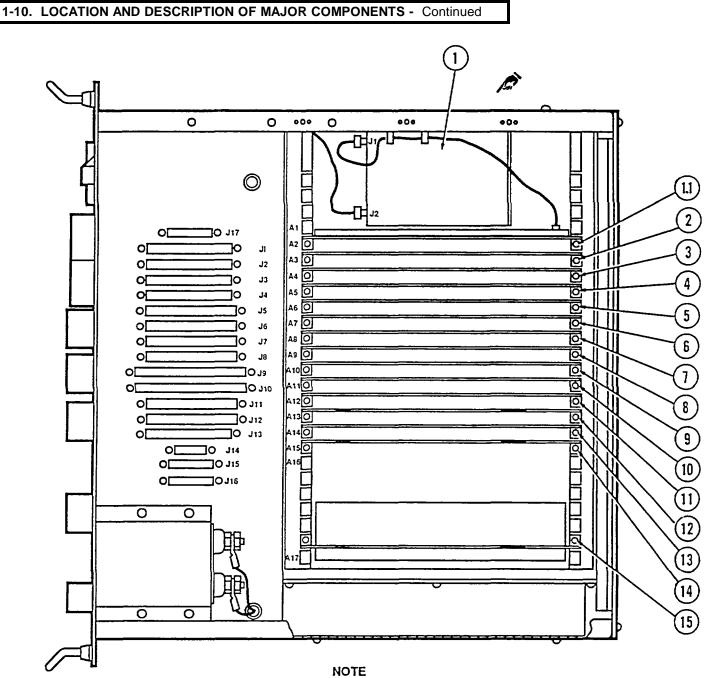

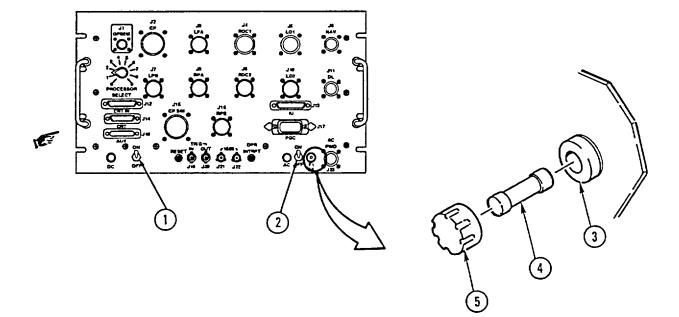

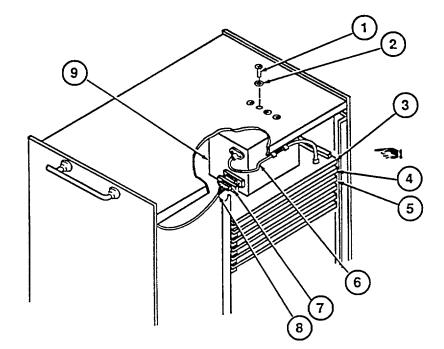

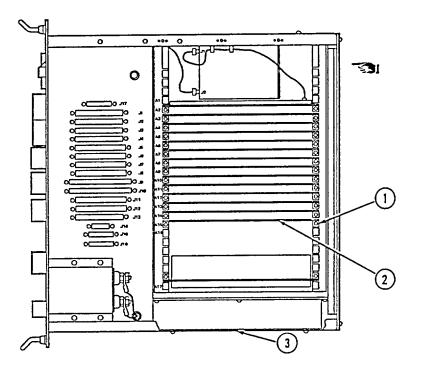

### 1-10. LOCATION AND DESCRIPTION OF MAJOR COMPONENTS

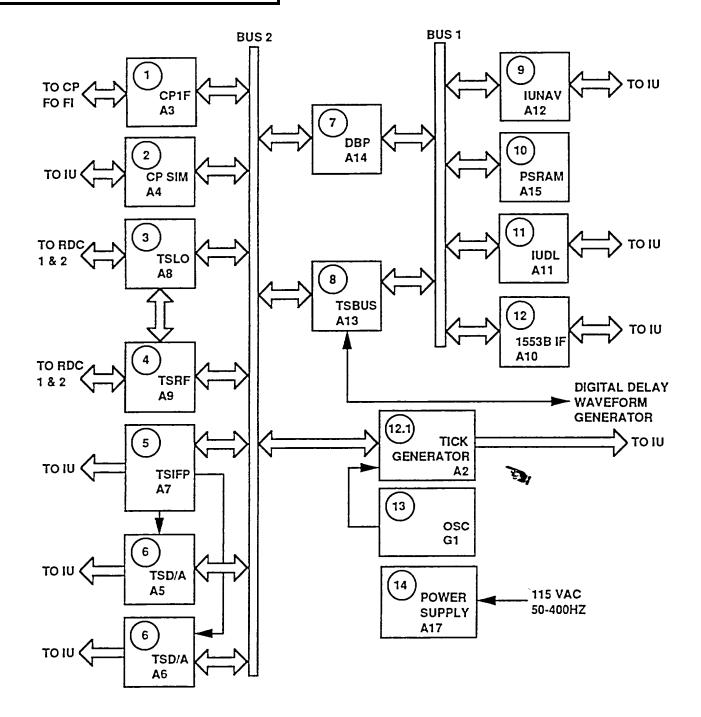

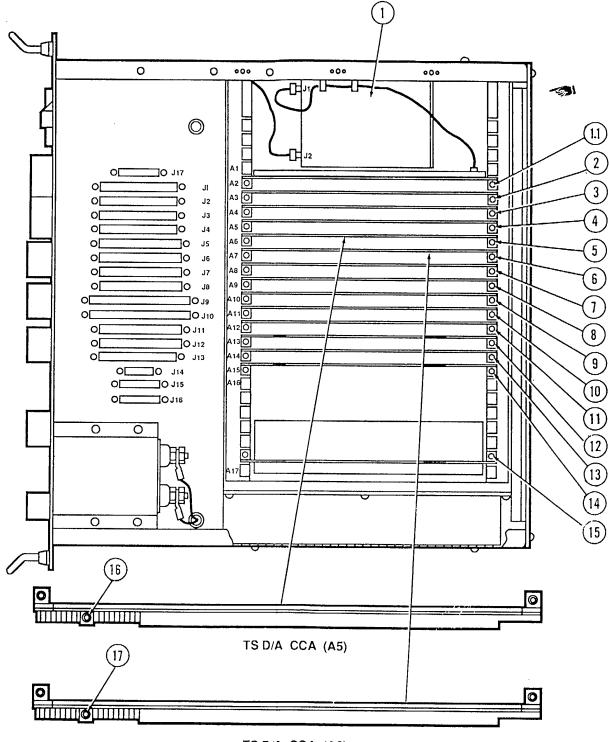

- (1) OSCILLATOR (61).

- (1.1) TICK GENERATOR (A2).

- (2) COMPUTER PROCESSOR INTERFACE (CPIF) (A3).

- (3) COMPUTER PROCESSOR SIMULATOR (CP SIM) (A4).

- (4) TEST SET DIGITAL/ANALOG (TSD/A) (A5).

- (5) TEST SET DIGITAL/ANALOG (TSD/A) (A6).

- (6) TEST SET IF PROCESSOR (TSIFP) (A7).

- (7) TEST SET LOCAL OSCILLATOR (TSLO) (A8).

- (8) TEST SET RADIO FREQUENCY (TSRF) (A9).

- (9) 1553B INTERFACE (1553B IF) (A10).

- (10) INTERFACE UNIT DATA LINK (IUDL) (AII).

- (11) INTERFACE UNIT NAVIGATION (IUNAV) (A12).

- (12) TEST SET BUS (TSBUS) (A13).

- (13) DUAL BUS PROCESSOR (DBP) (A14).

- (14) PROGRAMMABLE STATIC RANDOM-ACCESS MEMORY (PSRAM) (A15).

- (15) POWER SUPPLY (A17).

High accuracy clock

Simulates global positioning satellite (GPS) time tick

Simulates data from IU

Simulates CP outputs

Simulates IFP outputs

Simulates IFP outputs

Simulates IFP and trigger outputs

Simulates FS outputs

Simulates RFA outputs

Supports 1553B bus operation

Provides high-speed serial channel and self test loop-back

Simulates navigation data

Provides GPIB. Provides spare RS-232C channels, interrupts, and timers

8086 microprocessor which controls functions and testing of LRUs

Stores operating and diagnostic programs

Supplies and distributes power

(CCA SLOTS A1, A16 NOT USED)

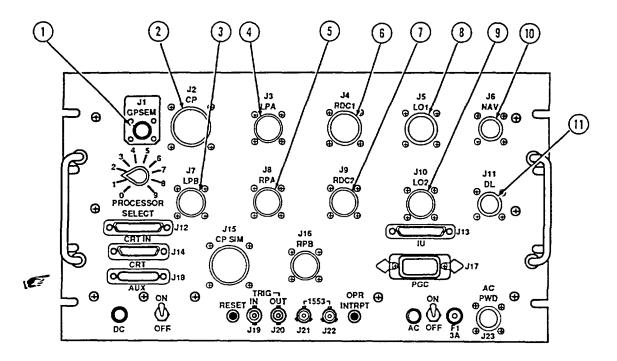

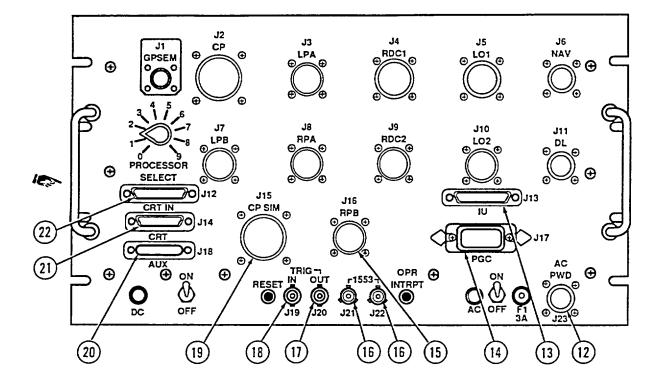

## 1-10. LOCATION AND DESCRIPTION OF MAJOR COMPONENTS - Continued

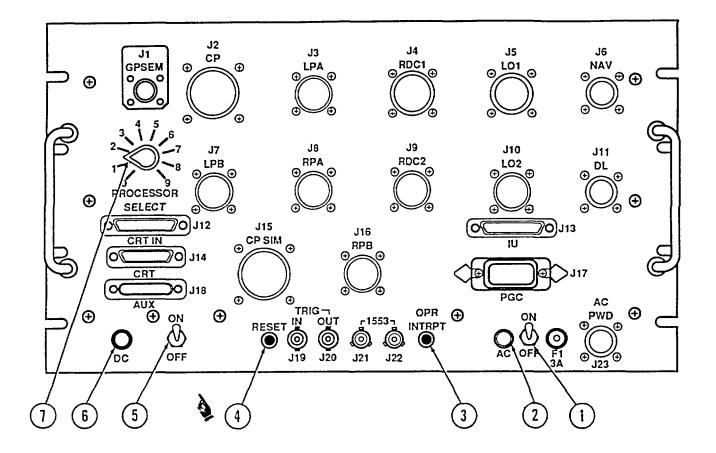

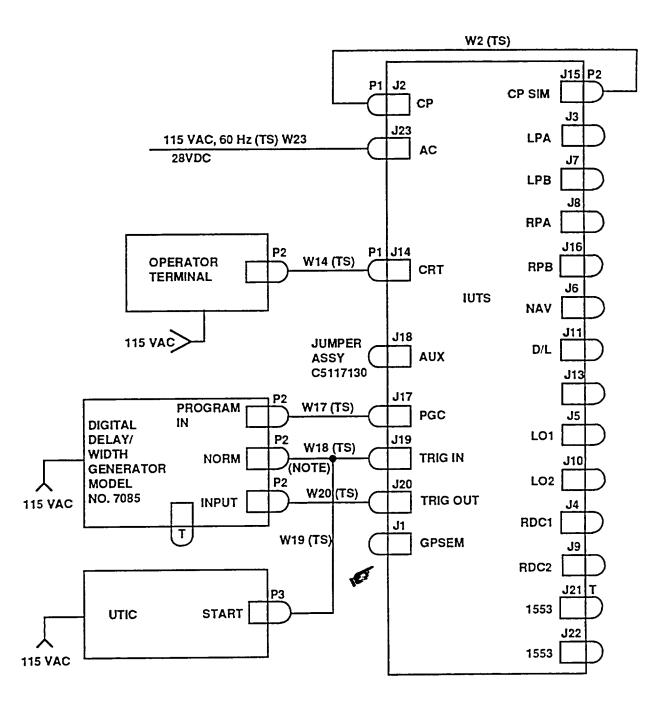

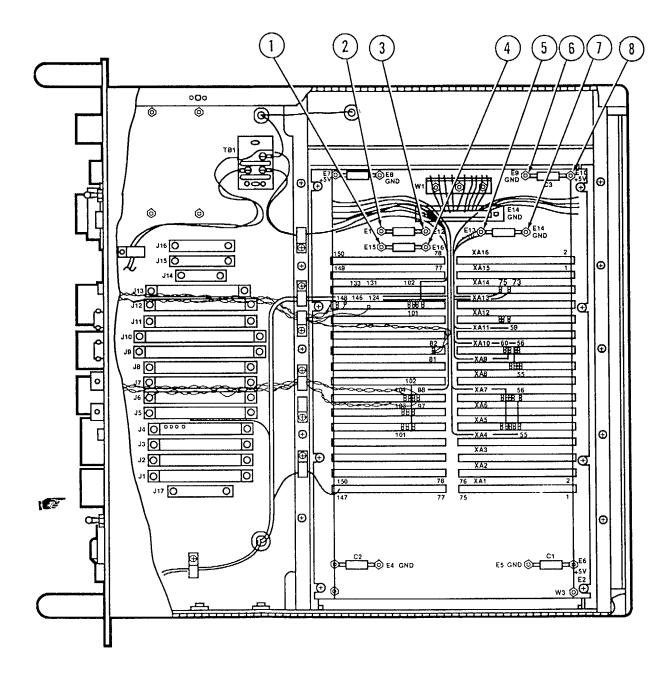

#### b. External Interfaces.

- (1) GPSEM (J1)

- (2) CP (J2).

- (3) LPB (J7).

- (4) LPA (J3).

- (5) RPA (J8).

- (6) RDC1 (J4).

- (7) RDC2 (J9).

- (8) L01 (J5).

- (9) L02 (J10).

- (10) NAY (06).

- (11) DL (J11).

GPS output to test IU

Data bus output to CP

Outputs simulated left pod quadrant B signals

Outputs simulated left pod quadrant A signals

Outputs simulated right pod quadrant A signals

Outputs simulated data signals to RDC1

Outputs simulated data signals to RDC2

Outputs simulated FS No. 1 signals

Outputs simulated FS No. 2 signals

Outputs simulated navigation signals

Outputs simulated data link outputs

## 1-10. LOCATION AND DESCRIPTION OF MAJOR COMPONENTS - Continued

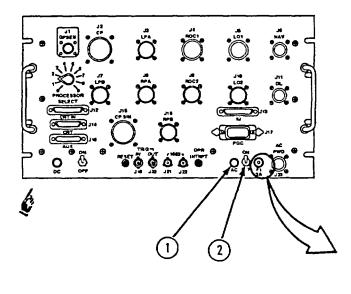

- (12) AC PWR (J23).

- (13) IU (J13).

- (14) PGC (J17).

- (15) RPB (J16).

- (16) 1553B (J21/J22).

- (17) TRIG OUT (J20).

- (18) TRIG IN (J19).

- (19) CP SIM (J15).

- (20) AUX (J18).

- (21) CRT (J14).

- (22) CRT IN (J12).

AC power input

I/O port to IU

Outputs control data to digital delay width generator

Outputs simulated right pod quadrant B signals

1553B bus ports

Trigger output to digital delay width generator

Trigger input from digital delay width generator

Outputs simulated CP data

I/O port to disk drive

Outputs data to CRT

I/O port to CP

# 1-11. EQUIPMENT DATA

| <u>a</u> . | Physical                    |                                                                          |

|------------|-----------------------------|--------------------------------------------------------------------------|

|            | Weight                      | 45.00 lb (20.41 kg)                                                      |

|            | Height                      | 10.50 in (26.67 cm)                                                      |

|            | Width                       | 19.00 in (48.26 cm)                                                      |

|            | Length                      | 17.00 in (43.18 cm)                                                      |

| <u>b</u> . | Functional                  |                                                                          |

|            | Input Power                 | 115 Vac @ 2.0 amp<br>+ 28 Vdc @ 4.0 amp                                  |

|            | Interface<br>External       | Interface unit<br>Computer processor<br>Receiver digital control         |

|            | Internal<br>Input<br>Output | BUS1 and BUS2<br>Control signals and data<br>Simulation signals and data |

| <u>c</u> . | Environmental               |                                                                          |

|            | Temperature<br>Operating    | + 32 degrees F ( 0 degrees C) to<br>-109 degrees F (+43 degrees C)       |

|            | Non-operating               | - 61 degrees F (-51 degrees C) to<br>+154 degrees F (+68 degrees C)      |

|            | Altitude<br>Operating       | 10,000 ft ( 3,048 m)                                                     |

|            | Non-operating               | 40,000 ft (12,192 m)                                                     |

|            | Humidity                    | 0 to 98 percent                                                          |

|            | Fungus                      | Fungus resistant                                                         |

|            | Salt fog                    | Prolonged exposure without degradation                                   |

|            | Sand and Dust               | Exposure without damage or degradation                                   |

|            | Vibration                   | Transportable by ground vehicle, watercraft, or aircraft                 |

|            | Rain                        |                                                                          |

|            | Operating                   | No damage or degradation                                                 |

## Section III. TECHNICAL PRINCIPLES OF OPERATION

## 1-12. OVERVIEW

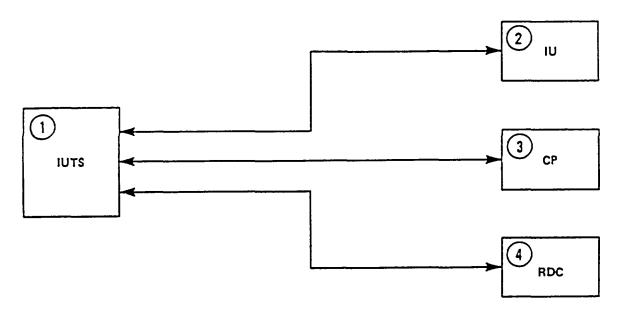

- (1) INTERFACE UNIT TEST SET (IUTS). Provides digital/analog (D/A) interfaces, and IFP control functions for testing IFP interfaces in IU. Also provides test interfaces for FIFO memory in CP, LO status, and ROM data to RDC.

- (2) **INTERFACE UNIT (IU).** Receives and converts analog signals to digital signals from IFP. Transfers pulse data to CP.

- (3) **COMPUTER PROCESSOR (CP).** Receives pulse data from IU and processes data to be sent back to IU.

- (4) **RECEIVER, DIGITAL, CONTROL (RDC).** Receives commands from IU. Distributes commands to IFS, IFP, and RFA. Transmits ROM data and lock status to IU.

### 1-13. DETAILED OPERATION

- (1) COMPUTER PROCESSOR INTERFACE (CPIF) (A3). Tests FIFO memory in CP.

- (2) COMPUTER PROCESSOR SIMULATOR (CP SIM) (A4). Simulates FIFO memory function for testing CP interface in IU.

- (3) TEST SET LOCAL OSCILLATOR (TSLO) (AS). Receives FS BCD frequency-tuned data words, L01 and L02, from RDC 1 and RDC 2. Converts differential input data and sends it to DBP (A14). Sends simulated FS lock status signals (LK1 and LK2) to RDC 1 and RDC 2.

- (4) TEST SET RADIO FREQUENCY (TSRF) (A9). Simulates outputs from RFA to RDC 1 and RDC 2.

- (5) TEST SET IF PROCESSOR (TSIFP) (A7). Generates control signals for testing IFP interface in IU.

- (6) TEST SET DIGITAL/ANALOG (TSD/A) (A5) (A6). Simulates analog signals for testing IFP interface in IU.

- (7) DUAL-BUS PROCESSOR (DBP) (A14). Controls data handling on bus 1 and bus 2, memory control, and testing.

- (8)\_ TEST SET BUS (TSBUS) (A13). Generates interrupts, control, and timing signals. Provides an IEEE-STD-488 GPIB to communicate with an external digital delay waveform generator (DDWG). Provides two spare RS-232C channels.

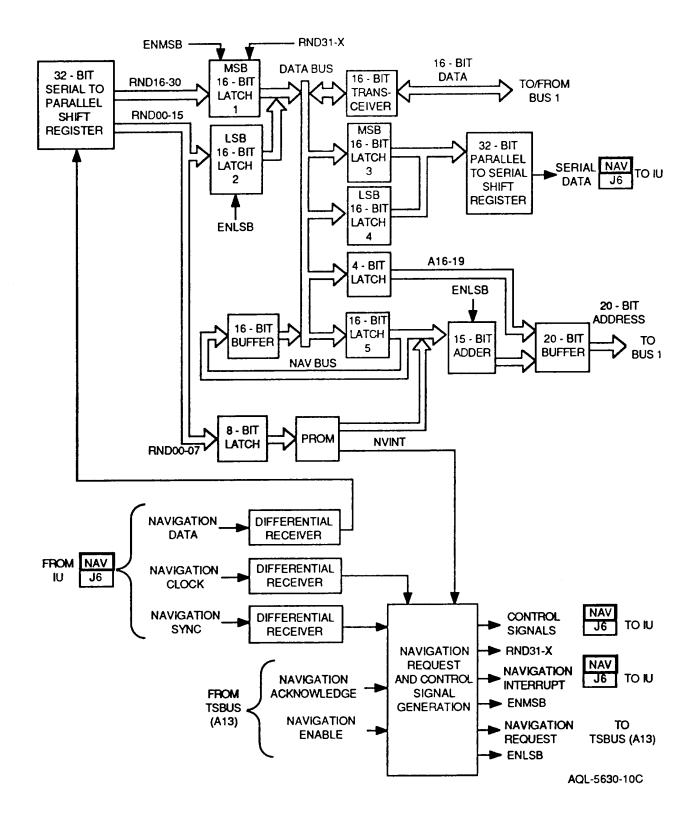

- (9) INTERFACE UNIT NAVIGATION (IUNAV) (A12). Generates simulated signals to test IUNAV board in IU.

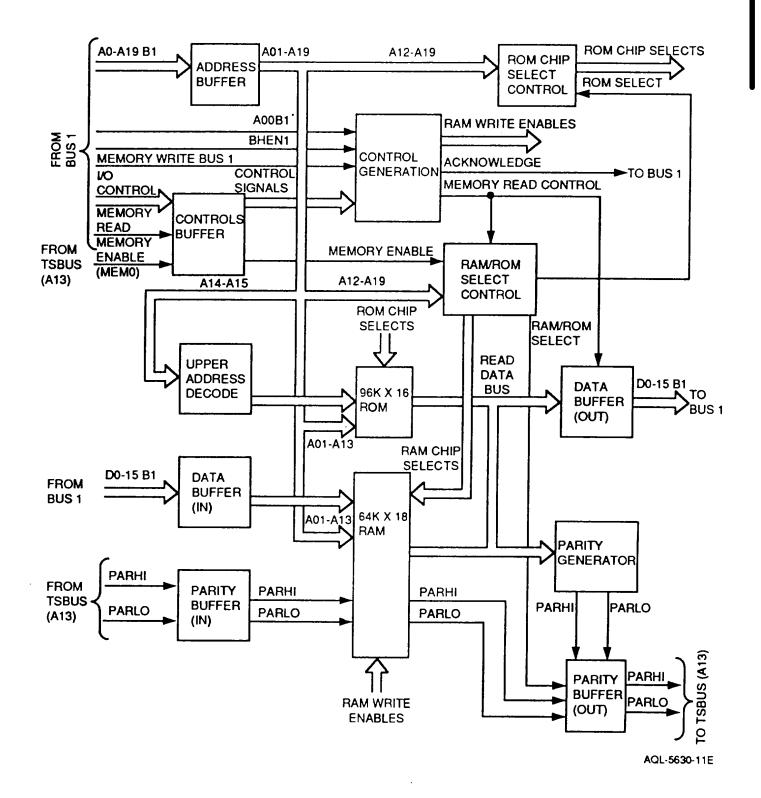

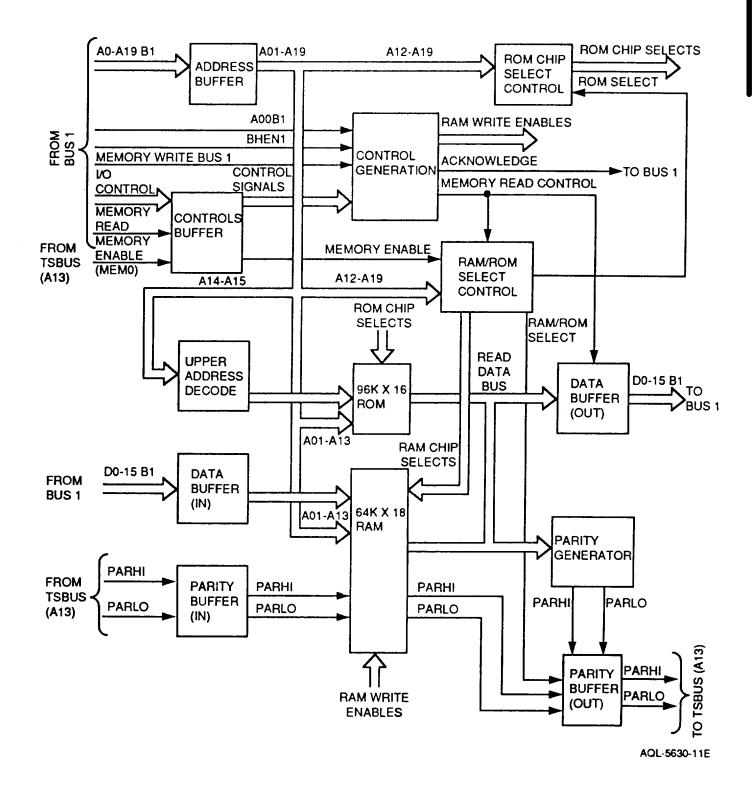

- (10) PROGRAMMABLE STATIC RANDOM ACCESS MEMORY (PSRAM) (A15). Stores operating and diagnostic programs in ROM and stores selected programs and data in RAM.

- (11) INTERFACE UNIT DATA LINK (IUDL) (All). Provides a high-speed serial data communications channel to test IU data link interface. Performs self-test using loop-back.

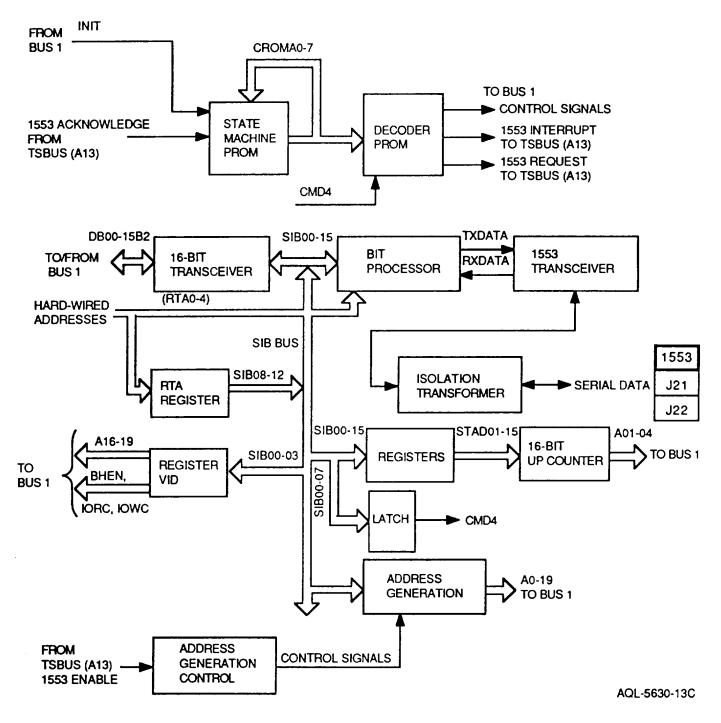

- (12) 1553B INTERFACE (A10). 1553B interface (A10) is a high-speed bi-directional transceiver with self-test capability. 1553B interface supports serial communications with IU via MIL-STD-1553 data bus.

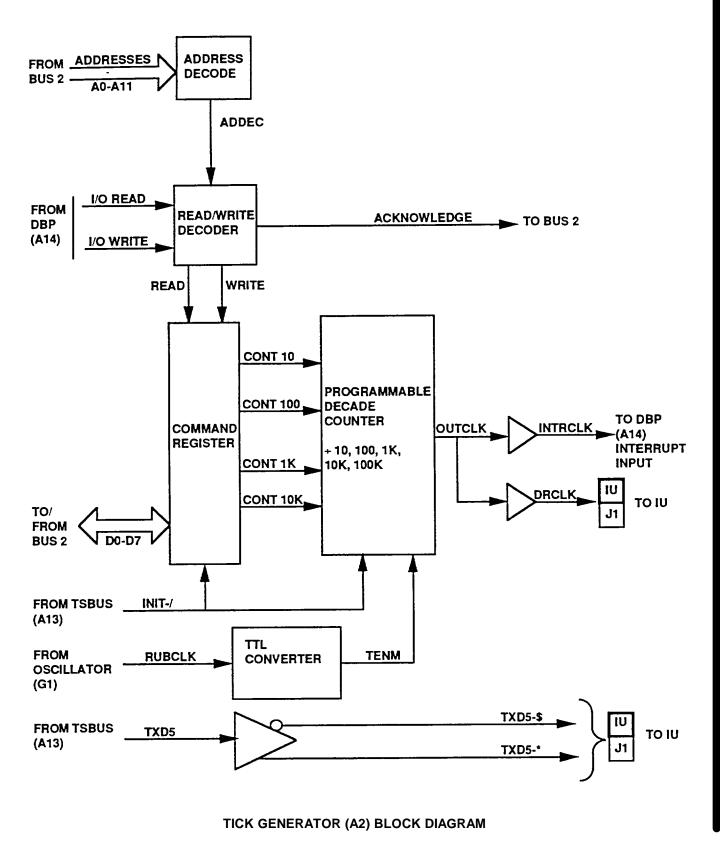

- (12.1) TICK GENERATOR (A2). Simulates GPS time tick and transmits GPS data to test IU.

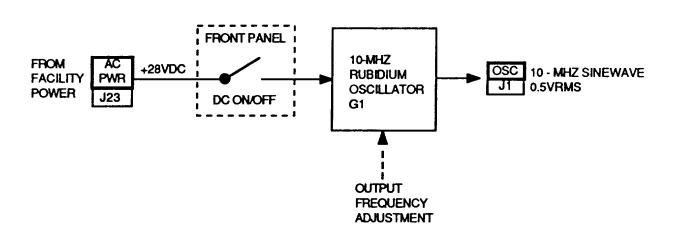

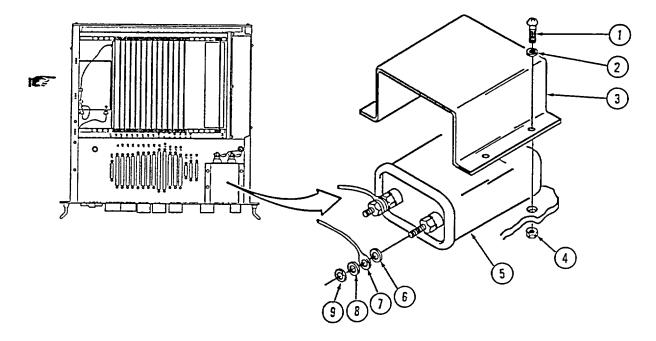

- (13) OSCILLATOR (GI). Rubidium oscillator generates a high-accuracy 10 MHz signal.

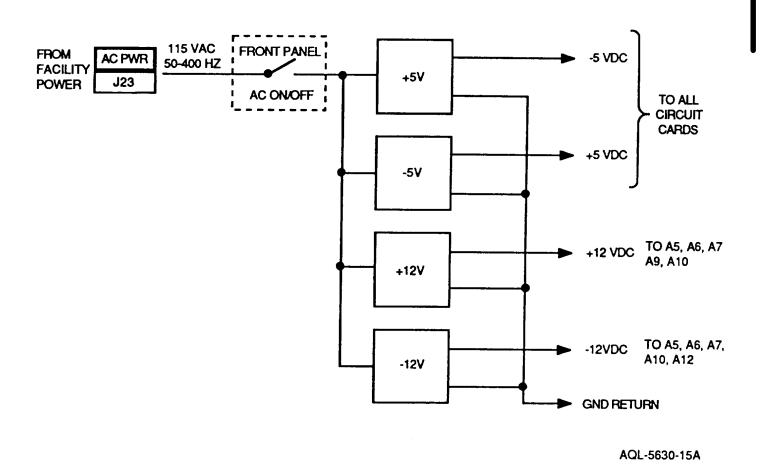

- (14) POWER SUPPLY (A17). Converts +115 Vac to four output voltages (+ 5 Vdc, 5 Vdc, +12 Vdc, and -12 Vdc) for operation of IUTS.

- <u>a</u>. <u>Overview</u>. Refer to the IUTS functional block diagram. IUTS is special test equipment and forms part of AQL maintenance subsystem. Purpose of IUTS is to test the IU interfaces and the CP FIFO memory in the AQL system. IUTS produces pre-programmed test patterns for each interface being tested. IU interfaces are:

- IFP

- CPIF

- RDC

- 1553B interface

- Data link communication system

- Navigation system

1-12 Change 1

**IUTS FUNCTIONAL BLOCK DIAGRAM**

Change 1 1-12.1

<u>a. 1</u>. <u>Tick Generator (A2)</u>. Refer to the tick generator (A2) block diagram. Tick generator (A2) provides simulated GPS data and time tick signals to the IU under test. These signals are under IUTS software control.

Tick generator (A2) receives:

- Address data (AO-A11) from bus 2

- VO read and write from DBP (A14)

- Data (D0-D7) from bus 2

- System RESET signal INIT-/ from TSBUS (A13)

- RUBCLK from oscillator (G1)

- Serial GPS data signal TXD5 from TSBUS (A13)

Tick generator (A2) outputs:

- Acknowledge to bus 2

- INTRCLK to DBP (A 14) interrupt input

- DRCLK to IU

- TXD5-\$ and TXD5-\* to IU

- (1) Address lines AO-A11 are decoded to produce ADDEC. The read/write decoder uses ADDEC and the I/VO read and write signals from DBP (A14) to generate the acknowledge signal to bus 2, acknowledging the read or write. The read/write decoder also generates a read and a write strobe for the command register.

- (2) An I/O write command writes data from data bits DO-D7 into the command register. The data becomes CONT 10, CONT 100, CONT 1K, and CONT 10K, which programs the programmable decade counter. An /00 read command allows the data in the command register to be read back onto the data bus. INIT-/ is the power on reset from TSBUS (A 13) and clears the command register.

- (3) The 10 MHz sinewave output of oscillator (GI) (RUBCLK) is converted to transistor-transistor logic (TTL) signal TENM and input to the programmable decade counter where it is divided by 10, 100, 1K, 10K, or 100K to generate OUTCLK. The division is controlled by the status of CONT 10, CONT 100, CONT 1K, and CONT 10K inputs to the programmable decade counter. INIT-/ is the power on reset from TSBUS (A 13) and clears the programmable decade counter.

- (4) The OUTCLK output of the programmable decade counter is split into two signals and buffered to produce INTRCLK and DRCLK. DRCLK is sent to the IU for test purposes. INTRCLK is the GPS interrupt input to DBP CCA A14.

- (5) Simulated navigation data (TXD5) from a serial communications controller on TSBUS (A13) is converted into a differential signal (TXD5-S and TXD5-\*) and output to the IU for test purposes.

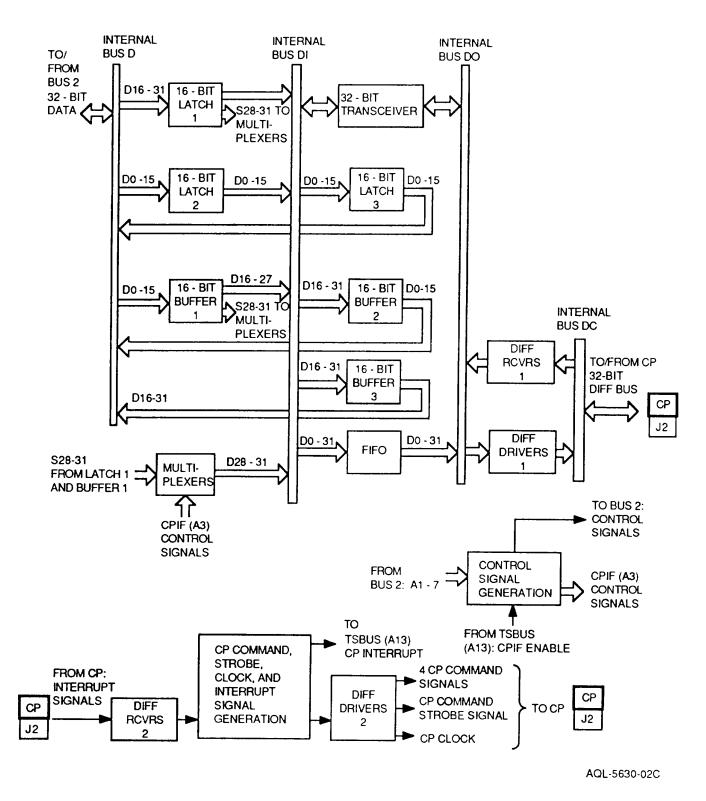

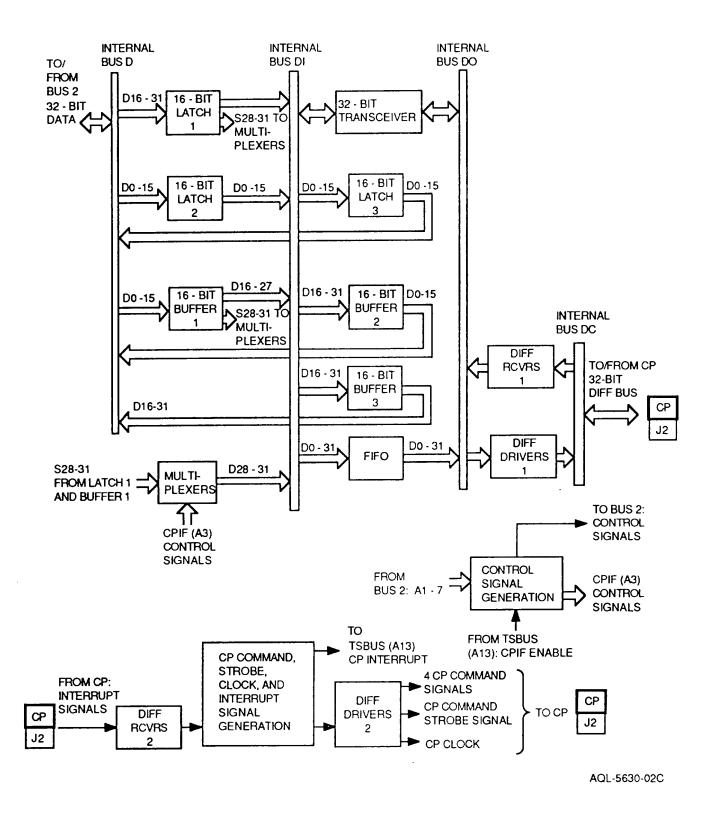

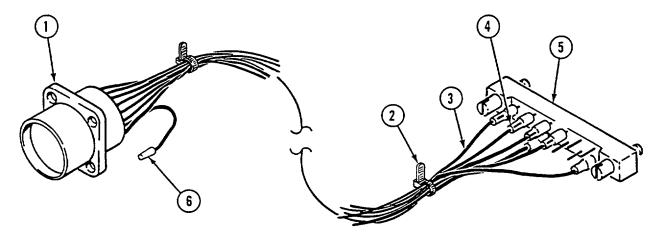

b. <u>CPIF (A3)</u>. Refer to the CPIF (A3) block diagram. CPIF (A3) controls differential pulse data transfer between IU and CP.

CPIF (A11) receives:

- 32-BIT DATA from bus 2

- INTERRUPT SIGNALS from CP

- Address data (A1-7) from bus 2

- CPIF ENABLE from TSBUS (A13)

CPIF (A3) outputs:

- 32-BIT DATA to bus 2

- CONTROL SIGNALS to bus 2 and CPIF (A3)

- CP INTERRUP T to TSBUS (A13)

- 4 CP COMMAND SIGNALS, CP COMMAND STROBE SIGNAL, AND CP CLOCK to the CP

- 32-BIT DATA (D0-31) on DIFF BUS to the CP

- (1) 32-BIT DATA (called beginning of look header) (BOL) from bus 2 is applied to internal bus D. All of the control signals and enables to route the data through CPIF (A3) are generated within CPIF (A3) itself. Output from the 16-bit latches is enabled on internal bus DI. Data on bus DI are enabled to the 32-bit transceiver. The transceiver puts 32-bit data on internal bus DO and into differential drivers. The differential drivers send the 32bit data (DIFF BUS) to the CP via internal bus DC which connects to the 32-bit differential bus.

- (2) Additional 32-bit data called intercept word (IW) may follow the BOL but require holding to allow frequency retrigger (FRT) signals to be sent to the CP first. IW is then enabled from bus DI into FIFO. When CP is ready for 1W, 32-bit data (TW) is put onto DO bus by FIFO and sent by differential drivers to CP the same as BOL.

- (3) When 32-bit data (FRT) is sent to the CP, it is transmitted the same as BOL. End of look header (EOL) follows to complete data transfer.

- (4) Data bits 28-31 of 32-bit data word going to CP are address information and are enabled out of 16-bit latch number 1 and buffer number 1 directly to multiplexers. CPIF control signals and data bits 28-31 control flow of 32-bit data through CPIF (A3).

- (5) CP status is sent to CPIF (A3) as 32-bit status word. Status word is sent via the 32-bit differential bus and CPIF internal bus DC to differential receivers number 1. At specific times, data bits DO-15 from bus D are also enabled into 16-bit buffer number 1. The data controls transfer of CP status word as in paragraph (4). The status word out of differential receivers number 1 is put on bus DO and enabled through the 32-bit transceiver to bus DI. From bus DI, data bits DO-15 are enabled through the 16-bit latch number 3 to bus D and the digitizer bus. Data bits DO-15 from the digitizer bus are sent to DBP (A14). From bus DI, data bits D 16-31 are enabled through buffer number 3 to bus D and the digitizer bus. The digitizer bus is connected directly to bus 2 through TSBUS (A13). Status word is destined for DBP (A14) which can only receive 16-bit words. Data bits D16-31 were enabled into the 16-bit buffer number 2 and held. Now data bits D16-31 are enabled out of the 16-bit buffer as D0-15 onto bus D and follow the same route as the first 16-bits to DBP (A14).

- (6) CPIF (A3) receives address bits A1-7 via bus 2 and CPIF ENABLE from TSBUS (A13). These signals are applied to the control signal generation circuits. CONTROL SIGNALS are used in CPIF (A3) and bus 2.

CPIF (A3) BLOCK DIAGRAM

- (7) INTERRUPT SIGNALS from the CP are applied to differential receivers number 2. The differential receiver outputs are applied to CP command, strobe, and interrupt signal generation circuit which generates the following outputs and transmits them to the computer processor through differential drivers number 2.

- CP INTERRUPT to TSBUS1 (A13)

- CP COMMAND SIGNALS to the CP

- CP COMMAND STROBE SIGNAL to the CP

- CP CLOCK to the CP

CPIF (A3) BLOCK DIAGRAM

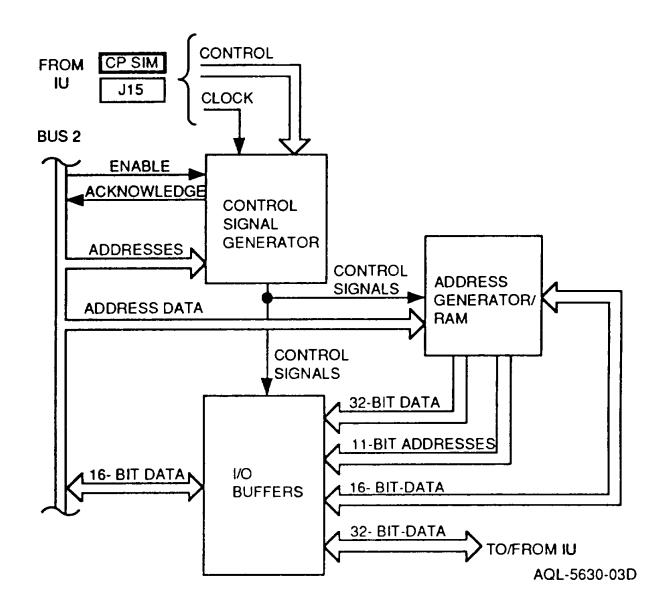

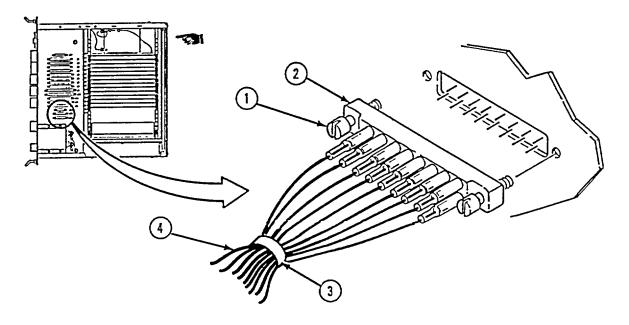

c. <u>CP SIM (A4)</u>. Refer to the CP SIM (A4) block diagram. CP SIM (A4) simulates interface between IU and CP FIFO memory. Interface simulation is accomplished by transferring 32-bit data in and out of a 32-bit wide RAM.

The CP SIM (A4) accepts:

- 32-bit differential data from the IU

- 16-bit data from DBP (A14) via bus 2

- Address lines from DBP (A14) via bus 2

- Control signals and clock signals from the IU

The CP SIM (A4) outputs:

- 32-bit differential data to the IU

- 16-bit data to bus 2

- Control signal response to DBP (A14), TSBUS (A13) via bus 2, and IU

- (1) Using control signals from the control signal generator and address lines from bus 2, the address generator produces addresses for the on-board RAM. Refer to the address generator/RAM section for further information.

- (2) Using differential data and control signals from the IU, the control signal generator produces reply signals to the DBP (A14), and control signals to the address generator/RAM, and the UO buffers. Refer to the control signal generator section for further information.

- (3) Using control signals from the control signal generator, data and addresses from the address generator/RAM and DBP (A14), the IO buffers input and output 16-bit parallel data to and from the DBP (A14) and inputs and outputs 32-bit differential data to and from the IU. Refer to the I/O buffers section for further information.

CP SIM (A4) BLOCK DIAGRAM

1-19

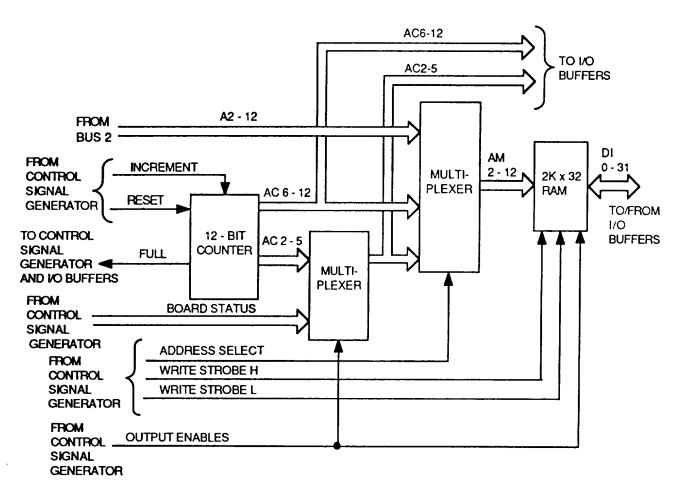

<u>d.</u> <u>Address Generator/RAM</u>. Refer to the CP SIM (A4) address generator block diagram. The address generator section of this card produces addresses for storage in RAM.

The address generator/RAM accepts:

- 11-bit address lines A2-12 from bus 2

- ADDRESS SELECT, WRITE STROBE H, and WRITE STROBE L from the control signal generator

- INCREMENT and RESET from the control signal generator

- OUTPUT ENABLES and BOARD STATUS from the control signal generator

- 32-bit RAM data DI0-31 from the I/O buffers

The address generator/RAM outputs:

- 32-bit RAM data DI0-31 to the I/O buffers

- 1-bit counter full signal to the control signal generator

- 11-bit address lines AC2-12 to the I/O buffers

- (1) Using the INCREMENT input, the 12-bit counter generates address signals AC2-5 and AC6-12, and a 1-bit counter full signal.

- (2) Using the board status lines, 4 bits of address lines from the 12-bit counter (AC2-5), and OUTPUT ENABLES, address lines to the second multiplexer (AM2-5), are selected.

- (3) Using the 11 address lines (A2-12) or the address lines AC6-12, AC2-5, and ADDRESS SELECT, the memory address lines AM2-12 are selected by the second multiplexer.

- (4) The 2K x 32 RAM simulates CP FIFO memory. Address signals AM2-12 from the second multiplexer are written into RAM upon receipt of a write signal. RAM data DI0-31 is output from RAM upon receipt of WRITE STROBE H, WRITE STROBE L, and OUTPUT ENABLES.

AQL-5630-23D

CP SIM (A4) ADDRESS GENERATOR/RAM BLOCK DIAGRAM

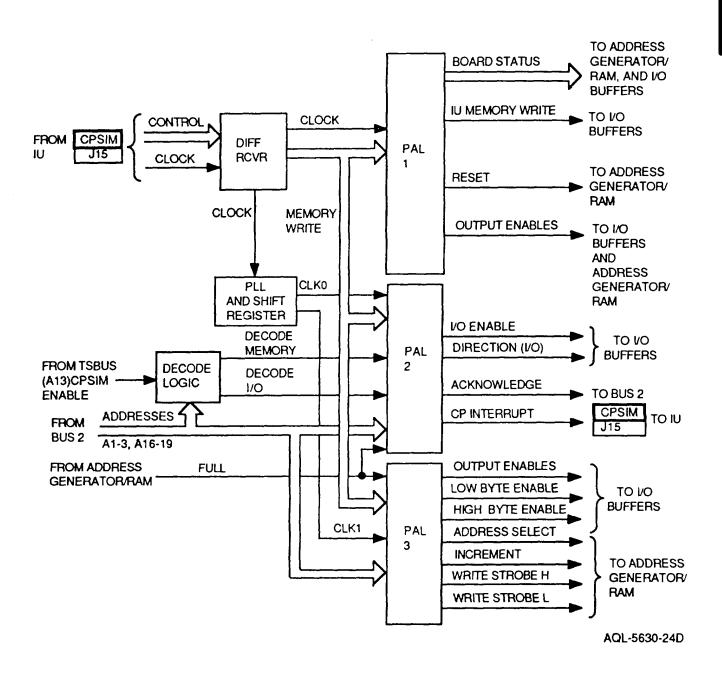

e. <u>Control Signal Generator</u>. Refer to the CP SIM (A4) control signal generator block diagram. The control signal generator section produces reply signals to the DBP (A14), and control signals to the address generator/RAM and the I/O buffers.

The control signal generator accepts:

- 4-bit address (A16-19) from bus 2

- 3-bit address (A01-03) from bus 2

- CLOCK and CONTROL from the IU

- FULL from the address generator/RAM

- CPSIM ENABLE from TSBUS (A13)

The control signal generator outputs:

- IU MEMORY WRITE to I/O buffers

- I/O ENABLE to the 1/O buffers

- DIRECTION (I/O) to the I/O buffers

- ACKNOWLEDGE to bus 2

- CP INTERRUPT to the IU via the differential bus

- RESET to the address generator/RAM

- OUTPUT ENABLES to the I/O buffers and address generator/RAM

- LOW BYTE ENABLE to the IO buffers

- HIGH BYTE ENABLE to the IO buffers

- ADDRESS SELECT to the address generator/RAM

- INCREMENT to the address generator/RAM

- WRITE STROBE H (high) to the address generator/RAM

- WRITE STROBE L (low) to the address generator/RAM

- BOARD STATUS to the address generator/RAM and I/O buffers

- (1) CLOCK is applied to the phase-lock loop (PLL) and shift register via the differential receiver. The PLL generates CLKO and CLK1 for PALS 2 and 3.

- (2) When CPSIM ENABLE is applied, the decode logic decodes the upper four address lines (A16-19) and generates DECODE MEMORY to PAL 2. Using the lower three address lines (A01-03), the decode logic outputs DECODE IO to PAL 2. The differential receiver generates MEMORY WRITE from CONTROL. The combination of CLOCK, MEMORY WRITE, DECODE MEMORY, FULL, AND DECODE I/O causes PAL 2 and PAL 3 to output the various signals used throughout the CP SIM and the IUTS.

- (3) Using MEMORY WRITE and CLOCK, PAL 1 produces the various signals used by other CP SIM sections.

CP SIM (A4) CONTROL SIGNAL GENERATOR BLOCK DIAGRAM

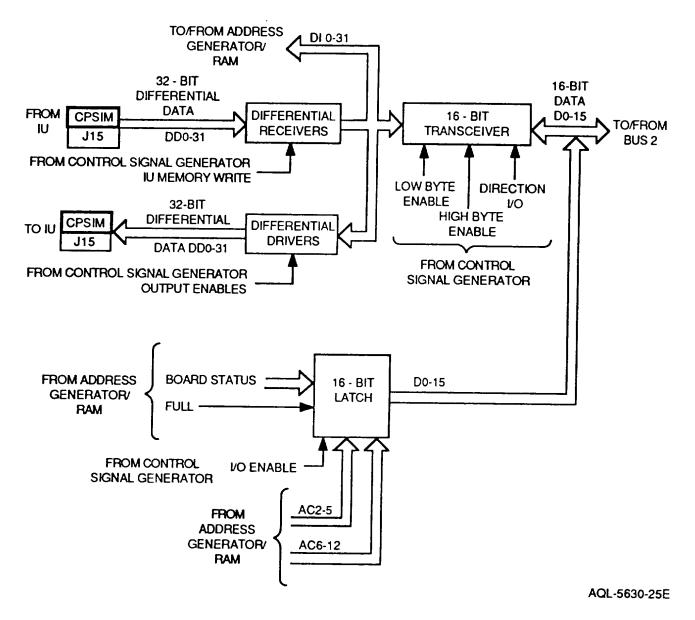

f. <u>I/O Buffers</u>. Refer to the CP SIM (A4) I/O buffers block diagram. The UO buffers section inputs and outputs 16bit parallel data to and from the DBP (A14), and inputs and outputs 32-bit differential data to and from the IU.

The I/O buffers accept:

- 11-bit addresses (AC2-12) from the address generator/RAM

- 32-bit data (DDO-31) from the IU

- LOW BYTE ENABLE, HIGH BYTE ENABLE, and DIRECTION UO from the control signal generator

- 16-bit data (DO-15) from bus 2

- DI0-13 from address generator/RAM

- Counter full status (FULL) from the address generator/RAM

- I/O ENABLE from the control signal generator

- IU MEMORY WRITE from the control signal generator

- BOARD STATUS from the address generator/RAM

- OUTPUT ENABLES from the control signal generator

The I/O buffers output:

- DIO-13 to address generator/RAM

- 32-bit data (DDO-31) to the IU

- 16-bit data (DO-15) to bus 2

- (1) The differential receivers and differential drivers are used to transfer data to and from the RAM to the IU using IU MEMORY WRITE and OUTPUT ENABLES.

- (2) The 16-bit transceiver transfers 16-bit data to and from bus 2 using DIRECTION I/O, LOW BYTE ENABLE, and HIGH BYTE ENABLE. The 16-bit latch holds the counter address and full status and board status, which may be enabled onto bus 2 using I/O ENABLE.

CP SIM (A4) I/O BUFFERS BLOCK DIAGRAM

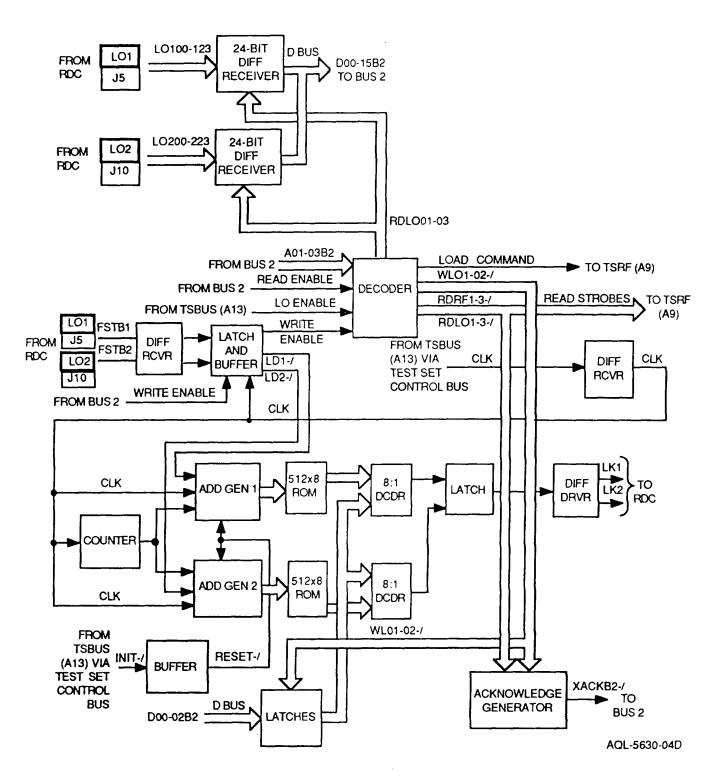

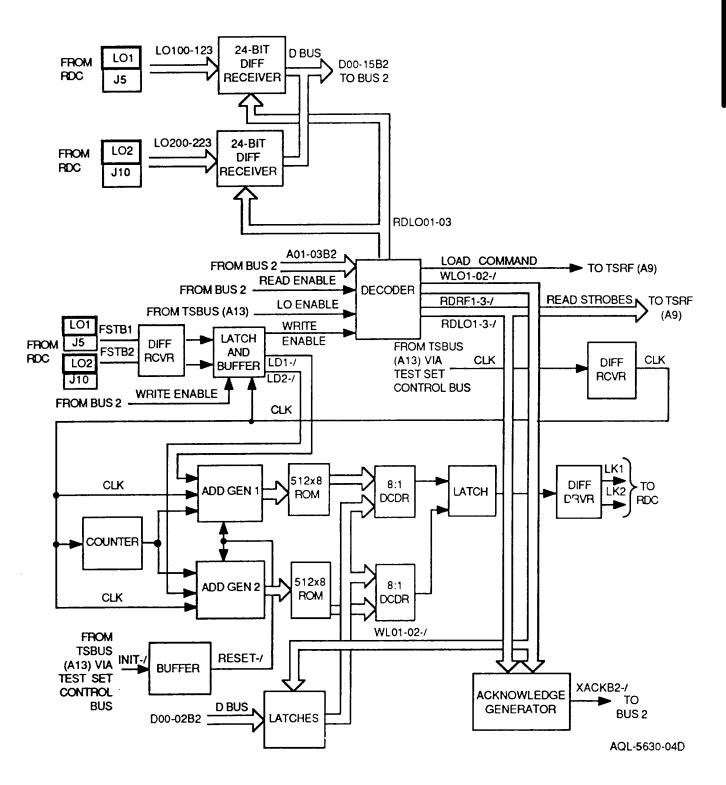

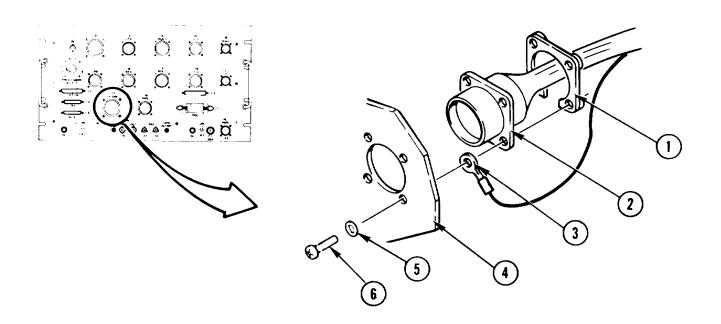

g. <u>TSLO (A8)</u>. Refer to the TSLO (AS) block diagram. The software-controlled TSLO (A8) tests the IU/FS/RFA/RDC interface by receiving FS BCD frequency-tuned data words, L01 and LO2, from the RDC and transmitting FS lock-status signals (LK1 and LK2) to the RDC via a differential bus. TSLO (AS) also sends control signals to TSRF (A9).

TSLO (As) accepts:

- BCD frequency-tuned FS data words, L01 and L02, as 48 differential signals (L0100-123 and L0200-223) from the RDC

- Frequency strobes (FSTB1, FSTB2) as two differential signals from RDC

- Three address lines (A01-03B2) from bus 2

- INIT4 from TSBUS (A13) via test set control bus

- ICLK from TSBUS (A13) via test set control bus

- LO ENABLE from TSBUS (A13)

- WRITE ENABLE and READ ENABLE from bus 2

TSLO (As) outputs:

- LOAD COMMAND to TSRF (A9)

- 16-bit data (D00-15B2) to bus 2

- Acknowledge signal (XACKB2-/) to bus 2

- FS lock-status signals (LK1, LK2) as two differential signals to RDC

- READ STROBES to TSRF (A9)

- (1) TSLO input and output data and signals:

- An input clock signal (CLK) from TSBUS (A13) is received by a differential receiver and the output signal CLK is used as the board clock.

- INIT-/ is received and buffered to become the board reset signal RESET-/.

- Two 24-bit differential receiver and filter networks receive the 24-bit frequency tune words L0100-123 and LO200-223 from the RDC.

- Strobe RDLO1-/ enables the lower 16 bits of tune word L01 onto bus 2. Strobe RDLO2-/ enables the lower 16 bits of tune word L02 onto bus 2. Strobe RDLO3-/ enables the upper 8 bits of tune word L01 and the upper 8 bits of tune word L02 onto bus 2.

- (2) TSLO read strobe, write strobe and acknowledge generation:

- Bus 2 address lines A01-03B2 and LO ENABLE are used to generate the read and write strobes. LO ENABLE and the address signals are fed into a decoder which generates read strobes RDLO01-03-/ and RDRF1-3-/ and write strobes WL01-02-/ and LOAD COMMAND. LOAD COMMAND and RDRF1-3-/ are outputs used by the TSRF (A9) module.

- The read and write strobes are fed into an acknowledge generator which outputs the acknowledge signal XACKB2-/.

- FSTB1 and FSTB2 are applied to the latch and buffer via the differential receiver. The signals are written into the latch by WRITE ENABLE. The latch outputs LD1-/ and LD2-/ are buffered and applied to the address generators. The WRITE ENABLE output from the latch and buffer is applied to the decoder. Write commands (WLO1-02-/) from the decoder are controlled by WRITE ENABLE. Read commands (RDRF1-3-/ and RDLO1-3-/) are controlled by READ ENABLE.

TSLO (AS) BLOCK DIAGRAM

- (3) TSLO lock status.

- Frequency strobe signals FSTB1 and FSTB2 from the RDC are applied to differential receivers, then buffered and latched to form load signals LD1-/ and LD2-. The load signals are used to pre-load the address generators (ADD GEN 1 and ADD GEN 2). The address generators are incremented by a 64 psec signal generated from an 8-bit free running counter clocked by CLKI. The outputs of the address generators are used as inputs to two 512 x 8 ROM containing lock status data. Data bits D00-02B2 are clocked into latches by write strobes WLO1-/ and WL02-/. The output of the latches is used as an input to two 8:1 decoders selecting 1 bit from each ROM. The status bits from the decoders are latched and sent to differential drivers. The outputs of the differential drivers are the lock status signals LK1 and LK2.

TSLO (AS) BLOCK DIAGRAM

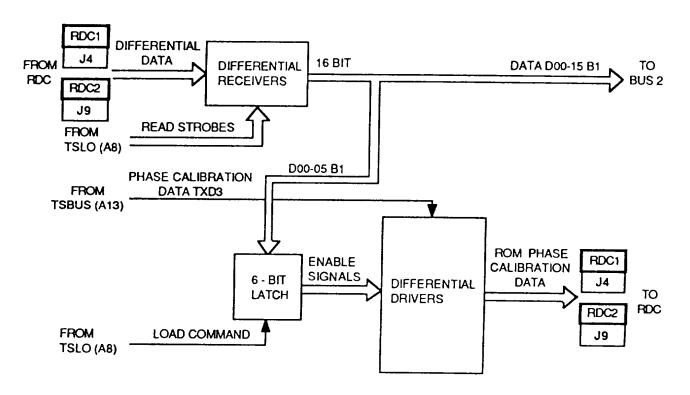

h. TSRF (A9). Refer to the TSRF (A9) block diagram. The TSRF simulates outputs from RFA to RDC1 and RDC2.

TSRF (A9) accepts:

- Data from RDC in the form of three 16-bit differential data words

- READ STROBES and LOAD COMMAND from TSLO (As)

- PHASE CALIBRATION DATA TXD3 from TSBUS (A13)

TSRF (A9) outputs:

- 16-bit data (D00-15B1) to bus 2

- Simulated RFA ROM PHASE CALIBRATION data to the RDC as six differential signals

- which represent low-band (LB), mid-band (MB), and high-band (HB) phase-correction data

(1) Control data:

- The TSRF (A9) circuit card consists of twelve differential receivers arranged to receive three 16-bit data words.

- The output of each 16-bit word may be enabled onto bus 2 by one of three READ STROBES.

- Data word 1 contains control signals for IFS A and IFP A Data word 2 contains control signals for IFS B and IFP B. Data word 3 contains control signals for RF antennas A and B.

- (2) Phase calibration data:

- Data bits D00-05B1 are written into a 6-bit latch on load signal LOAD COMMAND. The latch output, ENABLE SIGNALS, is used to enable one of six differential drivers. When enabled, a driver passes input data as differential ROM PHASE CALIBRATION DATA for one of the selected RF antenna bands.

AQL-5630-05B

1-31

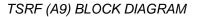

j. TSIFP (A7). Refer to the overall TSIFP (A7) block diagram. The software-controlled TSIFP (A7) functions as directed by DBP (A14) running operating system and diagnostic programs. In conjunction with TSD/A (A5) and TSD/A (A6), TSIFP (A7) tests the IFP interface to the IU by generating simulated IFP 1,0 data and control signals. Data flow between the IU, TSIFP (A7), TSD/A (AS), and TSD/A (A6) is entirely dependent upon operating system programs and diagnostic/test programs as executed by DBP (A13) with interaction of operator terminal and associated peripheral devices. Refer to the following seven paragraphs for further information. The major elements of the TSIFP (A7) are divided into seven groups. Refer to TSIFP (A7) sections one through seven.

TSIFP (A7) OVERALL BLOCK DIAGRAM

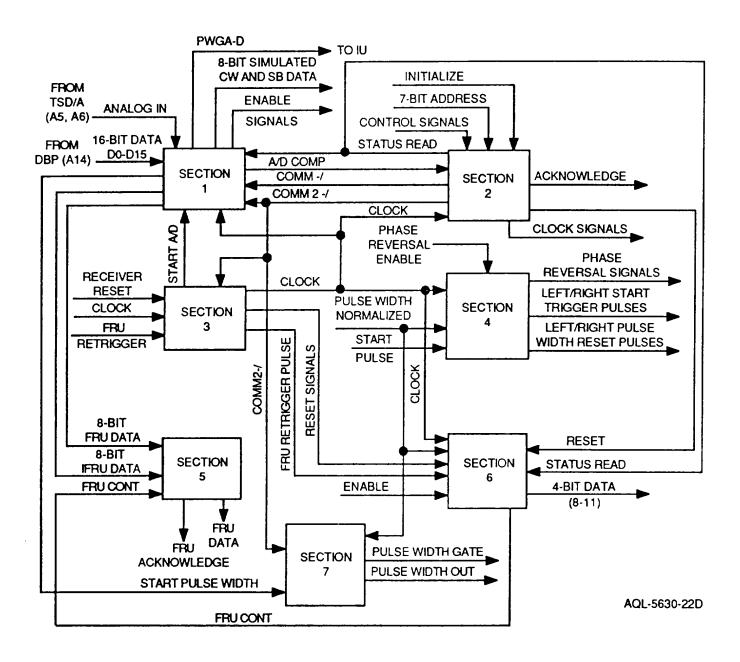

j. TSIFP (A7) Section One. Refer to the TSIFP (A7) block diagram, section one. TSIFP (A7) section one inputs data to and outputs data from the board.

TSIFP (A7) section one accepts:

- 16-bit data (DO-15B2) from DBP (A14) via bus 2

- ANALOG IN from TSD/A (A5) or TSD/A (A6)

- Control signal (STATUS READ) from TSIFP (A7) section two

- Control signal (START AID) from TSIFP (A7) section three

- Clock command signals (COMM-/, COMM2-, and AD96CK-/) from TSIFP (A7) section two

- CLOCK from TSIFP (A7) section three

TSIFP (A7) section one outputs:

- PHASE REVERSAL ENABLE to TSIFP (A7) section seven

- PWGA-D to IU

- A/D COMP to TSIFP (A7) section three

- START PUILSE WIDTH to TSIFP (A7) section seven

- ADDRESS SELECT to TSD/A (A5, A6)

- 8-BIT SIMULATED CW DATA (differential) to IU

- 8-BIT SIMULATED SB DATA (differential) to IU

- 8-bit FRU data to TSIFP (A7) section five

- 8-bit IFRU data to TSIFP (A7) section five

- 16-bit data to DBP (A14) via bus 2

- ANALOG ENABLE and TEST to TSD/A (A5, A6)

- PWGA-D to IU

- A/D COMP to TSIFP (A7) section three

TSIFP (A7) section one signal processing:

- (1) The 16-bit transceiver is used to handle 16-bit parallel data between TSIFP (A7) and DBP(A14).

- (2) Data is written into 16-bit latch (1), which outputs START PULSE WIDTH, PHASE REVERSAL ENABLE, DPWA-D, TEST, and 8-BIT SIMULATED CW AND SB DATA.

- (3) 8-BIT SIMULATED CW AND SB DATA is sent through the differential drivers to the IU.

- (4) Data is written into the 8-bit latch, which outputs ADDRESS SELECT to TSD/A (A5, A6) and ADDRESS SELECT CONTROL and ENABLE to the open collector drivers which output ANALOG ENABLE signals to TSD/A (A5) and TSD/A (A6).

- (5) Data is written into 16-bit latch (2), which outputs 8-BIT FRU DATA and 8-BIT IFRU DATA to TSIFP (A7) section five.

- (6) ANALOG OUT from TSD/A (A5) or TSD/A (A6) is sent to the TSIFP (A7) as ANALOG IN. ANALOG IN is applied to the signal conditioning circuit and then to the A/D converter.

- (7) The output of the A/D converter, 8-BIT DATA, is strobed through the 8-bit buffer to the 16-bit transceiver, where it is sent to DBP (A14) via bus 2.

- (8) CLOCK is applied to the divide-by-two circuitry and output as 2 MHZ to the AID converter. A/D COMP is produced when the A/D converter is finished with its conversion and 8-BIT DATA is passed to the 8-bit buffer.

- (9) Four bits from the 16-bit latch (DPWA-D) are sent to a TTL to MECL (Motorola emitter coupled logic) converter and output as PWGA-D to the IU.

TSIFP (A7) BLOCK DIAGRAM, SECTION ONE

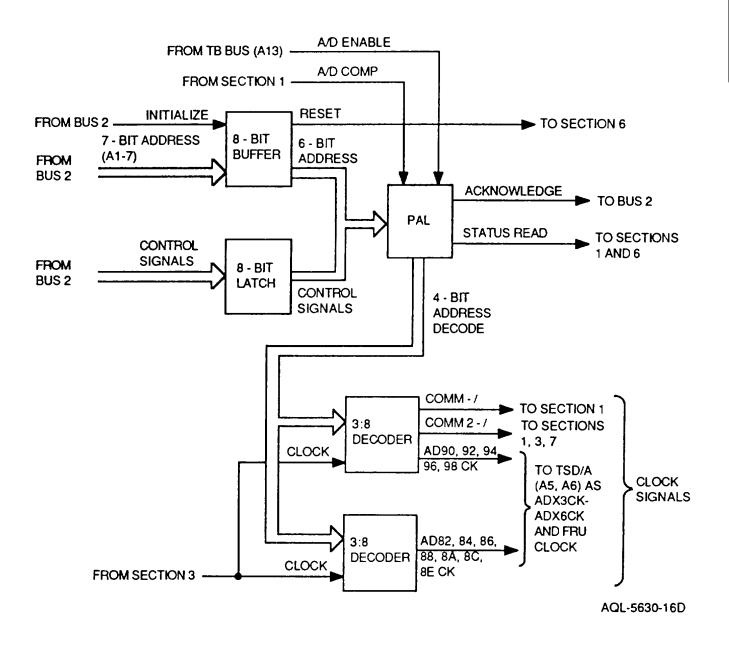

k. <u>TSIFP (A7) Section Two</u>. Refer to the TSIFP (A7) block diagram, section two. TSIFP (A7) section two generates signals for the D/A circuit cards (A5, A6) and control signals used elsewhere in the TSIFP.

TSIFP (A7) section two accepts:

- INITIALIZE from bus 2

- 7-BIT ADDRESS (A1-7) from bus 2

- CONTROL SIGNALS from bus 2

- CLOCK and A/D COMP from TSIFP (A7) section three

- A/D ENABLE from TSBUS (A13)

- A/D COMP from TSIFP (A7) section three

TSIFP (A7) section two outputs:

- RESET to TSIFP (A7) section six

- ACKNOWLEDGE to bus 2

- STATUS READ to TSIFP (A7) sections one and six

- Clock signals to TSD/A (A5), TSD/A (A6), and TSIFP (A7) sections one, three, and seven

- TSIFP (A7) section two signal processing:

- (1) CONTROL SIGNALS are latched into the 8-bit latch and used as inputs into the PAL.

- (2) The second input to the PAL, 6-BIT ADDRESS, is input via the 8-bit buffer.

- (3) The PAL generates ACKNOWLEDGE, STATUS READ, and 4-BIT ADDRESS DECODE.

- (4) ACKNOWLEDGE is sent to DBP (A14).

- (5) A/D ENABLE asserts at the beginning of the A/D conversion and A/D COMP asserts at the end of the A/D conversion to provide intelligence for STATUS READ.

- (6) STATUS READ is sent to a buffer and a receiver in TSIFP (A7) section one, and a PAL in TSIFP (A7) section six.

- (7) 4-BIT ADDRESS DECODE is an input to the 3:8 decoders which generate clock signals COMM-/, COMM2-/, AD90, 92, 94, 96, 98 CK, and AD82, 84, 86, 88, 8A, 8C, 8E CK for TSD/A (A5) and TSD/A (A6). (These clock signals are named ADX3CK-ADX6CK and FRU CLOCK when they reach the TSD/A cards.)

TSIFP (A7) BLOCK DIAGRAM, SECTION TWO

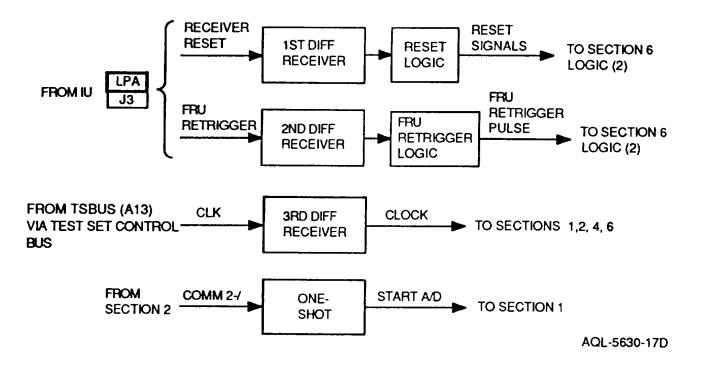

I. TSIFP (A7) Section Three. Refer to the TSIFP (A7) block diagram, section three. TSIFP (A7) section three generates control signals for use in other TSIFP sections.

TSIFP (A7) section three accepts:

- RECEIVER RESET from IU

- FRU RETRIGGER from IU

- CLK from TSBUS (A13) via test set control bus

- COMM2-from TSIFP (A7) section two

TSIFP (A7) section three outputs:

- RESET SIGNAIS to TSIFP (A7) section six

- FRU RETRIGGER PULSE to TSIFP (A7) section six

- CLOCK to TSIFP (A7) sections one, two, four, and six

- START A/D to TSIFP (A7) section one

TSIFP (A7) section three signal processing:

- (1) RECEIVER RESET is applied to the reset logic circuit via the first differential receiver. The output of the reset logic circuit is RESET SIGNALS, used in TSIFP (A7) section 6.

- (2) FRU RETRIGGER is applied to the FRU retrigger logic circuits via the second differential receiver. The signal is combined in the retrigger logic circuits to form FRU RETRIGGER PULSE, which is sent to TSIFP (A7) section six.

- (3) CLK is applied to the third differential receiver, which generates CLOCK for use as TSIFP (A7) clocks in sections two, four, and six.

- (4) When COMM2-/ is applied to the one-shot, it generates START A/D for the AD converter in TSIFP (A7) section one.

TSIFP (A7) BLOCK DIAGRAM, SECTION THREE

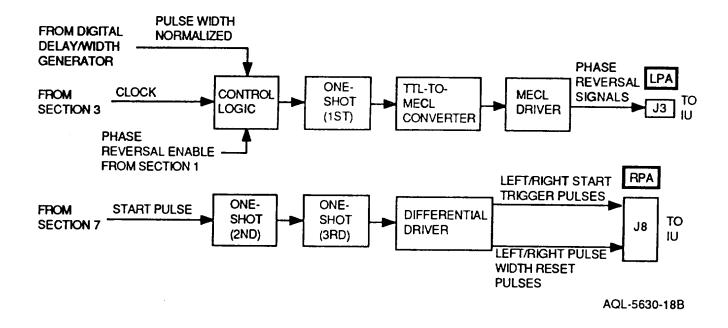

m. <u>TSIFP (A7) Section Four</u>. Refer to the TSIFP (A7) block diagram, section four. TSIFP (A7) section four generates trigger and reset pulses for use in the IU.

TSIFP (A7) section four accepts:

- PULSE WIDTH NORMALIZED from the digital delay/width generator

- CLOCK from TSIFP (A7) section three

- PHASE REVERSAL ENABLE from TSIFP (A7) section one

- START PULSE from TSIFP (A7) section seven

TSIFP (A7) section four outputs:

- PHASE REVERSAL SIGNALS to the IU

- LEFT/RIGHT START TRIGGER PULSES to the IU

- LEFT/RIGHT PULSE WIDTH RESET PULSES to the IU

TSIFP (A7) section four signal processing:

- (1) Using PULSE WIDTH NORMALIZED, CLOCK, and PHASE REVERSAL ENABLE, the control logic, the first one-shot, the TTL to-MECL converter, and the MECL driver provide PHASE-REVERSAL SIGNALS to the IU.

- (2) Using START PULSE, the second and third one-shots and the differential driver provide LEFT/RIGHT PULSE WIDTH RESET PULSES and LEFT/RIGHT START TRIGGER PULSES to the IU.

TSIFP (A7) BLOCK DIAGRAM, SECTION FOUR

1-41

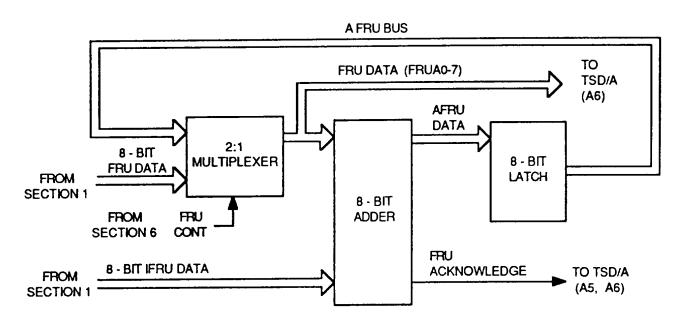

n. <u>TSIFP (A7) Section Five</u>. Refer to the TSIFP (A7) block diagram, section five. TSIFP (A7) section five generates various FRU signals for the TSD/A cards (A5, A6).

TSIFP (A7) section five accepts:

- 8-BIT FRU DATA from TSIFP (A7) section one

- 8-BIT IFRU DATA from TSIFP (A7) section one

- FRU CONT from TSIFP (A7) section six

TSIFP (A7) section five outputs:

- FRU ACKNOWLEDGE to TSD/A (A5) and TSD/A (A6)

- FRU DATA (FRUAO-7) to TSD/A (A6)

TSIFP (A7) section five signal processing:

- (1) FRU DATA and data from the AFRU bus are applied to the 2:1 multiplexer. Depending upon the state of FRU CONT, one or the other is passed to the 8-bit adder.

- (2) This data is then added to 8-BIT IFRU data and latched into the 8-bit latch as AFRU data.

- (3) The output of the multiplexer is also passed to TSD/A (A6) to be converted to an analog signal and sent to the IU.

- (4) FRU ACKNOWLEDGE clocks data into latches on TSD/A (A5) and TSD/A (A6).

AQL-5630-19D

TSIFP (A7) BLOCK DIAGRAM, SECTION FIVE

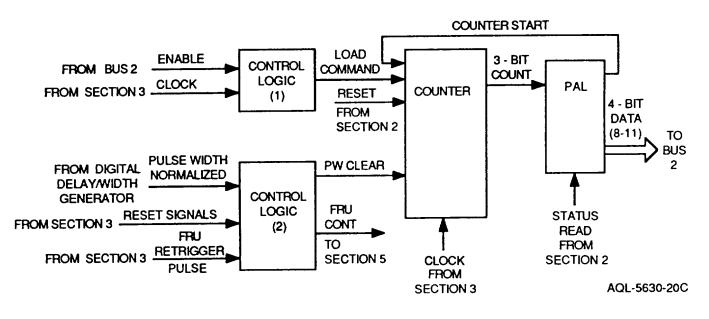

o. <u>TSIFP (A7) Section Six</u>. Refer to the TSIFP (A7) block diagram, section six. TSIFP (A7) section six produces a 4-bit data word for bus 2 and a control signal for the DBP.

TSIFP (A7) section six accepts:

- STATUS READ from TSIFP (A7) section two

- RESET from TSIFP (A7) section two

- ENABLE from bus 2

- CLOCK from TSIFP (A7) section three

- PUI-E WIDTH NORMALIZED from the digital delay/width generator

- FRU RETRIGGER PULSE and RESET SIGNALS from TSIFP (A7) section three

TSIFP (A7) section six outputs:

- 4-BIT DATA (8-11) to bus 2

- FRU CONT to TSIFP (A7) section five

TSIFP (A7) section six signal processing:

- (1) Using the inputs ENABLE and CLOCK, control logic circuit (1) provides LOAD COMMAND for the counter. The counter is pre-loaded and can be enabled to either count up or count down.

- (2) Using the inputs PULSE WIDTH NORMALIZED, RESET SIGNALS, and FRU RETRIGGER PULSE, control logic circuit (2) generates the counter control signal PW CLEAR. Control logic circuit (2) also produces FRU CONT, used in TSIFP (A7) section five to control a 2:1 multiplexer.

- (3) The PAL is used to generate COUNTER START and outputs the count onto data lines 8 to 11 of bus 2.

TSIFP (A7) BLOCK DIAGRAM, SECTION SIX

1-45

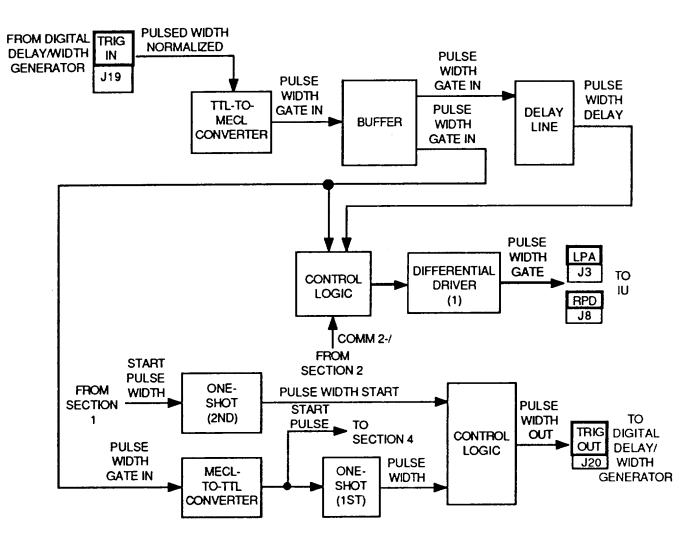

p. <u>TSIFP (A7) Section Seven</u>. Refer to the TSIFP (A7) block diagram, section seven. TSIFP (A7) section seven produces pulse width signals to the IU and the digital delay/width generator.

TSIFP (A7) section seven accepts:

- PULSE WIDTH NORMALIZED from the digital delay/width generator

- START PULSE WIDTH from TSIFP (A7) section one

- COMM2-/ from TSIFP (A7) section two

TSIFP (A7) section seven outputs:

- PULSE WIDTH GATE to IU

- PULSE WIDTH OUT to digital delay/width generator

- START PULSE to TSIFP (A7) section four

TSIFP (A7) section seven signal processing:

- (1) PULSE WIDTH NORMALIZED from the test generator is converted to MECL levels (PULSE WIDTH GATE IN) and buffered into two identical pulse width signals.

- (2) One of the pulse width signals goes directly to the control logic circuit, and the other goes through a delay line before going to the control logic circuit.

- (3) The control logic circuit selects one of the two signals and outputs it through a differential driver as PULSE WIDTH GATE.

- (4) The non-delayed pulse is converted back to a TTIL level used to trigger the first one-shot and is also sent to TSIFP (A7) section four as START PULSE.

- (5) The output of the first one-shot, PULSE WIDTH, is applied to another control logic circuit.

- (6) The second one-shot is used as an input to the control logic circuit to allow PULSE WIDTH from the first one-shot to pass through the control logic circuit and become PULSE WIDTH OUT.

AQL-5630-21B

TSIFP (A7) BLOCK DIAGRAM, SECTION SEVEN

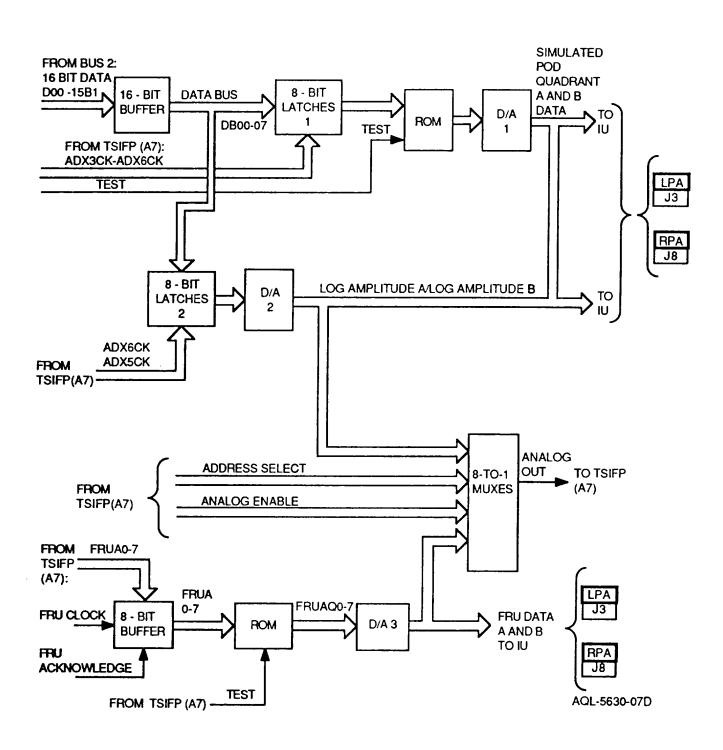

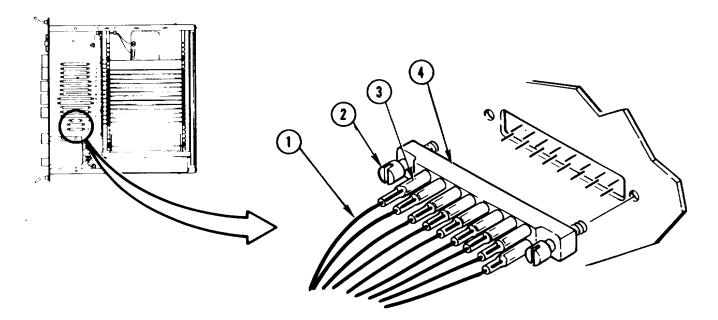

q. TSD/A (A5 and A6). TSD/A (AS and A6) function together to test IFP analog interface to IU by generating simulated pod quadrant A and B analog data.

#### NOTE

#### The following is representative of either TSD/A (A5) or TSD/A (A6).

TSD/A (A5 and A6) accept:

- 16-bit data from bus 2

- Latch clock signals ADX3 CK ADX6 CK from TSIFP (A7)

- TEST from TSIFP (A7)

- ADDRESS SELECT from TSIFP (A7)

- ANALOG ENABLE from TSIFP (A7)

- FRUAO-7 from TSIFP (A7) (accepted by A6 only)

- FRU ACKNOWLEDGE and FRU CLOCK from TSIFP (A7)

## TSD/A (A5 and A6) output:

- Left pod quadrant A simulated analog data to IU

- Left pod quadrant B simulated analog data to IU

- Right pod quadrant A simulated analog data to IU

- Right pod quadrant B simulated analog data to IU

- FRU DATA A and FRU DATA B to IU

- ANALOG OUT to TSIFP (A7)

- (1) 16-bit data is buffered and strobed into 8-bit latches (1, 2) by latch clock signals (ADX3 CK- ADX6 CK) from TSIFP (A7).

- (2) FRU data (FRUAO-7) is clocked into the 8-bit buffer by FRU ACKNOWLEDGE and FRU CLOCK This data and the test input line signal (TEST) address ROM whose digital output represents RFA pod data. ROM digital data outputs are converted by DIA converters (1, 3) to 16 analog signals representing:

- RFA df in-phase (I) data

- RFA df quadrature-phase (Q) data

- Fine-frequency FRU data

- (3) These 16 ROM-derived analog signals are sent to the IU and to the 8-to-1 multiplexers.

- (4) The upper data bits are latched into an 8-bit latch (2) and are directly converted by D/A converters (2) to analog signals, LOG AMPLITUDE A and LOG AMPLITUDE B. These analog signals are sent to the IU and to the 8-to-1 multiplexers.

- (5) As a group, these signals represent simulated RFA pod quadrant A and B analog data.

- (6) Any of these analog signals may be selected by ANALOG ENABLE and ADDRESS SELECT from TSIFP (A7). The selected signal is output through one of three 8-to-1 multiplexers as ANALOG OUT to TSIFP (A7).

TSD/A (A5 AND A6) BLOCK DIAGRAM

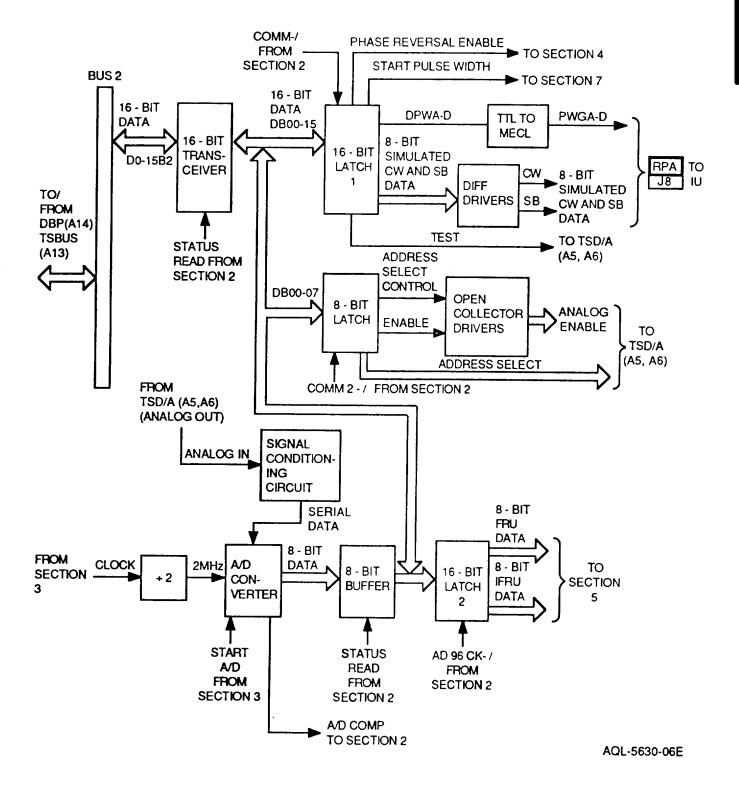

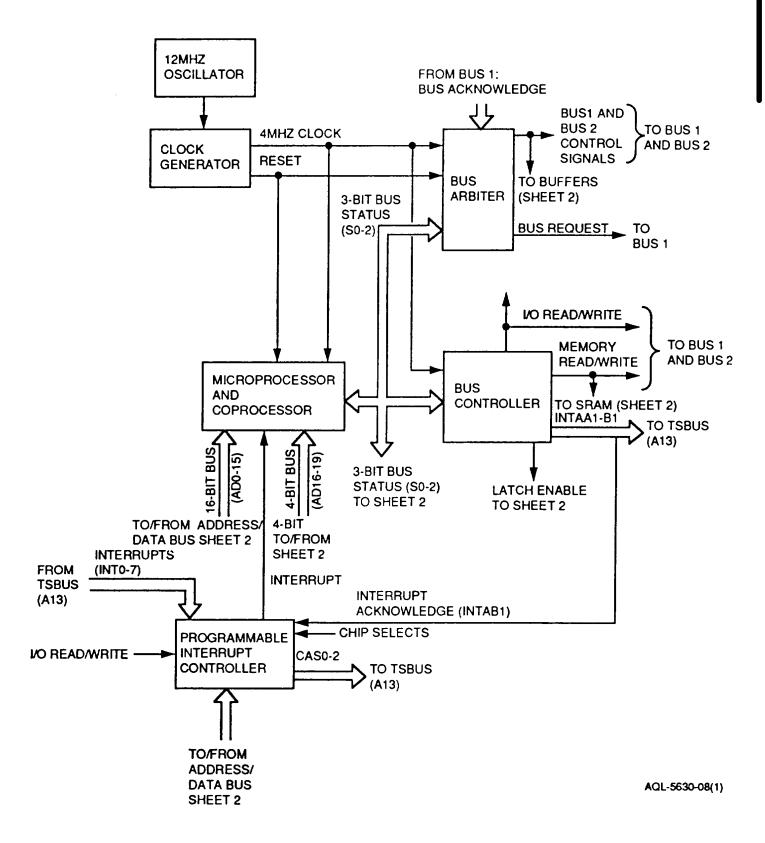

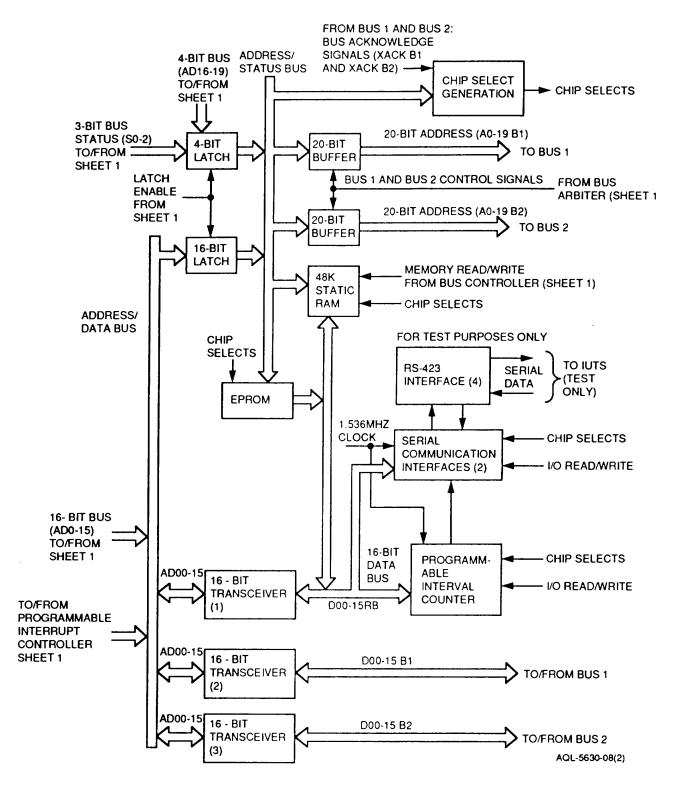

- r. <u>DBP (A14)</u>. Refer to the DBP (A14) block diagram. DBP (A14) controls data flow between bus 1 and bus 2. A microprocessor controls data flow and memory manipulation, while a coprocessor computes numerics.

- (1) The 12 MHz oscillator input to clock generator produces 4 MHZ CLOCK to the microprocessor, coprocessor, bus arbiter, and bus controller. RESET from the clock generator resets the microprocessor, coprocessor, and bus arbiter. 3-BIT BUS STATUS (SO-2) from the microprocessor is applied to the bus arbiter, bus controller, and 4bit latch (sheet 2). 3-BIT BUS STATUS causes the bus arbiter to generate BUS 1 AND BUS 2 CONTROL SIGNALS. 3-BIT BUS STATUS also causes the bus controller to generate I/O READ/WRITE signals and MEMORY READ/WRITE signals. MEMORY READ/WRITE accesses SRAM when no other bus activity is present. I/O READ/WRITE tells an input or output device to read from or write to data bus. In addition, the bus controller generates INTAA1-B1 containing decoded interrupt information, which is sent to the programmable interrupt controller on the TSBUS (A13) card. INTAB1 is also sent to the programmable interrupt controller as an interrupt acknowledge.

- (2) When INTERRUTI'S (INTO-7) are asserted, the programmable interrupt controller sends INTERRUPT to the microprocessor, which executes software to handle the interrupt. The interrupt controller has an 8-bit bi-directional data bus to the microprocessor address/data bus for address and data flow.

- (3) The microprocessor has a 4-bit address/status bus (AD16-19) and a 16-bit bi-directional address/data bus (AD0-15) for address, status, and data flow. The address/status bus is the four most significant address lines for memory operations. During memory operations, status information is available on these lines.

- (4) When a DBP card is ready to use the bus, BUS REQUEST is sent to bus 1. When TSBUS (A13) grants access to the bus, it sends BUS ACKNOWLEDGE to DBP (A14).

- (5) Decoded cascade information is sent to TSBUS (A13) on CASO-2.

- (6) Address bits ADO-19 from the microprocessor are applied to the chip select generation circuitry via the 4 and 16-bit buses and latches. The chip select generation circuitry generates device-access chip selects for the programmable interrupt controller, serial communication interfaces, programmable interval counter (PIC), SRAM, EPROM, bus 1, and bus 2.

- (7) Address data from the 4-bit and 16-bit latches are controlled by LATCH ENABLE from the bus controller. The 20-bit address bus also addresses a 48K x 8 SRAM and a 32K x 8 EPROM. The 16-bit address/data bus allows 16-bit data transfer between the microprocessor, bus 1, and bus 2. 16-bit data (DO0-15BI1B2) is transmitted or received by the 16-bit transceivers (2 and 3). Address data from the address/status bus are buffered by the 20-bit buffers, which are enabled by control signals from the bus arbiter.

DBP (A14) BLOCK DIAGRAM

(8) The 16-bit transceiver (1) transfers data (D00-15RB) between the microprocessor and the RS-423 serial communication interfaces. The serial communication interfaces provide noise-free data transfer for diagnostic program load and cathode ray tube (CRT) test. The PIC (used as a baud rate generator) sets serial interface data transfer rates. The PIC and serial interfaces receive 1.536 MHZ CLOCK from the 1.536 MHz oscillator (part of the DBP). Serial interface data transfer is set at 153.6 KHz. Transmit and receive control signals are software-controlled interrupts from each serial interface. The 16-bit address/data bus allows address and data flow between each serial interface, the PIG, SRAM, EPROM, the microprocessor address/data bus, and the programmable interrupt controller (sheet 1). The EPROM contains software that controls DBP (A14).

DBP (A14) BLOCK DIAGRAM

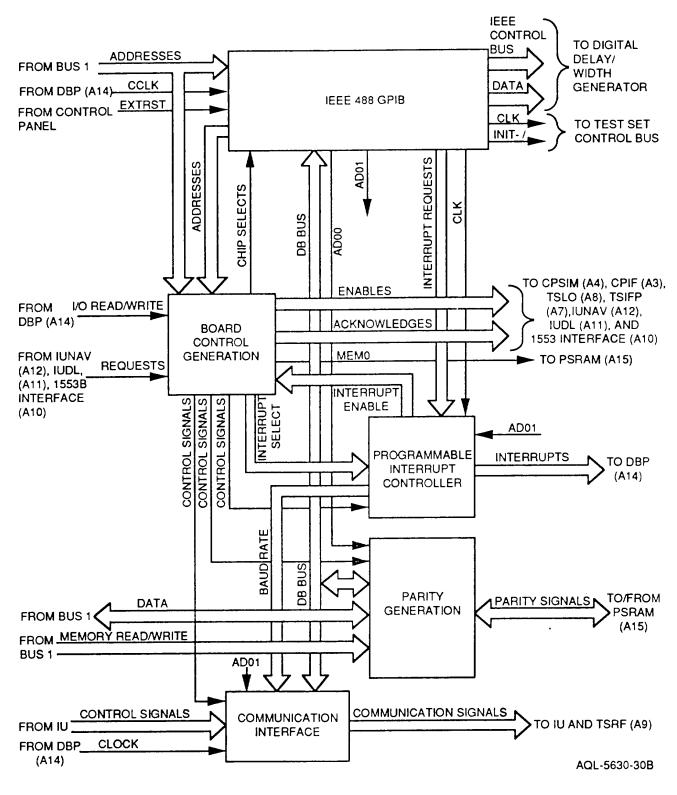

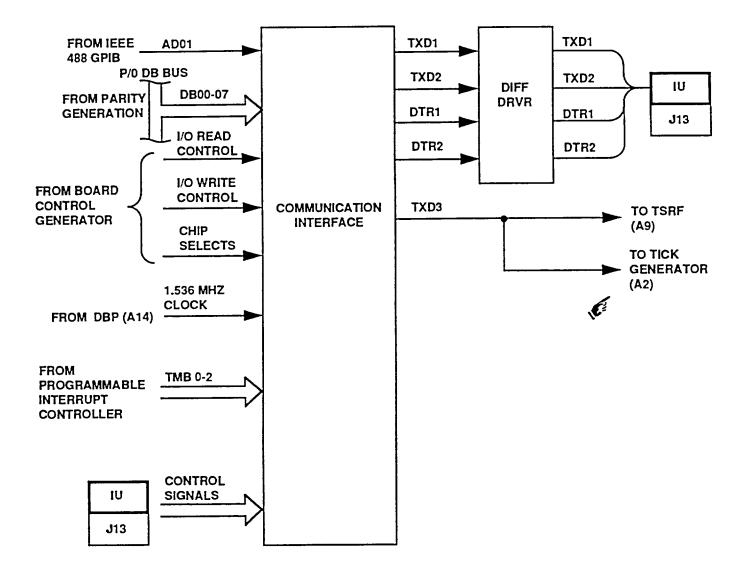

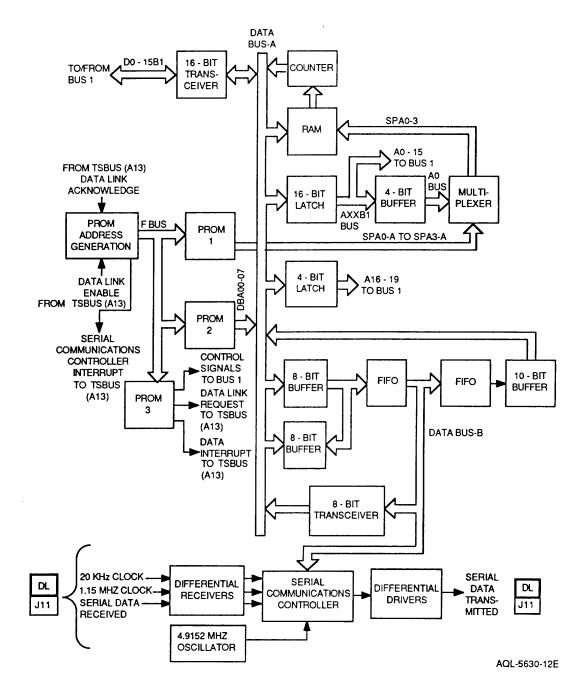

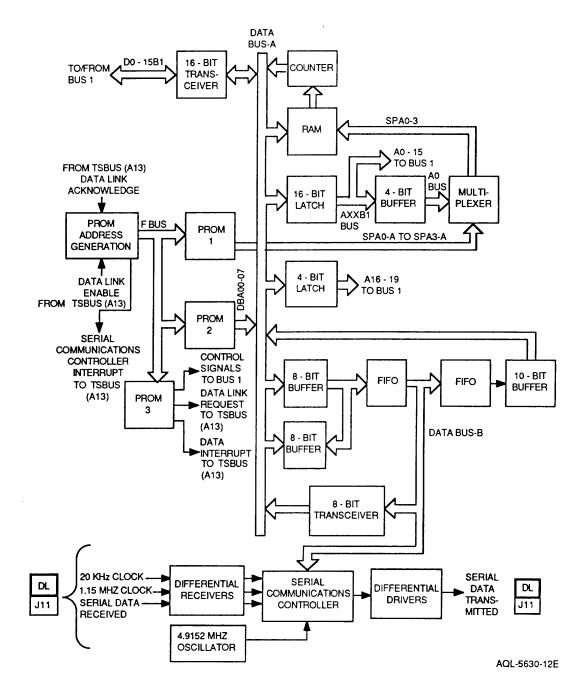

<u>a</u>. <u>TSBUS (A13)</u>. Refer to the TSBUS (A13) block diagram. The TSBUS provides a general purpose interface bus (GPIB) to communicate with digital delay/width generator and provides spare RS-232C channels, interrupts, and timers. The TSBUS (A13) is divided into five functional areas:

IEEE 488 GPIB Board Control Generation Programmable Interrupt Controller (PIC) Parity Generation Communication Interface

Refer to those areas for further information.

TSBUS (A13) BLOCK DIAGRAM

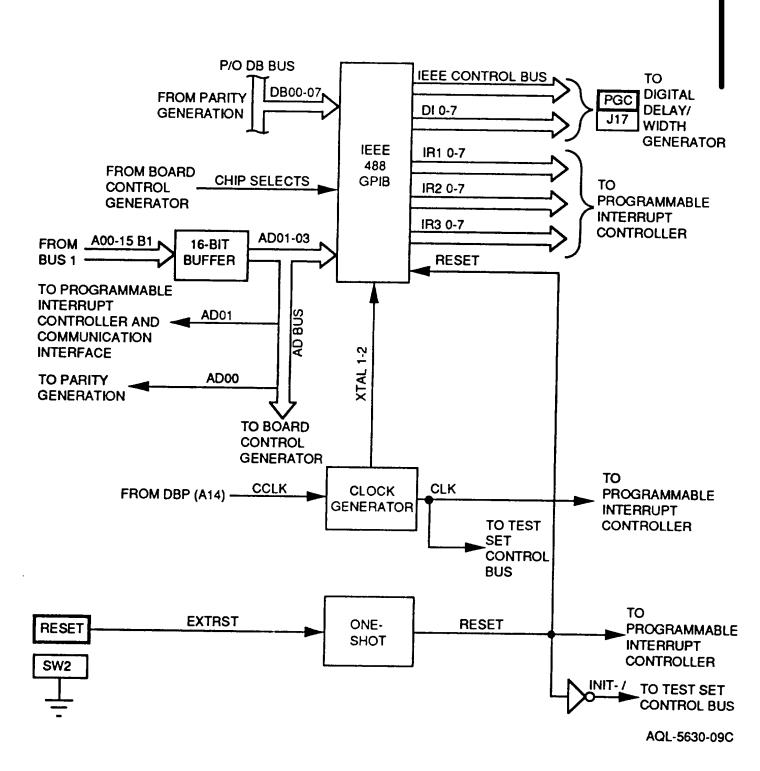

t. <u>IEEE 488 GPIB</u>. Refer to the IEEE 488 GPIB block diagram. The IEEE 488 consists of a 4 chip set that implements the IEEE-STD-488 digital interface GPIB.

The IEEE 488 GPIB section accepts:

- 8-bit data (DB00-07) from parity generation

- CHIP SELECTS from the board control generator

- 16-bit address lines (A00-15B1) from bus 1

- Clock signal CCLK from DBP (A14)

- External reset signal EXTRST from front panel

The IEEE 488 GPIB section outputs:

- IEEE CONTROL BUS to digital delay/ width generator

- 8-bit data (DI0-7) to digital delay/width generator

- Interrupt signals (IR10-7, IR20-7, IR30-7) to the PIC section

- Clock signal CLK to test set control bus and the PIC section

- RESET to the PIC section

- INIT-/ to test set control bus

- AD010 to the PIC and communication interface sections

- AD00 to the parity generation section

- (1) When the operator presses SW2 (RESET) button on the test set front panel, the signal EXTRST is applied to a one-shot. The output of the one-shot, RESET, is used as a reset signal on and off the board. RESET is inverted to become INIT-/, and applied to the test set control bus.

- (2) Clock signal CCLK from DBP (A14) is applied to the clock generator and is output as CLK. CLK is used as a board clock, and is also sent to the test set bus. The clock generator also outputs XTAL 1 and 2 which are used by the IEEE 488 GPIB circuitry.

- (3) Address lines A00-15B1 from bus 1 are applied to a 16-bit buffer and output on the AD bus. Address bits AD01-03 are applied to the IEEE 488 GPIB circuitry, AD01 is applied to the PIC and communication interface circuitry, and ADOO is applied to the parity generation circuitry.

- (4) Data bits DB00-07 from the DB bus are applied to the IEEE 488 GPIB circuitry and output as DIO-7 for use by the digital delay/width generator.

- (5) The remainder of the output signals, IEEE CONTROL BUS, IR10-7, IR20-7, and IR30-7, are generated by the interaction of data bits, address bits, and clock signals.

IEEE 488 GPIB BLOCK DIAGRAM

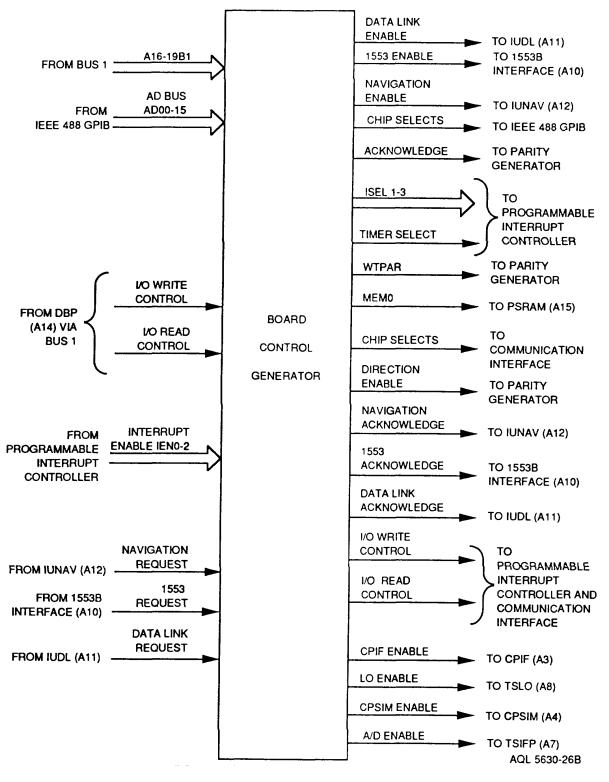

<u>u</u>. <u>Board Control Generation</u>. Refer to the board control generation block diagram. The board control generation section consists of a 16-bit buffer, a 6-bit latch, and five PALs. Its purpose is to create control and enable signals for use on the TSBUS (A13) as well as other cards.

The board control generation section accepts:

- 1553 REQUEST from 1553B interface (A10)

- Address bits A00-15 from the IEEE 488 GPIB section

- Address bits A16-19B1 from bus 1

- DATA LINK REQUEST from IUDL (All)

- /O WRITE CONTROL and I/O READ CONTROL from DBP (A14)

- INTERRUPT ENABLE IEN0-2 from the PIC section

- NAVIGATION REQUEST from IUNAV (A12)

The board control generation section outputs:

- 1553 ACKNOWLEDGE from 1553B interface (A10)

- 1553 ENABLE to 1553B interface (A10)

- A/D ENABLE to TSIFP (A7)

- ACKNOWLEDGE to the parity generation section

- CHIP SELECTS to the IEEE 488 GPIB and communication interface sections

- CPIF ENABLE to CPIF (A3)

- CPSIM ENABLE to CPSIM (A4)

- DATA LINK ACKNOWLEDGE from IUDL (All)

- DATA LINK ENABLE to IUDL (AII)

- DIRECTION ENABLE to the parity generation section

- I/O WRITE CONTROL and 10 READ CONTROL to the PIC and communication interface sections

- LO ENABLE to TSLO (A8)

- MEMO to PSRAM (A15)

- NAVIGATION ENABLE and NAVIGATION ACKNOWLEDGE to IUNAV (A12)

- TIMER SELECT and interrupt signals ISEL1-3 to the PIC section

- Write parity signal (WTPAR) to the parity generation section

Based upon address inputs, read/write controls, interrupts, and external requests, the board control generator produces the outputs shown.

BOARD CONTROL GENERATION BLOCK DIAGRAM

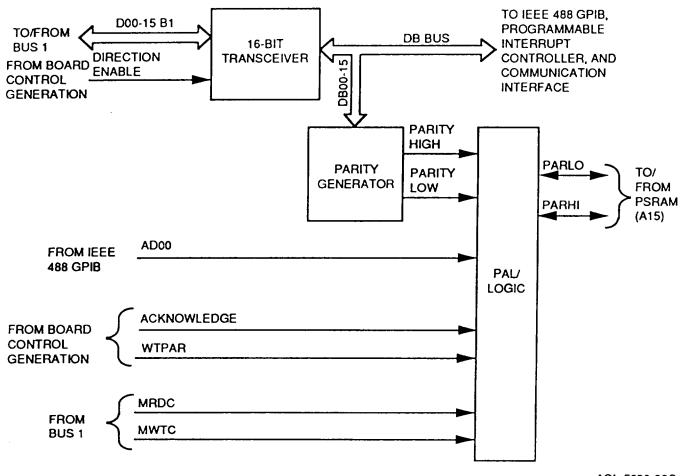

<u>y</u>. <u>Parity Generation</u>. Refer to the parity generation block diagram. The parity generation circuit consists of a 16-bit transceiver, a parity generator, a PAL, and a logic block. The parity generation circuitry outputs the parity of the upper and lower data bytes.

The parity generation section accepts:

- Data bits D00-15B1 from bus 1

- DIRECTION ENABLE from the board control generation section

- Address line ADOO from the IEEE 488 GPIB section

- ACKNOWLEDGE and WTPAR from the board control generation section

- Memory read/write commands MRDC and MWTC from bus 1

- Parity signals PARLO and PARHI from PSRAM (A15)

The parity generation section outputs:

- Data bits D00-15B1 to bus 1

- Data on the DB bus to the IEEE 488 GPIB, PIC, and communication interface sections

- Parity signals PARLO and PARHI to PSRAM (A15)

- (1) The 16-bit transceiver buffers data from bus 1 onto data bus DB.

- (2) The parity generator applies PARITY HIGH and PARITY LOW to the PAL.

- (3) The PAL and logic block are used to output parity information data based on the states of the address and read/write inputs.

AQL-5630-28C

PARITY GENERATION BLOCK DIAGRAM

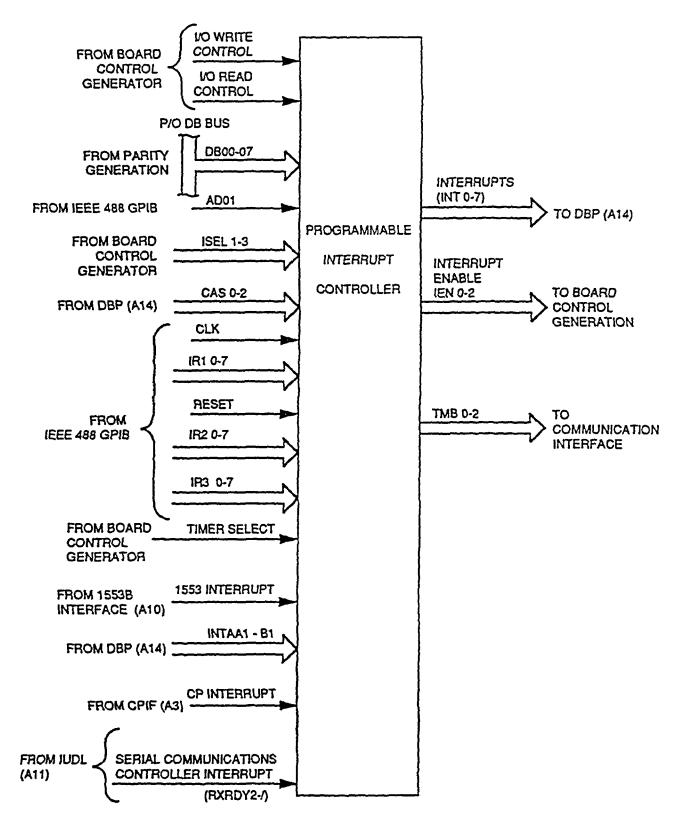

w. <u>PIC</u>. Refer to the PIC block diagram. The PIC processes interrupt requests to produce interrupts. In addition, it furnishes different baud rate signals for the communication interface.

The PIC section accepts:

- 1553 INTERRUPT from 1553B interface (A10)

- Address bit AD01 from the IEEE 488 GPIB section

- Cascade control signals CASO-2 from DBP (A14)

- CLK, IR1 0-7, RESET, IR2 0-7, and IR3 0-7 from the IEEE 488 GPIB section

- CP INTERRUPT from CPIF (A3)

- Data bits DB00-07 from the parity generation section

- I/O WRITE CONTROL, 10 READ CONTROL, and TIMER SELECT from the board

- control generator section

- INTAA1-B1 from DBP (A14)

- Interrupt select signals ISELi-3 from the board control generator section

- SERIAL COMMUNICATIONS CONTROLLER INTERRUPT (RXRDY2-/) from IUDL (A11)

The PIC section outputs:

- Baud rate signals TMBO-2 to the communication interface section

- INTERRUPT ENABLE IENO-2 to the board control generation section

- Prioritized interrupt signals (INT0-7) to DBP (A14)

- (1) The PIC section consists of three PIC, a PAL, and a programmable timer.

- (2) The PIC accepts interrupt request inputs and outputs the prioritized interrupt signal INTERRUPTS.

- (3) Based on TIMER SELECT, RESET, CLK, and address, and data inputs, the PIC section outputs baud rate signals TMBO-2.

PIC BLOCK DIAGRAM